トップQs

タイムライン

チャット

視点

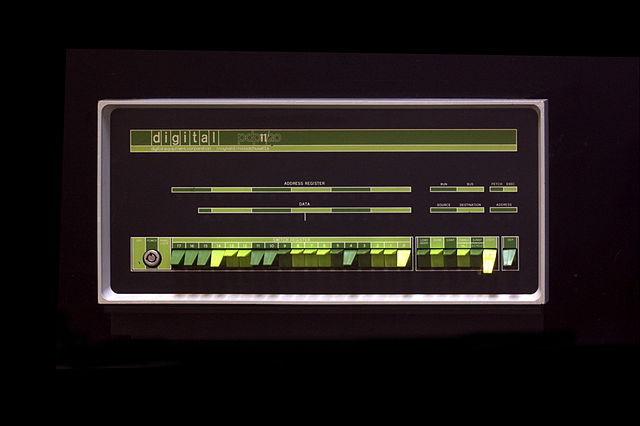

PDP-11

ディジタル・イクイップメント・コーポレーション社が1970年代から1980年代に販売した16ビットミニコンピュータシリーズ ウィキペディアから

Remove ads

PDP-11 は、ディジタル・イクイップメント・コーポレーション(DEC)が1970年代から1980年代に販売した16ビットミニコンピュータシリーズ[1][2]。PDP-11 は DECのPDPシリーズのPDP-8コンピュータの主にリアルタイムシステムの後継であるが、両シリーズは10年間以上並存した。革新的機能をいくつか持ち、従来よりもプログラミングが容易になっていた。ミッドレンジのミニコンピュータとしての後継は32ビットのVAXである。

その設計上の特徴は、モトローラのMC68000などのマイクロプロセッサの設計に影響を及ぼしている。またPDP-11上のオペレーティングシステム (OS) の設計は他のOS、例えばCP/M[3]やMS-DOS[4]の設計に影響を及ぼしている。最初の公式にUNIXと名付けられたバージョンのOSは、1970年に PDP-11/20 上で動作した。PDP-11のプログラミング上の低レベルな特徴とC言語の言語要素の類似は非常によく言われてはいるが[5]、意図的にそのように設計したわけではない[6]。たとえば、C言語の ++ や -- は、PDP-11より古い、PDP-7に実装したB言語に由来していて、ハードウェアの持っていた機能からの影響もあるだろうが、いくつかの特徴はハードウェアからというよりもトンプソンのオリジナルであろうとリッチーが書き残している(en:Increment and decrement operators#Historyを参照)。

Remove ads

歴史

DECが16ビットのPDP-11を開発するきっかけとなったのは、データゼネラルが発売したデータゼネラルNova である。Novaはワード長16ビットだが、DECが当時主力としていたPDP-8のワード長は12ビットだった。PDP-11ファミリは1970年1月に発表され、同年前半に出荷が開始された。最終的な売り上げ台数は不明であるが、販売開始後の8年間で5万台が売れたことが知られている[7]。当初はTTLのICで構成されていたが、1975年にはやや大規模な集積回路を使いCPUをワンボード化している。1979年にはマルチチップモジュール化したプロセッサ J-11 を開発。シリーズ最後の機種である PDP-11/94 と PDP-11/93 は1990年に登場した[2]。

PDP-11シリーズの特徴

要約

視点

命令セット

プログラマがPDP-11を好むのは、その直交性の高い命令セットによって命令の種類とメモリアクセス方法を分けて考えることができるからである。任意のメモリアクセス方法(アドレッシングモード)を任意の命令に使用でき、他の命令セットのように例外事項を覚えておく必要がない。例えば、多くの命令セットでは load と store があるが、PDP-11には move 命令しかなく、転送元と転送先のどちらのオペランドでもメモリもレジスタも指定可能である。また、入出力専用の命令がなく、直交性によって入力デバイスから出力デバイスへ直接データ転送することも可能である。同様に加算命令も任意のオペランド(メモリ、レジスタ、デバイス)を加える数としても計算結果の格納先としても使える。

PDP-11の命令セットアーキテクチャはB言語の慣習的構文に影響を与えていると言われているが、間違いである。レジスタインクリメントやデクリメントを行うアドレッシングモードが C言語の −−i とか i++ といった式に対応していると言われている。もし i も j もレジスタ変数なら、*(−−i) = *(j++) といった式は1個の機械語命令にコンパイルできる。デニス・リッチーは、B言語設計時にPDP-11は存在しなかったのだからこの伝説は間違いだと、明確に否定した。ただし、PDP-7の自動インクリメントセルがPDP-11のアドレッシングモードに影響している可能性はあるが、B言語そのものはPDP-7のその機能も使っていないと述べている[8]。それでも、C言語はPDP-11で実装する際にPDP-11の持つ細かい利点を活用しており、そのために後のプロセッサの設計に影響を与えた可能性はある[5]。

論理的には、アドレッシングモードと命令セットによってベースが提供されていると言える。2オペランド命令は、2つの6ビットフィールドでオペランドを指定し(3ビットがレジスタ指定で、3ビットがアドレッシングモード指定)、4ビットで命令コードを指定する。1オペランド命令は、6ビットでオペランドを指定し、10ビットで命令コードを指定する。どの命令でもオペランド指定フィールドには任意のアドレッシングモードを指定できる。8本のレジスタ(0番から7番まで)で、7本のレジスタは任意の用途に使用可能だが、6番のレジスタはいくつかの命令ではスタックポインタとして認識され、7番のレジスタはプログラムカウンタである。プログラムカウンタがプログラマから見えているという発明とアドレッシングモードの組合せで、絶対アドレス指定と相対アドレス指定が可能となった。アドレッシングモードとしては、レジスタ、即値、絶対アドレス指定、相対アドレス指定、間接アドレス指定、インデックス付きアドレッシングがあり、さらにレジスタの自動インクリメント/自動デクリメント(バイト操作なら1、ワード操作なら2)を指定できる。相対アドレス指定を使えば、機械語プログラムを位置独立にできる。

PDPエンディアン

PDP-11のエンディアンは独特であった。16ビットワードはリトルエンディアンで格納される。すなわち下位バイトがアドレスの小さいほうに格納される。32ビットワードを構成する2個の16ビットワードは、ビッグエンディアンで格納される。すなわち上位16ビットワードがアドレスの小さいほうに格納される。ここで、各16ビットワード内は前述のようにリトルエンディアンである。PDP-11が非常に一般化したため、この形式を PDPエンディアン と呼ぶことがある。

このようなミドルエンディアンにまつわる問題を「NUXI問題」と言う。これは UNIX という文字列をPDPエンディアンの順序で並べ替えたものに由来する。UNIX を他機種に移植した際、最初の起動メッセージ(しばしば、本格的な初期化に入る前、最小限のブートが完了したことを示すため、短い文字列を出力することがある)として「UNIX」ではなく「NUXI」と出力されたことがあった、と言われている。

(なお、コンピュータ中のデータの並べ方について「エンディアン」という語を使う提案は1980年になされたものであるため、初期のPDP-11についてエンディアンという語を使うのは後付けということになる)

I/O専用バスの無い構成

他の初期のコンピュータとの大きな違いとして、初期の PDP-11 は入出力専用バスを持たず、Unibus というメモリバスしか持たない。そのため入出力機器はメモリ空間にマッピングされ、特殊な I/O (入出力) 命令を必要としない。また、それぞれに割り込みベクターと割り込み優先度が設定される。プロセッサのアーキテクチャが可能にしたこの柔軟性の高いフレームワークにより、新たなバスデバイスを容易に考案でき、当初予想もしていなかった新たなハードウェアの制御も可能である。DECはこのUnibusの基本仕様を公開し、バスインタフェース回路基板のプロトタイプも提供し、ユーザーが独自のUnibus対応ハードウェアを開発できるようにしていた。

これにより、PDP-11は特注の周辺機器の制御を得意とした。アルカテル・ルーセントの前身の1つである Bell Telephone Manufacturing Company が開発したX.25ネットワーク・パケット交換機 BTMC DPS-1500 は管理システムとしてPDP-11と組み合わせて配備され、Unibus経由で直接接続されていた。

PDP-11ファミリの上位機種であるPDP-11/45やPDP-11/83システムは、この単一バス方式をやめている。その代わり、CPU筐体内だけでCPUとメモリ間の専用インタフェース回路を使用し、UnibusやQ-busはI/O専用とした。PDP-11/70ではさらに、磁気ディスク装置や磁気テープ装置とメモリ間を新たな専用バス Massbus で接続した。入出力機器はこういった構成でもメモリアドレス空間にマッピングされ続けたが、追加されたバスインタフェースの設定のためのコードを追加する必要があった。

割り込み

割り込みシステムはなるべく単純になるよう設計され、割り込みシーケンスでイベントを逃さないことを保証している。デバイスが割り込みを発生する場合、4本の優先度ラインのいずれかをアサートする。プロセッサは優先度毎の割り込みデイジーチェインに応答する(デイジーチェインはイベントを順番に並べる一種の論理回路である。最初の論理ゲートが最初に処理される。デイジーチェインはその優先度でのデバイス間の優先順位に従って設定される)。

PDP-11の設計では、この割り込み応答順はデバイスが物理的にCPUに近い順番になっている。CPUが応答すると、デバイスはそのベクターアドレスをバスに出力する。これは4バイトのメモリブロックのアドレスである。CPUはステータスレジスタとプログラムカウンタをベクターテーブルからロードする。このときのステータスレジスタの値は割り込みを不可とするようになっている。プログラムカウンタにロードされるアドレスは割り込みハンドラのスタートアドレスである。割り込みハンドラがデバイスに関する処理を行い、その過程で割り込んできたデバイスの割り込み信号を再設定する。最後に特殊なRTI (Return From Interrupt) 命令でCPUが割り込まれた箇所に戻る。戻ったところが低優先度の割り込みの処理中の場合もあり、割り込み処理の入れ子が可能である。このような処理によって割り込みを受け付けそこなうことを防いでいる。未処理の割り込みはどの段階であってもそのまま存在していて、次のサイクルで処理可能である。割り込み処理が間違って起動されるとCPUはタイムアウトとなり、特殊な擬似割り込みを発生してユーザーに対してハードウェア故障を警告する。

大量生産のための設計

PDP-11は工場でそれなりに熟練した労働者が生産できるよう設計された。あらゆる観点から個々の工程の危険性を低減している。ワイヤラッピング式のバックプレーンを使用し、プリント基板をバックプレーン上のコネクタに差し込むようになっている。バックプレーン上のコネクタ同士はワイヤラッピングで接続される。ワイヤの被覆(テフロン)を剥いだ銅線(鍍金された硬い単芯線)が端子(四角柱の角)に巻かれて食い込むことで密着する。このコネクタ部分は電話の交換機などとよく似ている。

Remove ads

LSI-11

1975年2月に登場した LSI-11 (PDP-11/03)[2] は大規模集積回路を使用した最初のPDP-11である。CPUはウェスタン・デジタル製の4個のLSIチップ(MCP-1600チップセット)で構成される。Unibusによく似たQ-busを使用。大きな違いは Q-bus のアドレスバスとデータバスが物理的には同じ線を共有していることである(マルチプレクサ)。I/Oデバイスのアドレッシングも若干異なり、22ビットの物理アドレス(Unibusでは 18ビット)とブロック転送モード(Unibusにはない)をサポートし、全体的には性能が大幅に向上している。

CPUのマイクロコードには直接RS-232Cまたはカレントループで端末と通信できるデバッガが組み込まれている。当時、そのようなデバッグには制御パネルのスイッチとランプを使うのが普通だったが、端末からコマンドを入力して指定したメモリアドレスやレジスタの内容を八進で表示できた。このデバッガはコンピュータのレジスタを調べたり、メモリや入出力機器を調べるために使われた。従って、CPUが機能しない場合でもコンピュータの内部状態を調査して修理することが可能であった。

マイクロコードには汎用ブートストラップが含まれ、DEC製の全てのディスクドライブを使用可能であった。

これら2つの発明はコンピュータが動作中は使われない。ハードディスクからブートできないとき、フロッピーからのブートを試すなど、全く起動しないときデバッガを使うといった使い方になる。これによって信頼性が向上し、全体としてコストを低減させている。

後期のQ-busベースのシステム(LSI-11/23、/73、/83 など)はDECが独自設計したチップセットを使用している。また、Unibus対応のPDP-11も後々まで継続し、CPUはQ-bus仕様のプロセッサカードを採用しつつ、アダプタでUnibusと接続してUnibus用周辺機器が使えるようにしており、中には特別なメモリバスを採用して性能向上させた機種もある。

Q-bus系機種では他にも大きな技術革新があった。例えば、PDP-11/03の派生システムではシステム全体の Power On Self Test (POST) を導入している。

PDP-11の衰退とその後

要約

視点

基本設計は非常に優れていて、最新技術も次々に取り入れていった。しかし、UnibusやQ-busのスループットがシステム性能のボトルネックとなっていき、最終的に16ビットアーキテクチャではどうがんばっても超えられない限界が見えてきた。一部機種では物理アドレス空間を拡張したが、全てのプログラムは16ビットの仮想アドレス空間(64Kバイト)に制限されていた。1980年代にメモリチップが低価格化していったが、PDP-11上のソフトウェアは大容量メモリを簡単には使えなかった。

DECがPDP-11の後継とした32ビットのVAX(Virtual Address Extension; PDP-11の仮想アドレス拡張という意味)はこのような問題に対応したが、当初はハイエンドのタイムシェアリング市場をターゲットとした。初期のVAXにはPDP-11互換モードがあり、32ビットのソフトウェアと同時に既存ソフトウェアも使用可能だった。

インテルの8086などはセグメント方式による拡張で16ビットのアドレス空間を超え、32ビット化などという大層なことをしなくても 1Mバイトまでのメモリを扱えた。これは成長過程にあった IBM PC 互換機市場には十分だったが、80286が登場する前に1Mバイトの限界が問題となってきた。80286はセグメントアドレス空間を拡大し、80386では32ビットのリニアなアドレス空間がサポートされた。

技術者がより大きなアドレス空間をサポートするアーキテクチャに移っていったころ、MC68020 (1984) やIntel 80386 (1985) のような32ビットマイクロプロセッサが登場してきた。量産効果でこれらのマイクロプロセッサは低価格化し、PDP-11はコスト面でも太刀打ちできなくなった。PDP-11ベースのパーソナルコンピュータ DEC Professional などの試みも失敗に終わった。

1994年、DECはPDP-11システムのソフトウェアの権利を Mentec Inc. (LSI-11ボードを Q-bus およびパソコン用に製造する会社)に売却した[9]。そして1997年にはPDP-11ファミリの生産を終了させた。Mentecは数年間、PDP-11アーキテクチャの新プロセッサを製造していた。

1980年代、IBM PC とその互換機が小型コンピュータ市場を席巻したが、DECはそれにうまく対抗策を打ち出せなかった。

1990年代後半にはDECを初めとするミニコンピュータ業界は壊滅し、UNIXとWindowsのサーバやワークステーションに取って代わられたのである。

しかし、2020年代後半に至ってもPDP-11を保守可能であると公表している企業があり、現役で使用されているPDP-11が存在している可能性はある。[※ 1]

2010年7月までに、VHDLで実装したPDP-11/70のIPコアがOpenCoresにて公開された。[10]ライセンスはGPL。2006年にPDP-11のマニュアルを発掘した有志の開発者により実装され、2007年までにFPGA搭載ボード(Digilent S3BOARD)上で初めて動作。2009年までにUNIX 5th Editionおよび2.11 BSDのブートに成功。

Remove ads

アーキテクチャ詳細

要約

視点

以下の情報はDECのPDP-11 Processor Handbookにある。[※ 2]

メモリ管理

PDP-11のアドレスは16ビットであり、64KBまでのアドレス範囲を指定できる。PDP-11からVAXに移行するころ、8ビットのバイトと16進表記が一般的になっていたが、PDP-11では八進表記が普通で、搭載メモリ容量はワード数で表記されるのが普通だった。したがって、基本論理アドレス空間は32Kワードだが、上位4Kワード(アドレス 160000 から 177777 まで)は周辺機器のレジスタのマッピング用に予約されており、メモリはマッピングされない。したがって、初期のPDP-11の最大メモリ容量は28Kワードだった。

この制約に対して、以下のような技法が使われた。

- 後期のPDP-11では、仮想記憶をサポートするメモリ管理ユニットが使われた。物理アドレスは18ビットまたは22ビットに拡張され、256KBまたは4MBのメモリを扱えるようになったが、1つの論理アドレス空間は16ビット(32Kワード)に制限されたままだった。

- PDP-11/45をはじめとする機種では、命令用論理空間(32Kワード)とデータ用論理空間(32Kワード)を設定可能とした。初期のUNIXなどはこの機能を使っていた。

- 例えば Modula-2 の実装では、実行環境が論理空間を8kBのページに分割して制御し、ユーザーからは隠蔽した形でバンク切り換えのような操作を行っていた(外部リンク参照)。

アドレッシングモード

多くの命令で6ビットで1オペランドを構成しており、3ビットで8本ある汎用レジスタのいずれかを指定し、3ビットで8種類あるアドレッシングモードのいずれかを指定する。このため八進表記が自然に使われた。

以下では仮の1オペランド命令をOPRで表し、アセンブリ言語でのアドレッシングモードの表現を示す。Rnは汎用レジスタを意味し、R0からR7まである。コードの "n" はレジスタ番号である。

汎用レジスタのアドレッシングモード

任意の汎用レジスタに適用できる8種類のアドレッシングモードを下表に示す。なお、R6(スタックポインタ)とR7(プログラムカウンタ)については別に解説する。

2オペランド命令では両方のオペランドでこれらのモードを使える。インデックスおよびインデックス間接モードは命令に続くワードも命令の一部として使用するので、2オペランド命令は3ワードになる場合がある。

自動インクリメントと自動デクリメントはバイト命令なら1ずつ、ワード命令なら2ずつインクリメント/デクリメントする。間接モードの場合、ポインタ1つ分のインクリメント/デクリメントになるので、2ずつとなる。

プログラムカウンタのアドレッシングモード

R7(プログラムカウンタ)を使用する場合、以下の4つのアドレッシングモードが意味のある効果を発揮する。

絶対モードは例えば、固定のアドレスにマッピングされたI/Oレジスタのアクセスに使用する。相対モードはプログラムの変数を参照する場合や分岐先を指定する場合に使用する。相対モードや相対間接モードのみを使ったプログラムは位置独立となる。つまり、プログラムを配置するアドレスが仮定されていないので、任意の位置にロードでき、移動させることも可能である(リロケータブルバイナリ)。

イミディエートモードと絶対モードは通常の自動インクリメントモードと自動デクリメント間接モードに対応している。上の表にあるように補助ワードを「命令内」にあるとするか、命令の次のワードと考えるかは立場によって異なる。なお、PCは常に次々と命令を指していくので、常に2ずつ自動インクリメントされる。

スタックのアドレッシングモード

R6はSPと表記されることもあり、トラップや割り込みの際のハードウェアスタックのスタックポインタとして使われる。このスタックは、アドレスの小さい方に向かって成長する。SPまたはプログラマがソフトウェアスタックのスタックポインタとして選択した任意のレジスタには、次のようなアドレッシングモードがある。

ソフトウェアスタックはバイトも積むことができるが、SPの場合はワードしか積まない。従ってSPの自動インクリメント/自動デクリメントは常に2ずつである。

命令セット

PDP-11はバイト(群)やワード(群)を操作する。バイト(群)はレジスタ番号で指定され、そのレジスタの下位バイトを直接操作するか、そのレジスタでメモリ位置を指す。ワード(群)もレジスタ番号で指定され、そのレジスタの内容を直接操作するか、そのレジスタでメモリ位置を指す。ワードは偶数番地境界になければならない。オペランドのあるほとんどの命令で、ビット15がセットされているものはバイトアドレッシングで、ビット15がクリアされているものはワードアドレッシングである。以下の表で示すとおり、ニーモニックの最後尾に "B" をつけるとバイト操作を意味する(例えば、MOV と MOVB)。

2オペランド命令

命令の先頭4ビットが命令コードである(特にビット15でワードアドレッシングかバイトアドレッシングかを示す)。6ビットで1オペランドとなっており、2オペランドある。オペランドの内容については上述のアドレッシングモードを参照。

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| opcode | mode | source | mode | destination | |||||||||||

ADD命令とSUB命令はワードアドレッシングであり、バイトを対象とするバージョンは存在しない。

一部の2オペランド命令は、一方のオペランドにレジスタしか指定できない。

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| opcode | register | mode | source/destination | ||||||||||||

ここで、レジスタペアが使われる。「(R,R+1)」のように記述し、Rレジスタが上位ワードであって偶数番目でなければならない。2つ目のレジスタは下位ワード(または余り)である。乗算ではRが奇数番目のレジスタであってもよいが、その場合の積の上位ワードはレジスタに保持されない。

1オペランド命令

命令の先頭10ビットが命令コードで、特にビット15はワードアドレッシングかバイトアドレッシングかを示す。先頭4ビットの組合せのほとんどが2オペランド命令で使われているため、命令コードが9ビットであっても、それほど命令の種類は多くない。残り6ビットで1オペランドを表す。

| 15 | 11 | 10 | 6 | 5 | 3 | 2 | 0 | ||||||||

| B | 0 | 0 | 0 | 1 | Opcode | Mode | Register | ||||||||

SWAB命令は指定したワードの上位バイトと下位バイトを入れ替えるもので、バイトアドレッシングは存在しない。

条件分岐命令

多くの分岐命令は、PSW(ステータスレジスタ)の条件コードの状態に基づいて分岐するか否かを決定する。一般に直前にCMP命令、BIT命令、TST命令などを行って条件コードをセットする。算術演算命令や論理演算命令も条件コードをセットする。インテルのx86とは異なり、MOV命令も条件コードをセットする。したがって、転送した値がゼロか否か、負か否かで条件分岐することもできる。

命令の上位8ビットが命令コードである。下位8ビットで現在のプログラムカウンタからの相対オフセットを指定する。オフセットはワード数であり、分岐先アドレスはそれを2倍してPCに加えたものとなる。またオフセットは符号付整数なので、前方にも後方にも分岐できる。

| 15 | 11 | 10 | 8 | 7 | 0 | ||||||||||

| x | 0 | 0 | 0 | 0 | Opcode | Offset | |||||||||

2オペランド命令の表にある SOB (subtract one and branch) も条件分岐命令である。レジスタオペランドをデクリメントし、結果がゼロでないとき命令の下位6ビットを符号なしオフセットと解釈して後方に分岐する。

分岐できる範囲が限られているため、コードが成長していくとこれらの命令では分岐先に到達できなくなる可能性がある。その場合2ワードを必要とするJMP命令に書き換え、JMP命令は無条件分岐なので、例えば元が BEQ だった場合は BNE に書き換えてJMP命令をスキップするようにする。

ジャンプとサブルーチン関連

- JMP (ジャンプ)

- JSR (サブルーチンコール)

- RTS (サブルーチンから復帰)

- MARK (復帰時のスタックのクリーンアップ)

- EMT (エミュレータトラップ)

- TRAP, BPT (ブレークポイントトラップ)

- IOT (入出力トラップ)

- RTI & RTT (割り込みからの復帰)

JSR命令は任意のレジスタをスタック上にセーブできる。セーブすべきレジスタがない場合はPCを指定し (JSR PC,address)、サブルーチンから復帰する際も RTS PC とする。例えば、"JSR R4, address" としてサブルーチンを呼び出すと、R4の元の値がスタックのトップに置かれ、リターンアドレス(JSR命令の次の命令のアドレス)が R4 に格納される。リターンアドレスの位置にはコードではなくデータを置いておいて (R4)+ で読み込んだり、ポインタを置いておいて @(R4)+ で読み込む。すると自動インクリメントでデータ部分を飛ばすことになり、R4が真のリターンアドレスになる。そこで RTS R4 を実行すれば正しい位置に復帰できる。

その他の命令

- HALT, WAIT (割り込みを待ち合わせる)

- RESET (Unibusをリセット)

条件コード操作

- CLC, CLV, CLZ, CLN, CCC (対応する条件コードをクリア)

- SEC, SEV, SEZ, SEN, SCC (対応する条件コードをセット)

ステータスレジスタ (PSW) には以下の4つの条件コードがある。

- N - 負値であることを示す。

- Z - ゼロ(比較結果が等しい)であることを示す。

- V - オーバーフローが発生したことを示す。

- C - キャリーが発生したことを示す。

SCCとCCCはこれら4つを全てクリアまたはセットする。

オプションの命令セット

- 拡張命令セット(extended instruction set、EIS)

- PDP-11/35、11/40、11/03 でのオプション。後期機種では標準となった。

MUL、DIV- 乗算と除算ASH、ASHC- 算術シフト

- 浮動小数点命令セット (floating instruction set、FIS)

- PDP-11/35、11/40、11/03 でのオプション。

FADD、FSUB、FMUL、FDIV- 単精度のみ。レジスタオペランドの指すスタック上の浮動小数点数を対象とする。

- 浮動小数点プロセッサ (floating-point processor、FPP)

- PDP-11/45およびその後の多くの機種でのオプション。

- ビジネス命令セット (commercial instruction set、CIS)

- 11/23 と 11/24 ではマイクロコードによるオプション、11/44では追加モジュール、11/74では一部バージョンでサポート。COBOL と Dibol で使用する各種文字列命令と十進命令をサポート。

- PSWアクセス命令

- PSWはメモリアドレス 177 776 にマッピングされているが、最初期の機種以外では以下のような命令があって、PSWにより直接的にアクセスできる。

SPL- 優先度レベルの設定MTPS- PSWへ転送MFPS- PSWから転送

- 他のメモリ空間へのアクセス命令

- 命令論理空間とデータ論理空間を複数提供する後期機種において、他の論理空間にアクセスするための命令群で、直交性がない。例えば、オペレーティングシステム内のランタイムサービス(システムコール)ルーチンが呼び出し側と情報交換するのに用いた。

MTPD(move to previous data space)MTPI(move to previous instruction space)MFPD(move from previous data space)MFPI(move from previous instruction space)

Remove ads

アセンブリ言語によるプログラミング例

RT-11で動作するPDP-11マクロアセンブラによる Hello world プログラムである:

.TITLE HELLO WORLD

.MCALL .TTYOUT,.EXIT

HELLO:: MOV #MSG,R1 ;STARTING ADDRESS OF STRING

1$: MOVB (R1)+,R0 ;FETCH NEXT CHARACTER

BEQ DONE ;IF ZERO, EXIT LOOP

.TTYOUT ;OTHERWISE PRINT IT

BR 1$ ;REPEAT LOOP

DONE: .EXIT

MSG: .ASCIZ /Hello, world!/

.END HELLOこのプログラムのファイル名をHELLO.MACとしたとき、アセンブルしてリンクして実行するときのコンソールの表示は以下のようになる:

.MACRO HELLO

ERRORS DETECTED: 0

.LINK HELLO

.R HELLO

Hello, world!

.(RT-11のコマンドプロンプトは「.」である)

MACRO-11 のコードのもっと複雑な例としては、ケビン・ミュレル[11]の KPUN.MAC[12] やファーバ・リサーチ[13]の JULIAN[※ 3] ルーチンがある。その他のPDP-11用コードのライブラリとして Metalab[※ 4] や Trailing Edge[※ 5] アーカイブがある。

これらのコードを PDP-11 エミュレータで実行してみることもできる。ボブ・スプニク[14]の SIMH はPDP-11だけでなく各種アーキテクチャをエミュレートでき、それらアーキテクチャのオペレーティングシステムのソフトウェアキットを含む(RT-11もある)。

Remove ads

PDP-11 の機種

要約

視点

PDP-11プロセッサはI/Oバスの種類などでいくつかのグループに分類される。いずれのグループも各機種にはOEM版とエンドユーザー版がある。どの機種であっても命令セットは同じだが、後期機種には新命令が追加されており、一部命令の動作が若干異なる。アーキテクチャの進化に伴い、プロセッサのステータス/コントロールレジスタ群の扱い方も変化している。

Unibus 機種

以下の機種は主要バスとして Unibus を使用:

- PDP-11(後に PDP-11/20 に改名), PDP-11/15 - 最初の機種。マイクロプログラム方式でないプロセッサを使用。ジェームス・オラフリン[15]が設計。浮動小数点数はオプション。

- PDP-11/35, 11/40 - /20 をマイクロプログラム方式にした後継。ジェームス・オラフリンが設計チームを率いた。

- PDP-11/45, 11/50, 11/55 - 磁気コアメモリと同時に半導体メモリ(最大256kB)を使用可能とした高速なマイクロプログラム方式プロセッサ。FP11 FPU をオプションでサポートし、浮動小数点数のフォーマットがこれによって確立された。

- PDP-11/70 - 11/45 のアーキテクチャを物理メモリ4MBまで拡大し、専用メモリバスを装備し、2Kバイトのキャッシュメモリを備え、Massbus で 高速I/Oデバイスを接続。

- PDP-11/05, 11/10 - 11/20のコスト低減版

- PDP-11/34, 11/04 - 11/35と11/05のコスト低減版。PDP-11/34 のコンセプトはボブ・アームストロング[16]によるもの。11/34はUnibusメモリを最大256kBまでサポート。11/34a ではFPUオプションをサポートし、11/34c ではキャッシュメモリオプションをサポート。

- PDP-11/60 - ユーザーが書き込み可能なマイクロプログラム記憶装置を持つ PDP-11。ジェームス・オラフリンが率いる別のチームの設計

- PDP-11/44 - 11/45と11/70の後継。標準でキャッシュメモリと浮動小数点ユニットを装備したもの。このマシンには洗練されたシリアル・コンソールを装備し、4MBの物理メモリをサポート。設計チームは John Sofio が率いた。複数ICでCPUを構成した最後の機種。

- PDP-11/24 - Unibus使用のPDP-11で初のVLSI版 PDP-11。Fonz-11 (F11) チップセットとUnibusアダプタを使用

- PDP-11/84 - VLSI Jaws-11(J11) チップセットとUnibusアダプタを使用

- PDP-11/94 - J11ベースで 11/84 よりも高速

Q-bus 機種

以下の機種は主要バスとして Q-bus を使用:

- PDP-11/03 (LSI-11/03) - 最初のLSI版 PDP-11。ウェスタン・デジタル社のMCP-1600チップセットを使用し、60kBまでのメモリをサポート。

- PDP-11/23 - 第2世代のLSI (F-11) を使用。初期のユニットのメモリ容量は 248Kバイトだが、後に 4Mバイトまでサポートするようになった。

- PDP-11/23+/MicroPDP-11/23 - プロセッサカード上の機能を強化した 11/23

- MicroPDP-11/73 - 第3世代LSI-11。高速な Jaws-11 (J-11) チップセットを使用し、最大4MBのメモリをサポート。

- MicroPDP-11/53 - オンボードメモリを持つ低速版 11/73

- MicroPDP-11/83 - PMI(private memory interconnect)を使った高速版 11/73

- MicroPDP-11/93 - さらに高速。Q-bus を使用した最後の PDP-11

- Mentec M100 - Mentecが再設計した 11/93.J-11チップセットを 19.66MHz で駆動し、4個のオンボード・シリアルポート、最大4MBのオンボードメモリ、オプションのFPUがある。

- Mentec M11 - プロセッサアップグレードボード。Mentec による PDP-11マイクロコードの実装で、テキサス・インスツルメンツの TI 8832 ALU と TI 8818 マイクロシーケンサを使用。

- Mentec M1 - プロセッサアップグレードボード。Mentec による PDP-11マイクロコードの実装で、Atmelの0.35μm版ASICを使用[17]。

- Quickware QED-993 --高性能 PDP-11/93 プロセッサアップグレードボード

標準以外のバスを採用した機種

- PDT-11/110

- PDT-11/130

- PDT-11/150

PDTシリーズは「スマート(賢い)端末」としてマーケティングされたデスクトップシステムである。/110 と /130 はVT100端末と同じ筐体だった。/150は8インチFDDを2つ、非同期シリアルポートを3つ、プリンターポートを1つ、モデムポートを1つ、同期シリアルポートを1つ備えた装置で、端末そのものは別途接続する必要がある。どれもLSI-11/03と同じ4つのチップで構成されるチップセットを使用している。/150とVT105を組み合わせたシステムは MiniMINC として販売された。

- PRO-325

- PRO-350

- PRO-380

DEC Professional シリーズは IBMの 8088 や 80286 ベースの初期のパーソナルコンピュータに対抗しようとしたデスクトップ機である。5.25インチフロッピーディスクドライブを装備し、325 以外はハードディスクも装備していた。CPU は LSI-11 で、RSX-11M+ にメニューシステムを追加した P/OS が動作した。既存のPDP-11とのソフトウェア互換を意図的に阻害したため、(DEC以外の人々に予想された通り)市場では全く振るわなかった。また、RT-11も移植された。DEC内部ではRSTS/Eも移植されたが、外部にはリリースされなかった。325と350は DCF-11 (Fonz) チップセットを採用しており、PDP-11/23などと同じである。380は DCJ-11 (Jaws) チップセットを採用しており、MicroPDP-11/53 などと同じだが、周辺チップセットの制約からクロック周波数は10MHzに制限されていた。

実際には商品化されなかった機種

- PDP-11/27 - 主要I/Oバスとして VAXBIバス(VAX用32ビットバス)を使った Jaws-11 を使った実装

- PDP-11/68 - 物理メモリ4MバイトをサポートするPDP-11/60の後継

- PDP-11/74 - PDP-11/70をマルチプロセッサ化したもの。最大4個のプロセッサを相互接続し、ケーブルの取り回しが非常に難しくなった。また、ビジネス向きの命令セット拡張も行われている。いくつかのプロトタイプが組み立てられ、少なくとも2台のマルチプロセッサシステムがユーザーサイトでベータテストを受けたが、公式には出荷されることはなかった。4プロセッサシステムは RSX-11 オペレーティングシステム開発チームがテストし、シングルプロセッサ機は開発チーム全体のタイムシェアリング環境として使われた。11/74は32ビット機 VAX 11/780 と同時期に計画された。フィールドでの保守の問題でキャンセルされた[18]。いずれにしてもDECはPDP-11ユーザー全部をVAXに移行させることはできなかった。その原因は性能ではなく、PDP-11のリアルタイム性の良さにある[要出典]。

特殊バージョン

- GT40 - PDP-11/05をベースとしたベクターグラフィック端末

- GT42 - PDP-11/10をベースとしたベクターグラフィック端末

- GT44 - PDP-11/40をベースとしたベクターグラフィック端末

- GT62 - PDP-11/34aをベースとしたベクターグラフィック端末

- H-11 - LSI-11/03の Heathkit社 OEM版

- VT20 - PDP-11/05ベースのテキスト端末(ダイレクトマップ方式)で、テキスト編集と組版用

- VT71 - LSI-11/03ベースのテキスト端末(ダイレクトマップ方式)で、テキスト編集と組版用

- VT103 - LSI-11を搭載したバックプレーン内蔵のVT100端末

- VT173 - PDP-11/03をベースとしたハイエンド端末。ホストからシリアル接続で編集ソフトウェアをダウンロードして使用できる。出版社などで使われた。

- MINC-11 -- PDP-11/03 または 11/23 をベースとした実験用システム[19]。11/23ベースのものは MINC-23 として販売されたが、MINC-11からMINC-23へのフィールドアップグレードが可能だった。命令セットが微妙に変更されており、MINC-23用ソフトウェアは11/23では動作できないことがあった。後期モデルでは互換性を確保していた。

- C.mmp -- カーネギーメロン大学によるマルチプロセッサシステム

海賊版クローン

PDP-11は非常に人気があったため、鉄のカーテンの向こう側で無許可のクローンが何種類か製造された。一部はDECのPDP-11とピン互換があり、周辺機器やシステムソフトウェアを流用することができた。以下のような機種が知られている:

- SM-4、SM-1420、SM-1600、エレクトロニカBKシリーズ、Electronika 60、DVK、UKNC(ソビエト連邦、PDP-11ский(PDP-11スキイ)とも呼ばれ、DECの米国内の生産台数より多かったと推定されている)。Elektronika 85、90は、いわゆるポケットコンピューターのような極小のフォームファクタで製品化されていた。

- SM-4、SM-1420、IZOT-1016、および周辺装置(ブルガリア)

- SM-1620、SM-1630(東ドイツ)

- MERA-60(ポーランド)

- SM-4、TPA-1140[20]、TPA-1148[21]、TPA-11/440[22](ハンガリー)

- CalData CDP-XI — アメリカ製で、DEC製OSが全て動作した[23]。

Remove ads

オペレーティングシステム

PDP-11では以下のようなオペレーティングシステム (OS) が使用可能であった。

DEC製:

- BATCH-11/DOS-11 - PDP-11ファミリ用の最初のOSだが、後に登場したRT-11に取って代わられた。

- DSM-11 (Digital Standard MUMPS) - MUMPS環境のDECによる実装。

- RSTS/E - マルチユーザー・タイムシェアリングシステム

- RSX-11 - リアルタイムオペレーティングシステム。VMSやWindows NT系を設計した、デヴィッド・カトラーが初めて設計したOS。Windows NT の遠い祖先にあたる。

- IAS - Interactive Application System、1975年ごろ登場したOSでRSX-11から派生。

- P/OS - PDP-11ベースのパーソナルコンピュータ用OS、RSX-11から派生。

- RT-11 - シングルユーザー・リアルタイムオペレーティングシステム

- Ultrix-11 - DEC自身によって移植されたUNIX

サードパーティー製:

- ANDOS - ソビエト連邦製。ファイルシステムはFAT12互換。

- CSI-DOS - ソビエト連邦製。

- DEMOS - ソビエト連邦製。Unix系。

- Duress - イリノイ大学アーバナ・シャンペーン校とDatalogicsが開発。[24]

- Fuzzball - LSI-11ベースのルーター。NSFnetの初期のバックボーンを形成した。

- MERT[24] - ベル研究所がUNIXから派生させたマイクロカーネル的なOS。

- MK-DOS -ソビエト連邦製。

- MONECS - モナシュ大学で開発。教育用であり、言語処理系が豊富。

- MUMPS - 医療情報処理環境。

- PC11 - ピルキントンが開発したプロセス制御OS。[24]

- polyForth - Forth Inc. によるForth環境。

- Solo - Concurrent Pascal で書かれたシングルユーザーOS[25]

- TRIPOS - ケンブリッジ大学の実験的OS。PDP-11以外にもデータゼネラル Nova やMC68000で動作した。

- TSX-Plus - RT-11ベースのマルチユーザーOS

- UCSD p-System - UCSD Pascal の開発環境を発展させたOS。

- UNIX - 様々なバージョンがあり、主なものとして Version 6 Unix、Version 7 Unix、UNIX System III、2BSD、Venix がある。

- Xinu - 教育用Unix系OS。

Remove ads

使用

PDP-11ファミリは様々な用途で使われた。標準ミニコンピュータとして、タイムシェアリングシステム、科学技術計算、教育、ビジネスなどに使われた。またリアルタイムシステムとして、プロセス制御やファクトリーオートメーションにも使われた。

OEM版は大規模システムの制御用組み込みシステムとして使われることが多かった。交通信号システム、医療システム、CNC機械加工、ネットワーク管理などに使われた。例えば、パケット交換網の管理に使われた例がある。1980年代のイギリスの航空交通管制でのレーダー情報処理には、PDP-11/34をベースとしたシステムが使われていた。放射線療法機器セラック25はPDP-11/23を組み込んでいた[26]。

テラダインは半導体試験装置のテストプログラム格納用にPDP-11を採用していた。組み込みシステムで使われたPDP-11は、ソフトウェアの2000年問題で使用不可能になるまで使われ続けたものが多い。アメリカ海軍は、パイロットの空間識失調状態の訓練を行うシミュレータで、2007年までPDP-11/34を使い続けていた。今ではPDP-11のソフトウェアをPC上のエミュレータで実行している[27]。

注釈

出典

参考文献

関連文献

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads