热门问题

时间线

聊天

视角

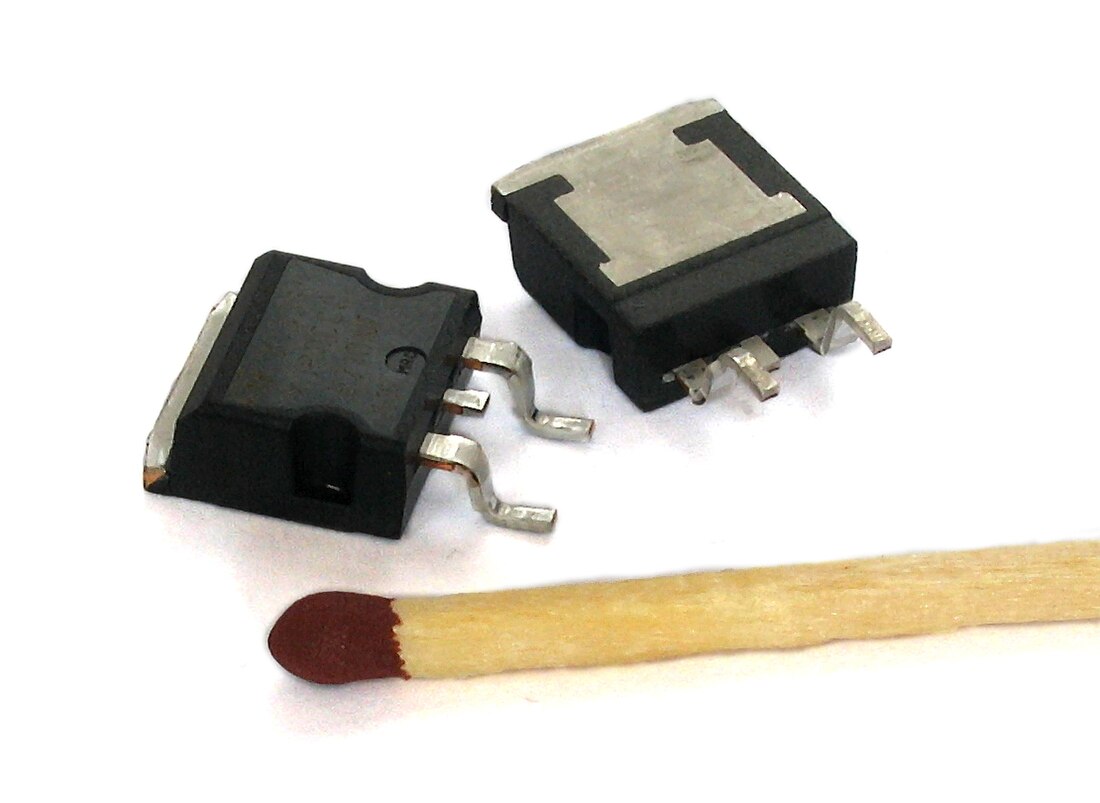

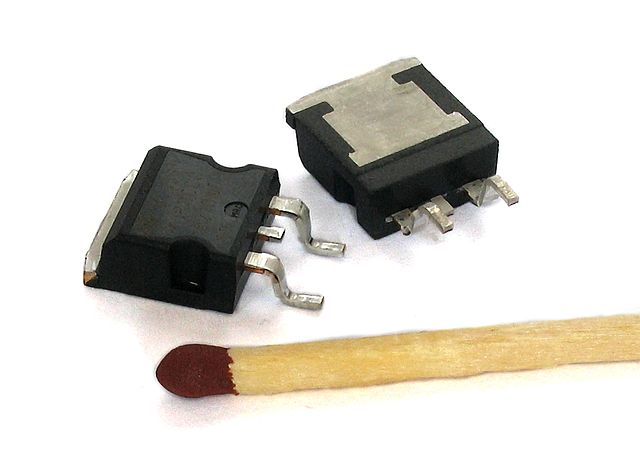

功率MOSFET

專門處理大功率電壓及電流的MOSFET 来自维基百科,自由的百科全书

Remove ads

功率MOSFET(英语:Power MOSFET)是专门处理大功率的电压和电流的金属氧化物半导体场效电晶体(MOSFET),也是功率半导体的一种。和其他功率半导体(例如绝缘栅双极晶体管或晶闸管)比较,功率MOSFET的优点是其切换速度快,在低电压下的高效率。功率MOSFET和IGBT都有隔离的闸体,因此在驱动上比较容易。功率MOSFET的缺点是增益较小,有时闸极驱动的电压甚至比实际要控制的电压还低。

MOSFET及互补式金属氧化物半导体(CMOS)技术持续的演进,自1960年起已用在积体电路上,这也是功率MOSFET的设计得以实现的原因。功率MOSFET和一般信号级的MOSFET原理相同。功率MOSFET常用在电力电子学,是源自信号级的MOSFET,自1970年代开始有商品贩售[2]。

功率MOSFET是最常见的功率半导体,原因是因为其闸极驱动需要的功率小、以及快速的切换速度[3]、容易实施的并联技术[3][4]、高频宽、坚固性、偏压简单、容易使用、也容易维修[4]。在低压(200V以下)的应用中,功率MOSFET是最常见的功率半导体。功率MOSFET可以用在许多不同的领域中,包括大部份的电源供应器、直流-直流转换器、低电压电机控制器等,以及许多其他的应用。

Remove ads

历史

金属氧化物半导体场效电晶体是贝尔实验室的Mohamed Atalla和Dawon Kahng在1959年发明的,是电力电子学的一大突破。MOSFET一代一代的推进,让电力电子元件的设计者可以达到双极性电晶体无法达到的性能以及功率密度[5]。

日立制作所在1969年发明了第一个垂直式的功率MOSFET[6],之后称为VMOS(V 型槽MOSFET)[7]。日本产业技术综合研究所的Y. Tarui, Y. Hayashi和Toshihiro Sekigawa首次提出有自对准闸极的双扩散MOSFET(DMOS)[8][9]。1974年时,日本东北大学的西泽润一发明了用在音频上的功率MOSFET,很就由山叶公司生产,用在高保真音频功率扩大器。JVC、Pioneer、索尼及东芝也开始在1974年开始生产有功率MOSFET的放大器[10]。Siliconix在1975年开始贩售VMOS[7]。

VMOS和DMOS发展成当时所谓的VDMOS(垂直型DMOS)[10]。惠普实验室John Moll的研突团队在1977年制作了DMOS的原型,展示DMOS比VMOS优越的特性,包括低导通阻抗以及高崩溃电压[7]。日立在同一年开发了横向扩散金属氧化物半导体(横向DMOS),属于平面型的DMOS。日立是1977年至1983年之间,唯一的LDMOS制造商,当时的LDMOS是由HH Electronics和Ashly Audio用在音频功率扩大器中,也用在音乐以及公共广播系统中[10]。当2G数位蜂窝网络在1995年开始使用时,LDMOS广为使用在2G、3G等无线网路的无线电功率扩大器中[11],后来也用在4G网路中[12]。

Alex Lidow于1977年在史丹佛大学和Tom Herman共同发明了HexFET,六边形的功率MOSFET[13][14]。国际整流器公司在1978年开始贩售HexFET[7][14]。绝缘栅双极晶体管(IGBT)结合了功率MOSFET以及双极性电晶体(BJT)的特点,是由通用电气的B·贾扬特·巴利加在1977年至1979年所发明的[15]。

超接合面(Super Junction)MOSFET是用P+ columns穿透N-外延层的MOSFET。将P层和N层叠层的概令念最早是由大阪大学的Shozo Shirota和Shigeo Kaneda在1978年提出[16]。飞利浦的David J. Coe发明了超接合面的MOSFET,作法是将p型及n型的层对调,并且因此在1984年申请了美国专利,在1988年通过[17]。

Remove ads

应用

功率MOSFET是最常用到的功率半导体[3]。截至2010年[update],功率MOSFET占功率半导体市场的53%,比绝缘栅双极晶体管(27%)、射频功率放大器(11%)及双极性电晶体(9%)要多[18]。截至2018年[update],每年销售的功率MOSFET超过五百亿个[19],其中包括沟槽式(Trench)功率MOSFET,到2017年二月为止已销售一百亿个[20],以及意法半导体的MDmesh(超接合面MOSFET),截至2019年[update]已贩售五十亿个[16]。

RF DMOS,也称为RF功率MOSFET,是设计在射频(RF)应用的DMOS功率电晶体,用在许多电台广播及无线电应用中[23][24]

功率MOSFET也常用在运输技术中[25][26][27],包括许多不同种类的载具。

在汽车产业中[28][29][30],功率MOSFET是常见的汽车电子元件[31][32][21]。

功率MOSFET(包括DMOS、LDMOS及VMOS)也可以用在其他的应用领域中。

Remove ads

基本结构

在第一个商用功率半导体问世的1970年代,已研发了许多的结构,不过大部份(至少到目前为止)已不再开发,主要的结构为垂直扩散MOS(VDMOS)结构(也称为是双扩散MOS,或DMOS),以及横向扩散金属氧化物半导体(LDMOS)结构。

VDMOS的截面(如图1)可以看出元件的“垂直特性”:可以看出源极电极放在汲极的上方,在电晶体导通时,电流主要是垂直路径。VDMOS的“扩散作用”是指其制程。P极井(如图1)是透过扩散过程形成(其实是双重扩散过程,产生P和N+区,因此称为双扩散)。

功率MOSFET和侧向MOSFET的结构不同:就像大部份功率元件一样,其结构是垂直的,不是水平的。在平面结构中,电流和击穿电压额定都是通道大小的函数(也就是通道的长和寛),因此在矽晶面积上没有有效率的使用。在垂直架构中,电晶体的电压额定是N磊晶掺杂及厚度的函数(可以参考图1),而电流额定是通道宽度的函数。因此可以让电晶体在小的矽晶元中,可以维持高截止电压以及大电流额定。

LDMOS是侧向结构的功率MOSFET,主要是用在高端音响放大器[10]以及无线蜂窝网络(例如2G、3G[11]及4G[12])用的无线电功率放大器 。好处是在饱和区(对应电晶体的线性区)特性比VDMOS好。VDMOS主要用在切换的应用中,只会有开和关二个状态,不需考虑饱和区的特性。

当功率MOSFET在导通状态时,在汲极和源极之间有电阻性的行为。在图2中可以看到电阻(称为RDSon,表示导通时,在汲极和源极之间的电阻)是以下电阻的和:

- RS是源极电阻。代表了从封装的端子到MOSFET通道之间的所有电阻:包括打线接合的电阻、源端金属化的电阻,以及N+井的电阻。

- Rch是通道电阻,和通道寛度成反比。通道电阻是低压MOSFET中,RDSon的主要贡献来源,因此有许多的研究是在缩小晶元大小,增加通道密度。

- Ra是接触电阻,若电阻的方向从水平(通道)变成垂直(到汲极接触)时,接触电阻表示在闸极电阻下磊晶区的电阻。

- RJFET是上述尺寸减少造成的不良影响:P注入(如图1)形成了闸极的寄生JFET电晶体,会减少电流的流动。

- Rn是磊晶层的电阻,磊晶层的作用是维持截止电压,Rn直接和元件的电压额定有关。高压的MOSFET需要较厚,较少掺杂的磊晶层,也就是高电阻,相对的,低压的MOSFET只需要较薄的磊晶层,但掺杂要比较多,也就是低电阻。因此,Rn是高压MOSFET中,RDSon的主要贡献来源。

- RD是汲极电阻,其特性类似RS,代表了电晶体基板的电阻(截面图是示意图,未照实际比例,底下的N+层其实是最厚的)以及连接到封装端子之间的电阻。

Remove ads

在不导通时,功率MOSFET可以等效为PIN二极体(由the P+扩散层、N−磊晶层以及N+基板组成)。在这个高度不对称的结构逆向偏压时,无载子的区域会往低掺杂的区域扩展,也就是N−层的上方。表示这一层需要承受不导通时,大部份汲极到源极的电压。

不过当MOSFET在导通状态时,N−层没有功能,而且,因为是低掺杂的区域,其本质电阻无法忽略,会加在导通时的电阻RDSon当中(就是图2中的电阻Rn)。

二个主要的参数决定了电晶体的崩溃电压以及RDSon:掺杂程度以及N−磊晶层厚度。磊晶层厚度越厚,掺杂越少,崩溃电压越高。相反的,磊晶层厚度越薄,掺杂越多,RDSon越低(MOSFET的导通损失也会越少)。因此这是MOSFET设计上的取舍,在电压额定以及导通电阻之间进行取舍[来源请求],这也是图3所描述的。

在图1中可以看到,MOSET的工作原理只要源极连接到N+区,但源极的金属化连接了N+和P+的注入部份。若有这样的情形出现,会形成在N掺杂源极以及汲极之间的浮动的P区,可以等效为NPN电晶体,有一个未连接的基极。在特定情形下(例如汲极有大电流、汲极到源极的电压有数伏特的大小),会触发杂散NPN电晶体,使得MOSFET不可控。P注入层到源极金属化部份的连接会使杂散电晶体的基极对射极短路(MOSFET的源极),因此不会有了寄生锁存效应。

不过这解法在MOSFET的汲极(阴极)和源极(阳极)之间产生了二极体(本体二极体,body doide),使其只能单一方向阻隔电流。

在H桥或半桥的电路组态中,若是电感性负载,可以把本体二极体用来作为续流二极管。这些二极管的顺向导通压降会比较高,但可以承受大电流,在许多的应用中已经足够,而且可以节省元件个数,减少设备的成本以及电路板的大小。

切换特性

功率MOSFET是单载子元件,可以高速进行切换。没有双载子元件需要移除少数载子的问题。不过功率MOSFET的切换速度仍有本质上的限制,就是MOSFET中的内部电容(如图4)。在MOSFET切换时,需要将电容器充电及放电。流进闸极电容的电流会受到外部驱动电路的限制,因此充放电的速度会比较慢。若不考虑功率电路中的电感,驱动电路会主控MOSFET的切换速度。

在MOSFET的datasheet中,电容会用Ciss(汲极和源极短路时的输入电容)、Coss(闸极和源极短路时的输出电容)、Crss(源极短路到地时的反向传递电容)。这些电容和内部电容的关系如下:

其中CGS、CGD和CDS是闸极对源极、闸极对汲极、汲极对源极的电容。供应商选用Ciss、Coss和Crss来标示的原因是可以直接量测。而CGS、CGD和CDS比较接近物理上的意义,条目后续内容也会用此方式说明。

Remove ads

闸极对源极电容CGS是由CoxN+、CoxP和Coxm的并联连接组成(如图4)。N+和P区都是高度掺杂的区域,这二部份的电容可以视为是常数,Coxm是多晶矽闸极和金属源极之间的电容,也是常数。因此一般会将CGS视为是常数,不会随电晶体的状态而改变。

闸极对汲极电容CGD可以视为二个基本电容串联后所组成。第一个是氧化层的电容(CoxD),是由闸极电极、二氧化矽以及上方N磊晶层所产生,这个电容是定值。第二个电容(CGDj)是因为MOSFET不导通时,空乏层的扩展所产生,因此和源极及汲极之间的电压有关。CGD的值为:

空乏层的宽度为[33]

其中是矽的电容率,q是电子电荷,N是掺杂程度。CGDj的值可以用平板电容器的公式来近似:

其中AGD是源极及汲极重叠部份的面积,因此:

可以看出CGDj(以及CGD)的电容值会随源极及汲极的电压而改变。若电压是增加,则电容也会增加。若MOSFET在导通态,CGDj短路,闸极对汲极电容等于CoxD,为一定值。

Remove ads

因为源极的金属化会覆盖P井(如图1),汲极和源极的端子会被PN结隔开,因此CDS即为PN结的电容,电容是非线性电容,可以用类似CGDj的公式求得。

MOSFET的晶元需要和和外部的电路连接,多半会用打线接合的方式连接到MOSFET的端子(目前也在研究其他的接方式)。接线中会有杂散电感,这不是专门针对MOSFET的技术,但若在高速切换下,会有很明显的效应。杂散电感会使电流维持定值,在晶体关闭时会产生大电压,因此会增加切换损。

杂散电感在MOSFET的每一个端子都会出现,其影响不同:

- 闸极电感很小(假设小于数百nF),原因是闸极的电流梯度比较慢,。不过有时闸极电感和电晶体的输入电容器会产生振荡,可能会产生很大的切换损失,甚至会破坏设备,因此要设法避免。在一般的设计中,会维持杂散电感很低,让此一现象不会出现。

- 汲极电感会在MOSFET导通时设法减少汲极电压,因此可以降低切换导通损失(turn-on loss)。不过在关断MOSFET时也会产生大电压,因此会增加关断损失(turn-off loss)。

- 源极杂散电感的行为类似汲极电感,但会加上回授效应,会让切换持续的时间变长,增加切换损失。

- 在要开始快速开启时,因为源极杂散电感,晶元上的源极电压可以快速上升,闸极电压也可以快速上升,而内部的VGS会维持较低的值一段时间,因此会使切换时的导通变慢。

- 在要开始快速关断时,源极电感上的电流快速减少,上面的电压会变负值(相对包装外的导线),因此让内部的VGS增加,让MOSFET维持导通,因此切换时的关断也会变慢。

工作时的限制

闸极的氧化层很薄(100 nm,甚至更小),因此可以承受的电压有限。制造商会在资料表中列出闸极-源极电压的最大值,大约是20 V,若电压超过此限制值,可能会造成元件的损坏。而且,过高闸极-源极电压会让缩短MOSFET的寿命,降低RDSon的效果不明显,甚至没有效果。

为了改善这方面的问题,会配合闸极驱动器应用。

功率MOSFET在关断时,汲极-源极电压有最大值的限制,若电压超过此限值,会出现突崩溃的情形。若电压超过崩溃电压,会让功率开关误导通,可能因为误导通时产生的大量热量,造成开关或是其他电路的损坏。

一般而言,功率MOSFET的汲极电流需低于一定值(最大连续汲极电流)。汲极电流可以在短时间超过该限制值,不过仍需要小于最大脉波电流(有时会标示不同的脉波持续时间)。汲极电流会让内部元件(例如打线接合)因为焦耳加热而发热,也和其他现象有关(例如金属层的电迁移)。

为了功率MOSFET元件的可靠度,其结温(TJ)有最高温度的限制,此温度和MOSFET晶元的布置以及封装的材料有关。封装材料的模塑料以及人造树脂的特性,会元件的最高结温。

最高工作环境温度是由发热量以及热阻所决定。结点到外壳(junction-to-case)的热阻是元件以及封装的固有特性,外壳到环境(case-to-ambient )的热阻主要和在电路版上的布局、固定方式、散热片、气流或是散热液体流动有关。

功率MOSFET发热的方式(连续发热或是脉冲发热),会对应不同的热质量特性,也会会影响最大操作温度。一般来说,相同发热量下,若脉波的频率最低,最高工作环境温度就可以越高,因为元件可以冷却的时间比较长。有些模型(例如福斯特电抗定理)可以用来分析功率模组暂态下的温度特性。

安全工作区会结合功率MOSFET的汲极电流以及汲极-源极电压,定义MOSFET可以正常使用,不会损坏元件的电压及电流范围。一般会用图示的方式,在座标轴分别是汲极电流及汲极-源极电压的图上标示。汲极电流以及汲极-源极电压都需要低于其标示的最大值,而且其乘积也要小于元件可以散热的最大发热量。一般来说,功率MOSFET因为散热能力的限制,无法工作在汲极-源极电压以及汲极电流均为最大值的条件下[34]。

闩锁

功率MOSFET的等效电路中包括一个MOSFET,以及一个并联的寄生BJT。此BJT无法透过闸极进行控制,因此若导通了,就无法关闭。此一现象称为闩锁,会造成元件的毁坏。BJT可能因为p-type体区的电位差而导通。为了避免闩锁现象,MOSFET体以及源极之间会透过封装直接短路,避免有电位差。

技术

如上所述,功率MOSFET可以流过的电流是由其闸极通道的宽度所决定。闸极通道宽度是图中截面上的Z轴。

为了降低成本以及尺寸,会让晶元的面积越小越好。因此有许多的最佳化技术可以增加通道的表面积,也就是增加“通道密度”。作法包括在MOSFET晶元产生多个重复性的Cellular结构。针对这些单元,有提出几种不同的规划方式,最著名的是International Rectifier的HEXFET元件使用的六边形外形。

另外一种增加通道密度的方式是缩小基本结构的尺寸,因此可以在相同的表面积内容纳更多的单元,也就增加了通道密度。不过随著单元尺寸的缩小,要确保每一个单元的接面正常的难度也随之提高。因此会出现条形结构(如图所示)。条形结构在通道密度的效率不如Cellular结构,但是其长度可以比较小。平面结构的另一个优点是比较不会因为顺向偏压让杂散BJT导通产生的突崩溃而失效。在Cellular结构中,若任何一个单元的源极接触不好,就有可能会出现杂散BJT,进而出现突崩溃。而平面条状结构的MOSFET,只会因为外部热应力产生的突崩溃而使其损坏[35]。

P-substrate MOSFET(常简称PMOS)是掺杂方式相反的MOSFET(如图1,但P改为N,N改为P)。MOSFET是由P类的基板构成,有P−的磊晶。通道在N区,晶体是由闸极对源极的逆向电压导通。这适用于降压转换器,开关的一端接在输入电压的高电压侧。若是用N-MOSFET,此一组态需要提供的电压给闸极,但是用P-MOSFET,需要的电压不会超过。

这类MOSFET的主要缺点是导通特性不佳,因为是利用电洞作为载流子。电洞的载子迁移率比电子要差,而电导率和载子迁移率有关。PMOS元件的会是相同尺寸N-MOSFET的三倍。

VMOS结构在闸极有V型槽,是最早商品化的元件[36]。

此功率MOSFET结构(也称为trench-MOS),其闸极电极埋在矽蚀刻的沟槽内。因此可以产生垂直型的通道。此结构主要好处是没有JFET效应。UMOS的名称是源自其U型的沟槽。

针对电压等级超过500V的MOSFET,元件制造商(包括英飞凌科技以及其CoolMOS产品)开始使用电荷补偿原理(charge compensation principle)。使用此技术时,磊晶层的电阻(占高压MOSFET元件电阻的95%)可以缩小到原来的五分之一。

瑞萨电子为了提升超接合面(super-junction)MOSFET的生产效率以及可靠度,发展了有深沟槽(deep-trench)制程技术的超接合面结构。此技术是在低杂质的N型材料上馈蚀刻沟槽,以产生P型区。此制程克服了多层磊晶成长时的一些固有问题,其导通电阻及内部电容都很低。

因为超接合面结构的p-n接合面面积增加,相较于传统平面式的功率MOSFET,超接合面结构MOSFET的逆向恢复时间较短,但逆向恢复电流较大。

相关条目

参考资料

延伸阅读

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads