Loading AI tools

ウィキペディアから

NMOSロジック(N-type metal–oxide–semiconductor logic)は、論理回路とその他のデジタル回路を実装するためにn型MOSFET(金属-酸化物-半導体電界効果トランジスタ)を使用する[4]。 これらのn型MOSFETは、ソース端子とドレイン端子の間にあるp型半導体のボディの中に反転層を作ることによって動作する[5]。 n型チャネルと呼ばれるこの反転層は、n型半導体のソース端子とドレイン端子の間に電子を通すことができる。 n型チャネルは、ゲートと呼ばれる第三の端子に電圧を印加することによって作られる。 他のMOSFETと同様にn型MOSFETは、3つの動作領域を持つ。つまり、遮断領域(cut-off / subthreshold)、線形領域(linear / triode)、そして飽和領域(saturation / active)である[6][7]。

長年の間、NMOS回路は、かなり速度の遅いp型MOSFETを使う必要があったPMOS回路やCMOS回路と比較して遥かに高速だった[8]。 後にディプリーション負荷NMOSロジックが開発されて、NMOSの速度と消費電力はさらに改善された[9]。 CMOSよりもNMOSの方が容易に製造できた。CMOSは、p型サブストレート上に作った特殊なn型ウェル[注釈 1]の中にp型MOSFETを実装する必要があるからである[10]。

NMOSの主な欠点は、出力が定常状態(NMOSの場合Low)のときですら論理回路を通して直流が流れることであった[11]。当時の他のロジック・ファミリのほとんどが同じ問題を抱えていた。 このことは、静的な電力散逸を意味している。すなわち、回路がスイッチングしていないときですら電力が流出し、大きな電力消費が発生する[11]。

付け加えると、Diode-transistor logic、Transistor-transistor logic、エミッタ結合論理などと同様にNMOS回路とPMOS回路は、非対称入力ロジックレベルが原因でCMOSよりもノイズに弱かった[12]。

MOSは「金属-酸化物-半導体」という意味である。MOSFETが最初に作られたときの手法を反映してそのように呼ばれている。主に1970年代以前は、一般的にアルミニウムの金属ゲートを使っていたからである[13]。 しかしながら、1970年頃からほとんどのMOS回路は、ポリシリコンで作られた自己整合ゲートを使ってきた[13]。自己整合ゲートは、フェアチャイルドセミコンダクターにおいてフェデリコ・ファジンによって最初に開発された技術である。 ポリシリコンのゲートは、MOSFETを基本とした集積回路のほとんどの種類で未だに使われている。しかし、高性能マイクロプロセッサのような特定の種類の高速回路のために2000年代初頭から高融点金属ゲートが再登場し始めた[14]。

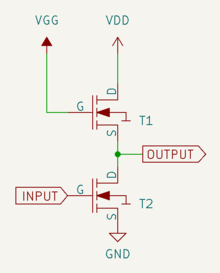

NMOSロジックで使われるMOSFETはn型エンハンスメントモードトランジスタであり、論理ゲート出力と負電源電圧(一般的にグランドのこと)の間、いわゆる「プルダウンネットワーク」(PDN)の中に配置されている[15][4]。 プルアップ(すなわち「負荷」であり、抵抗として考えることができる。以下参照)は、正電源電圧と各論理ゲート出力の間に配置されている[4]。

例えば、NMOS回路で実装されたNORゲートがあるとする[16]。 もしも入力Aあるいは入力BのどちらかがHigh(論理回路の1 = 真)であれば、各MOSトランジスタは出力と負電源の間で非常に低い抵抗値の抵抗としてふるまうので、出力を強制的にLow(論理回路の0 = 偽)にする。 AとBの両方がHighのとき、両方のトランジスタが導通し、グランドへのさらに低い抵抗の経路を作ることになる[16]。 出力がHighになる唯一の状態は、両方のトランジスタがオフのときである。この状態は、AとBの両方がLowのときにだけ発生する。このようにNORゲートの真理値表を満たすことになる[16]。

| A | B | A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

閾値電圧 VTは0Vよりも少しだけ高い値のことが多い。エンハンスメントモードなので、VGS ≧ 0 で使用する。 |

|

|

集積回路内部に抵抗器を作ると工数が増える[18]。MOSFETを抵抗器の代わりに使うと工数を削減できる。それを負荷トランジスタや負荷MOSFETという[19]。そのため、nチャネルMOSFETだけで回路全体を作ることができる。しかし、負荷MOSFETの電気特性は抵抗器と異なる。

負荷トランジスタ(プルアップトランジスタ)は論理スイッチとして使われるものと同種のエンハンスメントモードMOSFETである(ゲート・ソース間電圧VGSが0になるとオフになる)[20]。

図のように負荷MOSFETのゲートをどこに接続するのかで負荷の種類が異なる。負荷MOSFETのゲートをVddに接続すると飽和エンハンスメント負荷となり、Vggに接続すると線形エンハンスメント負荷となる。線形エンハンスメント負荷の方が電圧降下が少ないため出力電圧をVddに近くできるが、2電源が必要になる[11]。

回路図から負荷MOSFETの動作を決める変数は以下のようになる。

出力電圧が低下すると、VDS と一緒に VGS も増えることになる。そのため、IDS は、VDS のおおよそ2乗に比例して増えることになる。つまり出力電圧が低下すると過剰な電流が流れて消費電力が悪化する。その一方で出力電圧が増大すると電流がわずかしか流れないので、動作速度が低下する。

このように抵抗器の代わりにエンハンスメントモードMOSFETを使う方法は速度や消費電力の面で問題がある[11][21]。 それらの問題を改善するために負荷としてエンハンスメントモードトランジスタの代わりにディプリーションモードトランジスタを使うことができる[22]。 その方法を実装したものは、ディプリーション負荷NMOSロジックと呼ばれている。

MOSFETは、1959年にベル研究所のエジプト人技術者モハメド・M・アタラと韓国人技術者ダウォン・カーンによって発明された[23] 。 彼らは20μmプロセスでPMOSとNMOSのデバイスの両方を製作した。 しかしながら、NMOSデバイスは実用性がなく、PMOSデバイスだけは実用性があった[24]。

1965年にフェアチャイルドセミコンダクターのチータン・サー、オットー・リスティコ(Otto Leistiko)、そしてグローブ(Grove)は、チャネルの長さが8μmから65μmまでのいくつかのNMOSデバイスを製作した[25]。 IBMのデイル・L・クリッチロー(Dale L. Critchlow)とロバート・H・デナードも1960年代にNMOSデバイスを製造した。 IBMの最初のNMOS製品は、データ容量が1Kbitでアクセス時間が50nsから100nsの半導体メモリであった。この製品は1970年代初頭に大量生産に入った。 これによってMOSFETの半導体メモリが1970年代のバイポーラメモリと磁気コアメモリの技術を置き換えることになった[26]。

1970年代初頭の初期のマイクロプロセッサは、PMOSプロセッサであった。PMOSプロセッサは初期のマイクロプロセッサ業界を支配した[27]。 1973年に初期のNMOSプロセッサであるNECのμCOM-4は、Sohichi Suzukiが率いる5人の研究者で構成されたNECのLSIチームによって製造された[28][29]。 1970年代後半までにNMOSプロセッサは、PMOSプロセッサを追い越すことになった[27]。 1970年台中頃になると、モステックがディプリーション負荷NMOSロジックを製品化した。 速度と消費電力が改善し、NMOSはさらに進化した。インテルは自社独自のディプリーション負荷NMOSロジックにHMOSという名称をつけた。

CMOSマイクロプロセッサは、1975年に発表された[27][30][31]。 しかしながら、CMOSプロセッサは1980年代になるまで支配的な存在にならなかった[27]。 初期のCMOSはNMOSロジックよりも遅かったので、NMOSは1970年代のコンピューターにCMOSよりも広く使われた[32]。 Intel 5101(1Kbit SRAM)CMOSメモリチップ(1974)は、アクセス時間800nsであった[33][34]。その一方で当時の最速NMOSメモリチップIntel 2147(4Kbit SRAM)HMOSは、55/70nsのアクセス時間であった[34] 。

1978年にToshiaki Masuhara率いる日立製作所の研究チームは、3μmプロセスで製造されたHM6147(4Kbit SRAM)にツインウェル(twin-well)Hi-CMOSを導入した[32][35]。 日立HM6147メモリチップは、Intel 2147 HMOSメモリチップの性能(アクセス時間55/70ns)に匹敵し、Intel 2147(110mA)よりも大幅に少ない消費電力(15mA)であった[36][注釈 2]。 互角の性能とより少ない消費電力を持って、ツインウェルCMOSプロセスは1980年代のコンピューターのための最も一般的な半導体デバイス製造プロセスとしてNMOSをついに追い越した[32]。

1980年代にCMOSマイクロプロセッサは、NMOSマイクロプロセッサを追い越した[27]。

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.