Zilog Z80

microprocessore a 8 bit Da Wikipedia, l'enciclopedia libera

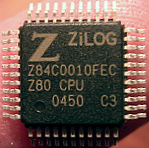

Lo Zilog Z80 è un microprocessore ad 8 bit con un design interno della ALU a 4 bit ma capace di operazioni a 8 e 16 bit[1] progettato dalla Zilog di Federico Faggin e commercializzato a partire dal luglio del 1976. Lo Z80, con i suoi derivati e i suoi cloni, è una delle famiglie di CPU più impiegate di tutti i tempi.[2]

| Zilog Z80 Central processing unit | |

|---|---|

| |

| Prodotto | 1976 |

| Progettato da | Federico Faggin, Masatoshi Shima |

| Produttore | Zilog |

| Predecessore | Intel 8080 |

| Successore | Zilog Z180, Zilog Z8000, Zilog Z800, Zilog Z280, Zilog Z380 e Zilog eZ80 |

| Specifiche tecniche | |

| Frequenza CPU | 2,5 MHz / 8 MHz |

| Microarchitettura | 8 bit |

| Socket | DIP40 |

È stato largamente utilizzato in numerosi sistemi, negli home computer, nei videogiochi arcade, nelle console, nei sistemi embedded ed anche in quelli militari;[3] insieme alla famiglia di CPU basate sul MOS 6502 ha dominato il mercato dei microcomputer e delle console giochi ad 8 bit di fine anni settanta e quello degli home computer dei primi anni ottanta.[4]

Zilog provò anche a commercializzare delle versioni per minicomputer dell'architettura Z80, lo Z800 e lo Z280, che però non riscossero il successo del loro predecessore: il primo fu abbandonato ancor prima della sua commercializzazione,[5] mentre la complessità ed i bug del secondo ne limitarono la diffusione a vantaggio di altri prodotti, fra cui l'Hitachi HD64180 e lo Zilog Z180.[6]

Con un comunicato ufficiale datato 15 Aprile 2024, la Zilog dichiara la cessazione della produzione dell'intera linea di CPU, MPU, I/O della famiglia Z80, con data di produzione dell'ultimo lotto stimata per il 15 Giugno 2024.[7][8]

Storia

Riepilogo

Prospettiva

Federico Faggin, dopo aver lavorato sull'8080, lasciò Intel alla fine del 1974 per divergenze con la dirigenza: questa, infatti, era ancora troppo focalizzata sulla produzione di chip di memoria e considerava i microprocessori solo come prodotti accessori, utili per vendere più RAM.[9] Faggin, invece, intravedeva in essi una potenzialità d'impiego molto più vasta, grazie alla loro possibilità di essere programmati per impieghi generali. Faggin decise quindi di lasciare Intel per fondare insieme al suo collega Ralph Ungermann la Zilog, una società dedita esclusivamente alla produzione di CPU.[10] Il primo prodotto della società fu proprio lo Z80, nato da un progetto che Faggin elaborò verso la fine del 1974,[11] presentato nel luglio del 1976.[12]

Lo Z80 si diffuse nel mercato dei processori molto più dell'Intel 8080 e del suo successore, l'8085[13] e divenne una delle CPU ad 8 bit più popolari.[14][15] Uno dei fattori chiave del successo iniziale dello Z80 furono i sistemi integrati nel chip stesso, come quello per il refresh della memoria DRAM: tale integrazione permetteva di realizzare sistemi completi con l'aggiunta di pochi altri componenti esterni di supporto (più in là comparvero sistemi embedded basati sullo Z80, che in genere utilizzano memorie statiche, che non necessitano di questo refresh) ed aprendo la via verso i moderni "System On Chip".

La Zilog concesse in licenza senza royalty la proprietà intellettuale del progetto del core dello Z80 a qualunque società lo avesse voluto produrre in proprio: questa politica commerciale alla lunga ripagò Zilog con un ritorno di immagine, diffusione e vendite perché permise ad un prodotto di una piccola società, quale essa era, di affermarsi sul mercato mondiale grazie al fatto che grossi produttori come Toshiba iniziarono a produrre in quantità industriali il processore.[16] Come conseguenza di questa scelta commerciale, Zilog ha prodotto meno del 50% di tutti gli Z80 costruiti in questi anni.[16] Nonostante ciò diversi produttori dell'Europa dell'Est,[3] del Giappone[16] e dell'ex Unione Sovietica[17] fabbricarono delle copie della CPU senza licenza.

Descrizione tecnica

Riepilogo

Prospettiva

Il set di istruzioni dello Z80 fu scritto per essere compatibile con l'Intel 8080,[12][18] per cui gran parte del codice per l'8080 (principalmente quello del sistema operativo CP/M) poteva girare senza modifiche sullo Z80. Masatoshi Shima (co-progettista dell'Intel 4004 e dell'Intel 8080) contribuì allo sviluppo dello Z80.[19]

Lo Z80 offriva le seguenti migliorie rispetto all'8080:[18]

- un insieme di istruzioni più completo,[20] incluse quelle per la manipolazione dei bit, lo spostamento dei blocchi di dati, l'I/O e le istruzioni per la ricerca dei byte;[21]

- nuovi registri indice IX e IY, con le relative istruzioni;

- un sistema di interrupt vettorizzati maggiormente automatizzato e generalizzato, operante in 3 modalità: il modo 2 gestiva una modalità vettorizzata indiretta, il modo 1 prevedeva una modalità diretta, valida per sistemi semplici con hardware minimale, mentre il modo 0 indicava la modalità compatibile 8080.[22]

- due banchi di registri separati, che possono essere velocemente invertiti, per velocizzare la risposta agli interrupt;

- necessità di meno hardware per l'alimentazione, la generazione del clock, l'interfaccia di memoria e l'I/O:

- richiesta di 1 singola alimentazione a 5 V (l'8080 necessita di 3 alimentazioni, rispettivamente a -5 V, +5 V e +12 V)

- clock a 5 V a singola fase (l'8080 necessita di un generatore di clock a due fasi di grande ampiezza);

- un meccanismo integrato per il refresh della memoria ad accesso diretto che altrimenti doveva essere fornito da una circuiteria esterna;

- bus dati non multiplato (l'8080 ha nel bus dati un sistema multiplato di segnali di stato);

- un prezzo più basso.

Il progetto originale in logica NMOS vide il limite massimo della frequenza del clock crescere progressivamente dai 2,5 MHz iniziali fino ai 4 MHz dello Z80A, ai 6 MHz dello Z80B ed agli 8 MHz dello Z80H.[23][24] Ne fu realizzata anche una versione CMOS con un intervallo di frequenze che andava dai 4 MHz fino ai 20 MHz delle versioni vendute più recentemente.[25][26] La versione CMOS permetteva inoltre una modalità d'attesa a basso consumo energetico denominata "Power-Down", o "modalità standby", in cui veniva mantenuto lo stato interno (registri e segnali di controllo) del processore fino al ricevimento del segnale di uscita da tale stato (un segnale di clock).[26] I chip derivati compatibili con lo Z80, l'HD64180/Z180[27][28] e l'eZ80 sono dichiarati capaci rispettivamente di 33 MHz e 50 MHz.

Modello di programmazione e gestione dei registri

Il modello di programmazione e la gestione dei registri sono convenzionali e simili a quelli della famiglia x86. I registri AF, BC, DE e HL, compatibili con quelli dell'Intel 8080, sono duplicati nello Z80 in 2 banchi separati[29] con il processore che può velocemente passare da un banco all'altro,[30] una caratteristica utile per velocizzare la risposta agli interrupt ad alta priorità e livello singolo. Questa caratteristica era presente nel Datapoint 2200, mentre non era implementata nell'Intel 8008. Il sistema dei registri doppi aveva senso sullo Z80 (e su altri microprocessori dell'epoca), perché esso era stato progettato anche per i sistemi embedded, non solo per i personal computer o per gli home computer.[31] I doppi registri risultarono molto utili per la codifica assembly altamente ottimizzata: alcuni software, specialmente i giochi per i sistemi MSX, gli ZX Spectrum ed altri computer basati sullo Z80, portarono l'ottimizzazione dell'assembly dello Z80 a livelli estremi, impiegando, tra le altre cose, proprio i registri duplicati.

Registri

Come sull'8080, i registri ad 8 bit sono di solito accoppiati per ottenerne delle versioni a 16 bit. I registri compatibili con quelli dell'8080 sono:[32]

- AF - (8 bit) accumulatore (A) e bit di flag (F) per resto, zero, segno meno, parità/overflow, semi-riporto (usato per codifica decimale), ed un flag Aggiungi/Sottrai (normalmente chiamato N), anch'esso per la codifica decimale;

- BC - (16 bit) registro dati/indirizzo oppure 2 registri ad 8 bit;

- DE - (16 bit) registro dati/indirizzo oppure 2 registri ad 8 bit;

- HL - (16 bit) registro accumulatore/indirizzo a 16 bit oppure 2 registri ad 8 bit;

- SP - (16 bit) puntatore stack;

- PC - (16 bit) contatore di programma.

I nuovi registri introdotti dallo Z80 sono:

- IX - (16 bit) registro indice o di base per offset ad 8 bit immediati o accumulatore a 16 bit;

- IY - (16 bit) registro indice o di base per offset ad 8 bit immediati o accumulatore a 16 bit;

- I - (8 bit) registro base per gli interrupt vettoriali;

- R - (8 bit) contatore per refresh della DRAM (il bit più significativo non conta);

- AF' - accumulatore alternativo (od "ombra") e flag (attivati e disattivati con EX AF,AF');

- BC', DE' e HL' - registri alternativi (od "ombra") e flag (attivati o disattivati con EXX);

- 4 bit per lo stato degli interrupt e le modalità degli interrupt.

Non c'è la possibilità di accedere direttamente ai registri alternativi: esistono per questo compito 2 istruzioni speciali, EX AF,AF' e EXX,[32] ognuna delle quali modifica 1 di 2 multiplatori flip-flop. Questo permette passaggi veloci di contesto per le routine di servizio degli interrupt: EX AF, AF' può essere utilizzata da sola (per routine di interrupt molto semplici e veloci) o in abbinamento a EXX per invertire l'intero gruppo di registri AF, BC, DE e HL, un modo di operare molto più veloce di quello basato sull'inserimento degli stessi registri nello stack (interrupt con più livelli o interrupt lenti e con bassa priorità normalmente utilizzano lo stack per memorizzare il valore dei registri).

Il registro di refresh ("R") viene incrementato[33] ogni volta che la CPU esegue un opcode (o un prefisso opcode) e non ha pertanto una relazione semplice con l'esecuzione del programma. Questo modo di operare era spesso usato per generare numeri pseudo-casuali nei giochi, ma anche in schemi di protezione software. Era anche utilizzato come contatore "hardware" in alcuni sistemi: un famoso esempio di questo utilizzo è il Sinclair ZX81, che permette di tenere traccia delle posizioni dei caratteri sullo schermo TV innescando un interrupt al verificarsi della reinizializzazione (collegando l'interrupt ad A6).

Il registro vettoriale di interrupt ("I") è usato per gli interrupt dello Z80 specificati con modalità 2 (selezionata dall'istruzione IM 2). Esso fornisce l'indirizzo di base della pagina (il "byte alto") per la tabella a 128 voci degli indirizzi degli interrupt di servizio che sono selezionati tramite un puntatore (il "byte basso" dell'indirizzo) inviato alla CPU durante un ciclo di riconoscimento degli interrupt.[22] Il puntatore identifica un particolare chip periferico e/o una funzione di un chip periferico (nel caso in cui un chip periferico possa sollevare più interrupt, come ad esempio il CTC), dove i chip sono normalmente connessi a cascata per la risoluzione della priorità. Come per quello di refresh, questo registro è stato talvolta utilizzato in maniera "creativa".

La ALU a 4 bit

La ALU, o "Arithmetic-Unit Logic", è il modulo integrato in una CPU deputato all'esecuzione dei calcoli aritmetico/logici. A differenza di altre CPU contemporanee (come il MOS 6502 o l'Intel 8080) la ALU dello Z80 è a 4 bit, vale a dire che esegue calcoli su numeri di 4 bit, o nibble. Siccome l'accumulatore della CPU è a 8 bit, per eseguire un calcolo su un numero contenuto nell'accumulatore la ALU dello Z80 deve eseguire due passaggi su tale registro. Per far sì che questo non incida sulle prestazioni della CPU, i progettisti dello Z80 hanno pensato ad un sistema di cicli interni divisi in "cicli macchina", o "cicli M" (dall'inglese M-cycle), in cui ogni ciclo M è composto da più "cicli di clock", o "stati T" (dall'inglese T-state), dove uno stato T è equivalente ad un ciclo di clock,[34], ed ottimizzando le istruzioni affinché la CPU sia in grado di eseguire un minimo di sovrapposizione delle operazioni delle singole istruzioni: questo processo è detto "fetch/execute overlapping" e permette di continuare l'esecuzione di una istruzione mentre la CPU sta leggendo dalla memoria l'opcode di quella successiva. Ad esempio, l'istruzione SUB r, che sottrae dall'accumulatore il valore contenuto nel registro ad 8 bit indicato da "r", viene eseguito in 1 ciclo M composto da 4 cicli di clock. L'esecuzione di questa istruzione più essere divisa nei seguenti singoli passaggi:

ISTRUZIONE CORRENTE "N" (SUB r)

M1 / T1 : viene impostato l'indirizzo da cui leggere l'istruzione "N" da eseguire

M1 / T2 : viene recuperata dalla memoria l'istruzione "N"

M1 / T3 : viene interpretato l'opcode come "SUB r": A viene caricato sul latch temporaneo "ACU" (*)

M1 / T4 : viene caricato il registro "r" nel latch temporaneo "TEMP" (*)

-------------

ISTRUZIONE SUCCESSIVA "N+1"

M1 / T1 : viene impostato l'indirizzo da cui leggere l'istruzione "N+1" da eseguire

contemporaneamente il nibble basso della precedente operazione viene calcolato

M1 / T2 : viene recuperata dalla memoria l'istruzione "N+1"

contemporaneamente viene calcolato il nibble alto della precedente operazione

ed il risultato viene ricomposto come valore ad 8 bit e depositato nell'accumulatore

- vedere figura relativa all'architettura interna della CPU

In tale modo lo Z80 non manifesta rallentamenti rispetto ad una CPU con una ALU interamente ad 8 bit. Ciò è anche possibile grazie al fatto che il recupero dell'istruzione dalla memoria viene sempre eseguito durante i primi stati "T" del primo ciclo M (detto M1) di una istruzione.[1][35][36][37]

Il linguaggio assembly dello Z80

Una retrospettiva - Il Datapoint 2200 e l'Intel 8008

Il linguaggio assembly del primo Intel 8008 era basato su una sintassi molto semplice (ma schematica), derivata dall'architettura del Datapoint 2200; questa sintassi fu poi trasformata in un nuovo linguaggio assembly dedicato al chip 8008; il nuovo linguaggio assembly fu poi esteso, quasi nello stesso periodo, per adattarsi alle aggiunte possibilità di indirizzamento offerte dal più evoluto chip Intel 8080 (l'8008 e l'8080 condividevano un linguaggio senza che fossero compatibili a livello di codice binario; l'8008 era invece compatibile a livello binario con il Datapoint 2200).

In questo processo di trasformazione, l'abbreviazione mnemonica "L", che stava per LOAD, fu sostituita dalle parole LOAD, STORE e MOVE, a cui erano state aggiunte altre lettere simboliche. La lettera "M", per Memory (referenziata da HL), fu trasformata da abbreviazione mnemonica a operando indipendente sintatticamente, mentre i registri e le combinazioni di registri furono indicati in maniera molto inconsistente, sia abbreviando gli operandi (ad esempio "MVI D" e "LXI H") sia usando le stesse forme mnemoniche delle istruzioni (ad esempio "LDA" e "LHLD") sia usando entrambi gli schemi contemporaneamente (ad esempio "LDAX B" e "STAX D").

| Datapoint 2200 & i8008 |

i8080 | Z80 | i8086/i8088 |

|---|---|---|---|

| ca. 1973 | ca. 1974 | 1976 | 1978 |

LBC | MOV B,C | LD B,C | MOV BL,CL |

-- | LDAX B | LD A,(BC) | MOV AL,[BX] |

LAM | MOV A,M | LD A,(HL) | MOV AL,[BP] |

LBM | MOV B,M | LD B,(HL) | MOV BL,[BP] |

-- | STAX D | LD (DE),A | MOV [DX],AL |

LMA | MOV M,A | LD (HL),A | MOV [BP],AL |

LMC | MOV M,C | LD (HL),C | MOV [BP],CL |

LDI 56 | MVI D,56 | LD D,56 | MOV DL,56 |

LMI 56 | MVI M,56 | LD (HL),56 | MOV byte ptr [BP],56 |

-- | LDA 1234 | LD A,(1234) | MOV AL,[1234] |

-- | STA 1234 | LD (1234),A | MOV [1234],AL |

-- | -- | LD B,(IX+56) | MOV BL,[SI+56] |

-- | -- | LD (IX+56),C | MOV [SI+56],CL |

-- | -- | LD (IY+56),78 | MOV byte ptr [DI+56],78 |

-- | LXI B,1234 | LD BC,1234 | MOV BX,1234 |

-- | LXI H,1234 | LD HL,1234 | MOV BP,1234 |

-- | SHLD 1234 | LD (1234),HL | MOV [1234],BP |

-- | LHLD 1234 | LD HL,(1234) | MOV BP,[1234] |

-- | -- | LD BC,(1234) | MOV BX,[1234] |

-- | -- | LD IX,(1234) | MOV SI,[1234] |

Tabella di 4 sintassi che usano esempi di istruzioni di LOAD e STORE equivalenti o (per l'8086) molto simili.[38]

La nuova sintassi

Intel dichiarò che i codici mnemonici del suo assembly erano brevettati. Fu perciò sviluppata una nuova sintassi, questa volta con un approccio più semantico:

- tutti i registri e le coppie di registri venivano indicati esplicitamente con i loro nomi interi;

- le parentesi tonde "()" venivano utilizzate coerentemente per indicare "contenuto di memoria a" (puntatore non referenziato), con l'eccezione di alcune istruzioni di salto;[39]

- Tutte le istruzioni "load" e "store" usavano lo stesso codice mnemonico,

LDper LOAD (un ritorno al vocabolario semplicistico del Datapoint 2200); altre istruzioni di uso comune (comeADDeINC) usavano lo stesso codice mnemonico, indipendentemente dal modo di indirizzamento o dalla dimensione dell'operando (ciò era possibile perché gli stessi operandi contenevano in sé abbastanza informazioni).

Queste linee guida resero semplice il compito di trovare i nomi e la sintassi di tutte le nuove istruzioni dello Z80, così come il riadattamento delle vecchie (ad esempio "LD BC,(1234)" espresso più sopra).

Dalla tabella si nota anche la somiglianza tra la sintassi dello Z80 e quella dell'Intel 8086. A parte la differenza di nomenclatura, e a dispetto di una certa discrepanza nella struttura base dei registri, le due sintassi sono virtualmente isomorfe per una larga porzione di istruzioni. Non è però certo se questa somiglianza sia dovuta alle comuni influenze avute su entrambi i gruppi di progettazione dalle CPU ante Intel 8080 (come il PDP-11), alla natura competitiva della relazione fra i due progetti o ad una questione di scelte.[40][41]

Istruzioni e codifica

Lo Z80 utilizza 252 dei 256 codici disponibili come singoli byte opcode ("root instructions", "istruzioni base"); i 4 codici rimanenti sono utilizzati estesamente come prefissi opcode:[42] CB e ED abilitano delle istruzioni aggiuntive, e DD e FD selezionano rispettivamente "IX+d" e "IY+d" (in alcuni casi senza utilizzare "d") al posto di HL. Questo schema dà allo Z80 un elevato numero di permutazioni di istruzioni e registri; Zilog le inquadrò in 158 differenti "tipi di istruzioni", 78 delle quali sono le stesse di quelle dell'8080,[42] permettendo l'esecuzione dei programmi 8080 sullo Z80.

La documentazione di Zilog raggruppa inoltre le istruzioni nelle seguenti categorie:

- operazioni aritmetiche e logiche ad 8 bit;

- operazioni aritmetiche a 16 bit;

- operazioni di caricamento ad 8 bit;

- operazioni di caricamento a 16 bit;

- operazioni sui bit (inserimento di valore 1, 0 o di test);

- operazioni di chiamata e ritorno da sottoprogrammi e riavvio da indirizzi predefiniti (restart);

- operazioni di scambio, trasferimento e ricerca dei blocchi;

- operazioni di controllo CPU e aritmetica semplice;

- operazioni di gestione dell'input/output;

- operazioni di salto;

- operazioni di rotazione e scorrimento dei bit;

Come su altri processori dell'epoca, nessuna istruzione di moltiplicazione è disponibile nell'originale Z80.[43] Le differenti dimensioni e le varianti delle operazioni di addizione, spostamento e rotazione dei bit avevano anche differenti effetti sui flag, a causa delle proprietà di influenza sui flag copiate dall'8080. Le istruzioni di caricamento non influenzavano i flag (tranne nei casi di caricamento negli speciali registri I e R). Le istruzioni sui registri indice erano utili per ridurre la dimensione del codice e, anche se alcune di esse non erano molto più veloci delle "equivalenti" sequenze composte dalle semplici operazioni, esse permettevano di ridurre indirettamente il tempo di esecuzione, diminuendo il numero di istruzioni necessarie per salvare e ripristinare i registri.[44][45] Similarmente, le istruzioni per le addizioni a 16 bit non erano particolarmente veloci nell'originale Z80 (11 cicli); comunque esse erano circa due volte più veloci se paragonate alle operazioni ad 8 bit alle prese con gli stessi calcoli e inoltre riducevano l'utilizzo dei registri.

Istruzioni non documentate

I registri indice IX e IY erano stati pensati come puntatori a 16 bit flessibili per migliorare l'abilità di manipolare la memoria, le strutture di dati e gli stack. Ufficialmente essi erano gestiti solo come registri a 16 bit, ma in realtà erano implementati come una coppia di registri ad 8 bit,[46] alla stessa maniera del registro HL, che era accessibile sia integralmente a 16 bit sia nei suoi singoli registri ad 8 bit "High" e "Low". Ugualmente i codici opcode (linguaggio macchina) erano identici ma preceduti da un nuovo prefisso opcode.[47]

Zilog pubblicò gli opcode ed i relativi codici mnemonici per le funzioni illustrate, ma non documentò il fatto che ogni opcode che permetteva la manipolazione dei registri H e L era ugualmente valido per le porzioni ad 8 bit dei registri IX e IY. Un esempio è l'opcode 26h seguito immediatamente da un byte (LD H,n), che caricherà quel valore nel registro H. Precedendo questa istruzione a 2 byte con il prefisso opcode per il registro IX si avrà il caricamento di quel valore negli 8 bit più significativi del registro IX. Un'importante eccezione a questo modo di operare è data dalle istruzioni simili a LD H,(IX+d) che fanno uso sia del registro HL sia di IX, o di IY, nella stessa istruzione:[47] in questo caso il prefisso DD si applica solo alla porzione "(IX+d)" dell'istruzione.

Inoltre ci sono diverse altre istruzioni non documentate.[48] Alcune di esse sono la conseguenza dei diversi progetti iniziali del chip mentre altre fanno riferimento ad aree molto esterne del die con un elevato tasso di malfunzionamento, motivo per il quale è stato deciso di non documentarle.[49]

Esecuzione delle istruzioni

Ogni istruzione è eseguita in passaggi che sono di solito indicati come cicli macchina (o M-cycles), dall'inglese "machine cycles", ognuno dei quali può richiedere da 3 a 6 cicli clock (o T-states).[50] Ogni ciclo M corrisponde approssimativamente ad un accesso alla memoria e/o ad un'operazione interna. Molte istruzione terminano effettivamente durante il ciclo M1 dell'istruzione successiva, condizione nota come fetch/execute overlap.

Esempi di istruzioni tipiche (R=read, lettura - W=write, scrittura):

I cicli M dello Z80 sono gestiti da una macchina a stati finiti interna che costruisce ogni ciclo a partire da 3, 4, 5 o 6 cicli di clock (T-state), a seconda del contesto. Questo meccanismo evita di dovere usare un'ingombrante logica asincrona e fa sì che i segnali di controllo si comportino in modo coerente all'interno di una vasta gamma di frequenze di clock. Ciò significa anche che va usato un clock con una frequenza superiore rispetto a quello che si userebbe nella situazione in cui questa suddivisione dei cicli macchina non esistesse (approssimativamente 2-3 volte superiore).

Questo non implica però la necessità di usare una memoria con dei tempi di accesso migliori, in quanto un clock con una risoluzione più elevata permette un controllo più preciso dei timing della memoria e la stessa può essere attiva in parallelo con la CPU per un margine più ampio (cioè registra meno idle), permettendo un uso più efficiente delle sue prestazioni. Parlando di esecuzione delle istruzioni, lo Z80 combina 2 cicli di clock completi in un lungo periodo di accesso alla memoria (il segnale M1), che generalmente dura solo una frazione di un (più lungo) ciclo di clock, in una specie di design più asincrono (tipo il Motorola 6800 o altre CPU simili).

Le memorie erano di solito troppo lente (soprattutto quelle di tipo EPROM, ma anche le Flash) se paragonate ai sotto-cicli (i cicli di clock) delle macchine a stato finito usate nei processori contemporanei. Il ciclo macchina più breve che poteva essere usato nei progetti embedded era spesso limitato dai tempi di accesso della memoria, non dalla massima frequenza della CPU (specialmente durante l'era degli home computer). Questa relazione è però cambiata leggermente durante gli ultimi decenni, particolarmente per quanto riguarda le SRAM; senza cache, i disegni a ciclo singolo come l'eZ80 sono pertanto divenuti recentemente molto più importanti.

Periferiche compatibili

Zilog introdusse un certo numero di periferiche per lo Z80, tutte supportanti il sistema di gestione degli interrupt e lo spazio di indirizzi I/O della CPU. Queste includevano il "CTC" (Counter-Timer-Circuit), il "SIO" (Serial Input Output), il "DMA" (Direct Memory Access), il "PIO" (Parallel Input-Output) ed il "DART" (Dual Asynchronous Receiver Transmitter). Col tempo, di questi chip furono offerte anche versioni in tecnologia CMOS, che offrivano un consumo energetico più basso unito ad una velocità superiore.

Come i processori Intel 8085 e 8086, ma non come i processori Motorola 6800 e MOS 6502, lo Zilog Z80 e l'Intel 8080 avevano per le istruzioni che riguardavano l'I/O una linea di controllo ed uno spazio d'indirizzi separati. Nonostante alcuni computer basati sullo Z80 (come l'Osborne 1) utilizzassero dei dispositivi di I/O mappati in memoria, in genere lo spazio I/O era utilizzato per indirizzare uno dei molti chip periferici di Zilog compatibili con lo Z80: i chip di I/O di Zilog supportavano gli interrupt in modo 2 dello Z80 (vedi sopra), che semplificava la gestione degli stessi per un gran numero di periferiche.

Indirizzamento I/O a 16 bit "non documentato"

Lo Z80 veniva indicato ufficialmente come capace di supportare l'indirizzamento della memoria a 16 bit (massimo 64 kB) e l'indirizzamento I/O ad 8 bit (massimo 256 porte), ma leggendo il manuale hardware di riferimento si poteva notare come tutte le istruzioni di I/O potessero gestire l'intero bus indirizzi a 16 bit: OUT (C),reg e IN reg,(C) inseriscono l'intero contenuto del registro BC nel bus indirizzi;[56] OUT (n),A e IN A,(n) inseriscono il contenuto del registro A nei bit b8-b15 del bus indirizzi e di n nei bit b0-b7 del bus indirizzi. Un progettista poteva scegliere se decodificare l'intero bus indirizzi a 16 bit sulle operazioni di I/O, così da avvantaggiarsi di questa caratteristica, oppure usare i bit più alti del bus indirizzi (b8-b15) per selezionare delle sotto-caratteristiche del dispositivo di I/O. Questa peculiarità è stata usata anche per minimizzare i requisiti hardware di decodifica, come negli Amstrad CPC e nello ZX81.

Copie su licenza, cloni e derivati

Riepilogo

Prospettiva

Cloni

Il Mostek MK3880 e l'SGS-Thomson (ora STMicroelectronics) Z8400 erano entrambi copie ufficiali dello Z80. Sharp e NEC svilupparono dei cloni in tecnologia NMOS, rispettivamente l'LH0080 e il µPD780C. Toshiba ne realizzò una versione CMOS, il TMPZ84C00, che è ritenuto essere lo stesso processore dello Zilog Z84C00, anch'esso in CMOS. Ci furono anche chip Z80 realizzati da GoldStar (poi LG), così come la serie BU18400 dei cloni Z80 (inclusi i chip DMA, PIO, CTC, DART e SIO) in tecnologia NMOS e CMOS realizzati da ROHM Electronics.

Nella Germania dell'Est comparve un clone senza licenza dello Z80, noto come U880: fu utilizzato nei computer realizzati da VEB Robotron e VEB Mikroelektronik Mühlhausen, come la serie KC 85, ma anche per computer auto-assemblati come il COMP JU+TER. In Romania era diffuso un altro clone senza licenza, l'MMN80CPU di Microelectronica, utilizzato negli home computer (quali il TIM-S, l'HC ed il COBRA).

Diversi cloni dello Z80 furono realizzati anche nell'Unione Sovietica; uno di questi era il T34VM1,[25] chiamato anche КP1858VМ1[17] (realizzato parallelamente al clone russo dell'8080, il KR580VM80A): il primo doveva essere usato nelle serie di pre-produzione, mentre il secondo doveva essere utilizzato per le produzioni in larga scala, anche se, a causa del collasso dell'industria microelettronica sovietica di fine anni ottanta, esistono più T34VM1 che КP1858VМ1.

- Il MOSTEK MK3880N-4, un clone dello Z80.

- Il NEC µPD780C, un clone dello Z80.

- Lo Sharp LH0080, un clone dello Z80.

Derivati

- Compatibili con lo Z80 originale

- Hitachi sviluppò l'HD64180, un microcodificato e parzialmente dinamico Z80 in CMOS, con le periferiche montate su chip ed una semplice MMU, che gestiva uno spazio indirizzi di 1 MB. Questo chip fu poi realizzato anche da Zilog, inizialmente come Z64180 e poi come Z180,[57] che ha il protocollo del bus ed i timing adattati meglio ai chip periferici dello Z80. Zilog ha continuato a produrre lo Z180 e a migliorarlo: le nuove versioni si chiamano Z8S180/Z8L180, e hanno core pienamente statici, con bassi consumi energetici e ridotte interferenze elettromagnetiche (EMI, elimination of electromagnetic interference).[58]

- Toshiba sviluppò le serie di controller intelligenti Z84013/Z84C13 (a 84 pin), e Z84015/Z84C15 (a 100 pin), in pratica dei core Z80 con le sue periferiche in tecnologia NMOS e CMOS, con un temporizzatore di supervisione, funzione di POR ("Power-On-Reset") e generatore di stati d'attesa, tutto sullo stesso chip. Essi furono fabbricati anche da Sharp. Questi processori sono oggi assemblati anche da Zilog.[59]

- Lo Zilog Z380, un chip a 32 bit compatibile con lo Z80, introdotto nel 1994, è sopravvissuto durante questi anni; è usato principalmente nei dispositivi per le telecomunicazioni.

- Lo Zilog eZ80, pienamente compatibile con lo Z80[60] con word di 8/16/24/32 bit ed uno spazio indirizzi lineare di 16 MB; è stato introdotto nel 2001. Esiste in diverse versioni, con SRAM o memoria flash integrata, così come con le periferiche montate su chip. Una variante integra su chip un MAC e il software a corredo include uno stack IP. A differenza dello Z800 e dello Z280, presenta solo qualche istruzione aggiuntiva (di cui le principali riguardano i metodi di indirizzamento e quelle per caricare i registri in memoria, con indirizzo variabile a 16/24 bit); rispetto allo Z80, esegue le istruzioni da 2 ad 11 volte più velocemente (con un valore medio di 3-5 volte). È certificato per frequenze di clock fino a 50 MHz.

- Kawasaki produsse il KL5C8400, compatibile a livello binario con lo Z80, di cui risulta mediamente 1,2-1,3 volte più veloce e può operare con clock fino a 33 MHz. Kawasaki produsse anche la famiglia KL5C80A1x, con le periferiche ed una piccola memoria RAM integrata nel chip: è efficiente approssimativamente quanto l'eZ80 e può operare fino a 10 MHz (2006).[61]

- Alcune famiglie di processori multimediali del costruttore cinese Actions Semiconductor, come l'ATJ2085 ed altri chip, contengono una MCU compatibile con lo Z80 insieme ad un processore DSP dedicato a 24 bit.[62] Questi chip sono utilizzati in molti lettori MP3 e multimediali.

- Non compatibili

- La serie di microcontrollori Toshiba TLCS-900 (principalmente PROM) sono basati sullo Z80, condividendo con questo la struttura base dei registri suddivisi in BC, DE, HL, IX, IY e gran parte delle stesse istruzioni, ma non sono compatibili a livello binario, al contrario della precedente famiglia TLCS 90.[63]

- La serie di microcontrollori NEC 78K è basata sullo Z80: essi condividono la stessa struttura base dei registri BC, DE, HL e istruzioni simili (ma con nomi differenti). Non sono compatibili a livello binario con lo Z80.

- Parzialmente compatibili

- I microprocessori/microcontroller Rabbit Semiconductor 2000/3000/4000[64] sono basati sull'architettura HD64180/Z180, anche se non sono pienamente compatibili a livello binario.[65]

Non più in produzione:

- L'R800 prodotto da ASCII Corporation fu un veloce processore a 16 bit utilizzato nei computer MSX Turbo R: era compatibile con lo Z80 a livello software ma non a livello hardware (i timing dei segnali, la disposizione ed i segnali dei pin differivano dallo Z80).

- Gli Z800, in tecnologia NMOS, e Z280, in tecnologia CMOS, furono implementazioni più veloci dello Z80 (prima dell'arrivo dell'HD64180/Z180), con una MMU capace di gestire uno spazio indirizzi di 16 MB; essi aggiungevano molte variazioni e modalità di indirizzamento al set di istruzioni originali dello Z80. Il primo non fu neanche messo in commercio mentre il secondo non riuscì ad imporsi a causa della sua eccessiva complessità e perché era stato progettato più per l'uso nei minicomputer che nei sistemi embedded.[6][66] Per contro lo Z80 in versione CMOS era rimasto popolare, a fianco delle famiglie compatibili Z180 ed eZ80.

- Lo Z280 in formato PLCC.

Versioni FPGA e ASIC

L'Evatronix CZ80CPU è un core per CPU equivalente allo Z80,[67] disponibile come codice sorgente Verilog o VHDL per i diffusi ASIC o come sorgente EDIF di netlist per i FPGA da Actel, Altera, Lattice o Xilinx.

Versioni libere sono il T80[68] ed il TV80,[69][70] disponibili come sorgenti VHDL e Verilog sotto una licenza in stile BSD o LGPL.[71] La versione in VHDL, una volta sintetizzata, può essere impostata fino a 35 MHz su un FPGA Spartan II di Xilinx.[68] Per produzioni su larga scala è comunque più conveniente utilizzare una soluzione tradizionale (o ASIC) piuttosto che un FPGA.

Emulazione software

Gli emulatori software degli Z80 girano oggi sui moderni PC molto più velocemente di quanto facesse la CPU Z80 originale: essi sono utilizzati per simulare gli home computer basati sullo Z80 (come l'Amstrad CPC, l'MSX ed il Sinclair ZX Spectrum), o console come il ColecoVision, ma anche negli emulatori di videogiochi (come il MAME) per eseguire i vecchi arcade. Il SIMH emula il computer MITS Altair 8800 sia con processore 8080 che Z80.

Impiego

Riepilogo

Prospettiva

Negli home computer

Durante la fine degli anni settanta e i primi anni ottanta lo Z80 fu utilizzato in un gran numero di macchine da ufficio basate sul sistema operativo CP/M, una combinazione che dominò il mercato di quel tempo.[72][73]

Due esempi di macchine da ufficio basate sul binomio Z80+CP/M furono il portatile Osborne 1 e la serie Kaypro. Research Machines realizzò i microcomputer 380Z (1977) e LINK 480Z (1981): quest'ultimo è dotato di un'interfaccia di rete proprietaria CHAIN (tipo Ethernet) per il collegamento ad una LAN. Se sulla LAN era presente un file server, il computer poteva avviare da esso un sistema operativo usando il CP/NOS (una versione solo-rete del CP/M), altrimenti poteva avviare il CP/M da un disco e poi accedere ai servizi di rete tramite CP/NET. Altri costruttori di tali sistemi furono TeleVideo, Xerox (serie 820) e un gran numero di altre società più o meno conosciute. Alcuni sistemi utilizzavano un multitasking software per distribuire un processo fra diversi utenti.

Il Commodore 128 integra a fianco del MOS 8502 un processore Z80, grazie al quale può entrare in una particolare modalità compatibile con il CP/M.[74][75] Altri computer basati sul MOS 6502 in vendita a quel tempo, come il BBC Micro e l'Apple II,[76] o basati sul MOS 6510, come il Commodore 64,[77] possono usare lo Z80 alloggiato su un'unità esterna, una scheda aggiuntiva o una cartuccia di espansione, come la SoftCard di Microsoft per l'Apple II: essa era una scheda aggiuntiva particolarmente diffusa e uno dei pochi prodotti hardware realizzati da Microsoft a quel tempo.

Acer, all'epoca Multitech, introdusse il Microprofessor I nel 1981, un dispositivo per l'apprendimento del linguaggio macchina dello Z80. Nel 2019 è ancora prodotto e venduto da Flite Electronics Int. (Southampton, Inghilterra) come "Flite's MPF-1B".[78] Un altro microcomputer con finalità didattiche basato sullo Z80 è l'NBZ80 o Nanocomputer, prodotto dall'azienda italiana SGS-ATES intorno al 1979.

Lo Z80 fu usato nella famiglia di home computer prodotti da Sinclair. Il Sinclair ZX80 integra uno Z80 oppure lo μPD780C-1, un clone del processore prodotto da NEC. Questo computer, presentato nel 1980, integra 1 kB di RAM e 4 kB di ROM, contenenti il sistema operativo e il linguaggio di programmazione Sinclair BASIC. Il Sinclair ZX81, presentato nel 1981, era un'evoluzione del precedente, rispetto al quale utilizza uno Z80A e integra 8 kB di memoria ROM. Come lo ZX80, anche lo ZX81 delega alla CPU Z80 la generazione del segnale video. L'erede dello ZX81 fu il Sinclair ZX Spectrum, basato anch'esso sullo Z80A, ma con un hardware migliore: lo ZX Spectrum può infatti contare su più RAM (16 kB o 48 kB, a seconda delle versioni), un interprete BASIC più completo (residente su 16 kB di ROM) e grafica a colori.

I computer costruiti seguendo lo standard MSX, sviluppato da Kazuhiko Nishi, presidente della società giapponese ASCII Corporation, erano basati su uno Z80 a 3,58 MHz. L'architettura MSX deriva da quella dei computer di Spectravideo, una società americana che commercializzava dei sistemi realizzati in collaborazione proprio con ASCII Corporation. Nishi ottenne la licenza dei computer di Spectravideo e ne rivide l'hardware, creando uno standard che chiamò MSX.[79] A livello di hardware i sistemi MSX erano distribuiti con 16/64 KB di RAM, un processore grafico TMS9918 e un processore audio AY-3-8910.

- La scheda madre del Commodore 128: lo Z80 è il secondo chip più grande in basso a destra.

- Il Microprofessor I, un mini computer didattico basato sullo Z80.

- L'Osborne 1, uno dei primi computer basati sullo Z80.

- Il Sinclair ZX80, uno dei primi home computer basati sullo Z80.

- La scheda madre del Sinclair ZX81: si noti al centro il clone dello Z80, il chip marchiato "NEC D780C-1".

- La scheda madre del Sinclair ZX Spectrum, con lo stesso clone dello Z80 del Sinclair ZX81.

- Il Kaypro II (1984), un diffuso personal computer trasportabile con sistema operativo CP/M e CPU Z80.

- Il Research Machines 380Z, un altro computer basato sul binomio CP/M-Z80.

- L'SVI-328, prodotto dalla Spectravideo e da cui sono derivati i computer MSX.

- Il Philips VG-8020, uno dei computer compatibile MSX, standard basato sullo Z80.

Nei sistemi embedded e nell'elettronica di consumo

Lo Zilog Z80 è stato a lungo un microprocessore molto diffuso nei sistemi embedded e nei microcontroller[32] dove è stato largamente utilizzato fino ai primi anni 2000,[14][80] sostituito dal suo successore eZ80. Di seguito sono illustrati alcuni usi dello Z80, inclusi i prodotti dell'elettronica di consumo.

Utilizzo industriale/professionale

- Apparecchiature da ufficio (quali fax, segreterie telefoniche e fotocopiatrici) usano spesso lo Z80.

- Controller PLC industriali utilizzano lo Z80 in moduli CPU per le funzioni ausiliarie quali l'I/O analogico, o in moduli di comunicazione.

- È anche usato in robotica, ad esempio per il riconoscimento vocale[81] e nella sintesi vocale (ad esempio, nel processore M8950 del 1981 di CSELT) e in compiti di basso livello, come unità di controllo dei servomeccanismi per selezionare e posizionare i meccanismi (anni novanta).

- I multiplexer RS232 che collegano un gran numero di "terminali" in vecchio stile ai minicomputer o ai mainframe utilizzavano matrici schede Z80 CPU/SIO.

- Lo Z80 è stato usato anche nei mixer video usati nelle emittenti TV per operazioni di modifica video in sistema real-time (anni ottanta).[82]

- È stato usato anche nei dischi rigidi di Seagate Technology e di altri produttori come controller.

- I terminali per le carte di credito delle pompe di benzina in America utilizzavano la CPU Z80 ed i chip PIO (Brevetti USA 4930665, 4962462 e 5602745).

- Diverse schede di espansione per PC, come le schede SCSI di Adaptec, hanno utilizzato lo Z80/Z180 ed i loro chip periferici.

- I processori Z80/Z180/Z380 sono stati utilizzati in apparecchiature per le telecomunicazioni come i commutatori telefonici ed i modem.

- Il commutatore di messaggi di Stofor, utilizzato ampiamente dalle banche e dagli agenti di borsa inglesi negli anni ottanta, era basato sullo Z80.

- Dispositivi per la domotica, come i controller wireless degli impianti di annaffiatura o le reti senza fili, usano il sistema open source N8VEM.

- Alcuni etilometri, come l'Intoxilyzer 5000EN, utilizzano una coppia di Z80 (anni 2000).[83]

Elettronica di consumo

- Diverse calcolatrici scientifiche hanno usato lo Z80, incluse la TI-73[84] (1998), la TI-81[85] (1990), la TI-82[86] (1993), la serie TI-83[87] (1996), la serie TI-84[88] (2004), la TI-85[89] (1995) e la serie TI-86[90] (1997) di Texas Instruments.[91]

- Tutti i lettori multimediali S1 MP3 sono basati sul core Z80 (anni 2000).[92]

- Lo Z80 è stato usato spesso anche nei videogiochi arcade,[14] sia come CPU, sia come coprocessore audio o video. Il gioco Pac-Man (1980) utilizza un singolo Z80 come CPU.[93][94] Galaxian (1979) ed i giochi arcade come King & Balloon (1980) e Check Man (1982) che usano la scheda madre Namco Galaxian utilizzano tutti lo Z80 come CPU principale.[95] Altri giochi Namco come Galaga (1981) e quelli che utilizzano la scheda madre Namco Galaga, tra cui Bosconian (1981), Dig Dug (1982), Xevious (1982) e Super Xevious (1984), utilizzano 3 processori Z80 in parallelo per la CPU, la gestione della grafica e del suono.[96] La scheda madre Jaleco Master System 32, utilizzata per diversi arcade, utilizza uno Z80 per la gestione del sonoro.[97]

- Lo Z80 fu usato anche in alcune console giochi come la ColecoVision (1982),[98] il Sega Master System (1985)[99] e il Sega Game Gear (1990), come coprocessore audio nel Sega Mega Drive (1988) e come controller audio e coprocessore del Motorola 68000 nel Neo Geo di SNK (1990).

- I sistemi gioco portatili Game Boy (1989) e Game Boy Color (1998) di Nintendo usavano un processore derivato dallo Z80[100] con un insieme di istruzioni leggermente differente (i registri indice ed il set di registri alternativi mancavano, ma erano state aggiunte le modalità di indirizzamento con incremento/decremento automatico), prodotto da Sharp Corporation. Il Game Boy Color è capace di raddoppiare il clock della CPU quando esegue software specifico per questo modello. La serie Game Boy Advance (2001) originariamente includeva questo Z80 modificato per motivi di retrocompatibilità, ma in seguito questa CPU fu eliminata quando fu presentato il Game Boy Micro.

- In Russia lo Z80 e i suoi cloni furono usati largamente in telefonia nelle linee telefoniche terrestri con Caller ID.

- Una calcolatrice Texas Instruments serie TI-86.

- La console ColecoVision è basata su uno Z80A.

- Il Sega Master System, un'altra console basata sullo Z80.

- La scheda madre per giochi arcade Jaleco Master System 32 utilizza uno Z80 per gestire il suono.

- Scheda madre del Neo Geo AES: lo Z80 è il chip rettangolare sotto al connettore centrale.

Strumenti musicali e altro

- Alcuni sequencer MIDI come l'E-mu 4060 Polyphonic Keyboard and Sequencer (1977)[101] ed il Roland MSQ700 (1984)[102], erano costruiti intorno allo Z80.

- Anche alcuni controller e commutatori MIDI, come il Waldorf Midi-Bay MB-15, usavano lo Z80 (1990).[103]

- Alcuni sintetizzatori analogici polifonici integravano lo Z80 come scanner della tastiera (ma anche per gestire le manopole delle impostazioni, i display e altro) e nei convertitori D/A o nei controlli PWM dei livelli analogici; nei sistemi più recenti è stato usato alle volte per gestire le comunicazioni tra i dispositivi MIDI. Lo Z80 è stato spesso utilizzato anche per generare il suono, implementando un oscillatore a bassa frequenza o un sintetizzatore. Alcuni esempi sono:

- i sintetizzatori Prophet 5 (1978), Prophet 10 (1980),[104] Prophet 600 (1982), Six-Trak (1984), Multitrak (1985), MAX (1984) e Split-8 (1985) di Sequential Circuits;[105]

- il sintetizzatore a 6 voci MemoryMoog (1982);[106]

- il sintetizzatore ad 8 voci Oberheim OB-8 (1983) con MIDI;[105]

- il sintetizzatore ad 8 voci Roland Jupiter-8 (1981).[107]

- Sintetizzatori/campionatori digitali come l'E-MU Emulator I (1981), l'Emulator II (1984) ed il campionatore a 12 bit Akai S700 (1987).[108]

- Drum machine come l'E-mu SP-12 (1985), l'E-mu SP-1200 (1987), l'E-mu Drumulator (1983) ed il Drumtraks (1984) di Sequential Circuits usavano i processori Z80.[105]

- Molti riverberatori digitali della Lexicon di fine anni ottanta (PCM70, LXP15, LXP1, MPX100) usavano uno o più Z80 per l'interfaccia utente e l'oscilloscopio a bassa frequenza; le funzioni sul segnale digitale erano poi eseguite da hardware dedicato.

- Il preamplificatore per chitarra con controller MIDI a valvole ADA MP-1 (1988) usava lo Z80.[109]

- Il preamplificatore per chitarra con controller MIDI a valvole MESA BOOGIE Triaxis (1991) usa lo Z80.

- Il Roland Jupiter-8, un sintetizzatore analogico del 1981, utilizzava lo Z80.

- L'E-mu SP-1200 è una drum machine e campionatore che usava lo Z80.

- Il Sequential Circuits Prophet 5, un sintetizzatore che impiegava lo Z80

Note

Bibliografia

Voci correlate

Altri progetti

Collegamenti esterni

Wikiwand - on

Seamless Wikipedia browsing. On steroids.