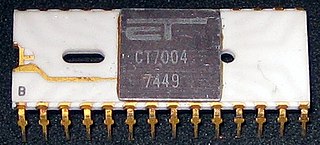

Logica PMOS

tipo di elettronica digitale Da Wikipedia, l'enciclopedia libera

La logica PMOS utilizza transistori a effetto di campo metallo-ossido-semiconduttore (MOSFET) con drogaggio di tipo P per implementare circuiti logici e altri circuiti digitali. I transistor PMOS operano creando uno strato di inversione in un substrato di tipo N. Questo strato di inversione, chiamato canale P, può condurre delle lacune tra i terminali source e drain di tipo P.

Il canale P viene creato applicando una tensione elettrica sul terzo terminale, che prende il nome di gate. Come gli altri MOSFET, i transistor PMOS hanno tre modi di operare: in zona di interdizione, in zona di triodo e in zona di saturazione.

La logica PMOS è semplice da progettare e costruire (un MOSFET può essere creato per operare come un resistore, quindi l'intero circuito può essere costruito a partire da transistor a effetto di campo di tipo PMOS), ma ciò comporta anche diversi difetti. Il problema peggiore è dato dalla presenza di una corrente continua che attraversa una porta logica PMOS quando la rete di pull-up è attiva, ossia ogni volta che l'uscita è alta, e ciò comporta una dissipazione di potenza statica anche quando il circuito è a riposo.

Inoltre i circuiti PMOS sono lenti nella transizione da segnale alto a basso. Quando effettuano la transizione da basso ad alto, i transistor forniscono una bassa resistenza, e la carica capacitiva in uscita si accumula molto velocemente (come quando si carica un condensatore attraverso una resistenza molto piccola). Ma la resistenza tra l'uscita e il terminale negativo di alimentazione è molto più grande, perciò la transizione alto-basso dura molto di più (come quando si scarica un condensatore attraverso una resistenza grande). L'impiego di un resistore di valore più basso velocizzerà il processo, ma incrementerà di contro la dissipazione di potenza statica. Come se non bastasse, i livelli degli ingressi logici asimmetrici rendono i circuiti PMOS sensibili al rumore.[1]

La maggior parte dei circuiti integrati PMOS richiedono un'alimentazione tra i 17 e i 24 volt in corrente continua.[2] Il microprocessore di tipo PMOS Intel 4004, tuttavia, utilizzava una logica PMOS in polisilicio anziché con porte metalliche, consentendo un differenziale di tensione. Per avere una compatibilità con i segnali TTL, l'Intel 4004 prevedeva una tensione di alimentazione positiva VSS=+5V ed una tensione di alimentazione negativa VDD = -10V.[3]

Sebbene fosse inizialmente più semplice da costruire,[4] la logica PMOS venne in seguito soppiantata dalla logica NMOS, che impiega transistor con canale N ed è più veloce. I moderni circuiti integrati sono invece realizzati con la logica CMOS, che utilizza sia transistor con canale N sia transistor con canale P.

Porte logiche

I MOSFET di tipo P sono sistemati in una cosiddetta "rete di pull-up" (in inglese pull-up network, PUN) tra la porta logica di uscita e la tensione di alimentazione positiva, mentre un resistore è collocato tra la porta logica di uscita e la tensione di alimentazione negativa. Il circuito è progettato in maniera tale che se l'uscita desiderata è alta, allora la rete sarà attiva, creando un percorso di corrente tra l'alimentazione positiva e l'uscita.

Le porte PMOS hanno lo stesso posizionamento delle porte NMOS gates se le tensioni di alimentazione sono invertite.[4] Pertanto, per la logica attiva-alta, le leggi di De Morgan dimostrano che una porta NOR PMOS ha la stessa struttura di una porta NAND NMOS (e viceversa).

|

|

|

Note

Bibliografia

Wikiwand - on

Seamless Wikipedia browsing. On steroids.