System-on-a-Chip

Art von integrierter Schaltkreis; Integration von Funktionen eines Systems auf einem Chip Aus Wikipedia, der freien Enzyklopädie

Ein System-on-a-Chip, auch System-on-Chip (SoC, dt. Ein-Chip-System), ist ein integrierter Schaltkreis (IC), in welchem eine Vielzahl von Funktionen eines programmierbaren elektronischen Systems realisiert ist. Als System wird dabei eine Kombination unterschiedlicher Elemente (logische Schaltungen, Taktgebung, selbständiges Anlaufen, mikrotechnische Sensoren usw.) aufgefasst, die zusammen eine bestimmte Funktionalität bereitstellen, beispielsweise einen Beschleunigungssensor samt Auswertungselektronik. Im Gegensatz zu einem elektronischen Schaltkreis auf einer Leiterplatte sind bei einem SoC alle Funktionen direkt auf dem Die, also dem Halbleiter-Substrat integriert, was auch monolithische Integration genannt wird. Aufgrund der häufigen Nutzung von Silizium als Substratmaterial spricht man auch von System-on-Silicon (SoS). Ursprünglich wurden SoCs vorrangig in eingebetteten Systemen eingesetzt, finden sich inzwischen aber in fast allen Geräteklassen, vom Smartphone bis zum Desktop-Computer.

Während Systeme anfänglich aus einem Mikroprozessor- oder Mikrocontroller-IC und vielen anderen ICs für spezielle Funktionen bestanden, die auf einer Platine aufgelötet waren, lässt die heute mögliche Integrationsdichte zu, nahezu alle Funktionen auf einem einzigen IC zu vereinigen. Dabei werden digitale, analoge und Mixed-Signal-Funktionseinheiten integriert. Vorteile sind vor allem Kosteneinsparung, geringerer Energieverbrauch beziehungsweise Verlustleistung und umfassende Miniaturisierung. So ist heute beispielsweise bei Mobiltelefonen die digitale Funktion, gegebenenfalls mit Ausnahme des Speichers, auf einem IC realisiert. Auch die Schnittstellen beispielsweise zur Tastatur, zur SIM-Karte oder zum Display sind bereits auf diesem IC enthalten.

Eine ähnliche Technik, um hohe Integrationsdichten auch von Bauelementen von stark unterschiedlicher Technik zu erreichen, ist das sogenannte System-in-Package (SiP). Dabei werden mehrere Chips (z. B. CPU und RAM) in einem Gehäuse zusammengefasst. Durch die weitere Hinzunahme von Peripheriebausteinen entstehen Leiterplatten mit komplexen Funktionen, die System on Module genannt werden.

Einsatzgebiet

Eingesetzt werden SoCs unter anderem in mobilen Geräten wie Smartphones, Tablet-Computer, sonstige Gadgets und Datenerfassungsgeräte, ebenso in der Steuerungs- und Automatisierungstechnik (z. B. Waschmaschine, Automobilelektronik, Industrieautomation) sowie in zahlreichen modernen Geräten der Unterhaltungselektronik. Meist sind viele verschiedene Schnittstellen zu bedienen (Sensoren, Aktoren, Netzwerke, Tasten, Anzeigen) und die Stückzahlen sind groß. Die Integration der Funktionen, die zuvor auf mehrere Bauelemente oder gar mehrere Leiterplatten verteilt waren, kann auch die Ausfall- und die Funktionale Sicherheit erhöhen, insbesondere wenn vielfältige Maßnahmen zur Fehleraufdeckung integriert sind, die mit diskreten Bauteilen nicht marktfähig zu realisieren wären. Für Anwendungen, die weniger große Stückzahlen generieren, wie in medizintechnischen Geräten oder der Avionik, werden selten speziell angepasste SoCs eingesetzt, sondern bleiben oft viele der integrierten Module ungenutzt.

Entwurfsvorgang

Zusammenfassung

Kontext

SoCs werden heute zumeist nicht völlig neu entwickelt, sondern die Entwürfe basieren – zumindest in Teilen – auf vorhandenen oder erworbenen Komponenten, sogenannten IP-Kernen. Dies sind beispielsweise Makros für vollständige CPU-Kerne, oder Koprozessoren – etwa als Hardwarebeschleuniger für Verschlüsselungs- oder Grafikberechnungen. Ebenso sind dies Peripherieblöcke zur Implementierung von Speicher-, Ethernet-, Bluetooth- oder sonstigen Schnittstellen, oder auch komplette Speichereinheiten inklusive deren Verwaltung.

Viele Standardkomponenten sind bei EDA-Werkzeugen der Chip-Hersteller in proprietärer Form kostenlos enthalten. Andere Komponenten können vom Chip-Hersteller oder anderen IP-Lieferanten wie z. B. ARM, Transmeta oder kleineren oft sehr spezialisierten Entwicklungsunternehmen lizenziert werden. Oftmals lassen sich solche IP-Kerne über Parameter dem Verwendungszweck angepasst generieren, beispielsweise in Form der Pipelinelänge, der Cachegröße oder den Busbitbreiten.

Weitere benötigte Komponenten eines SoC wurden beispielsweise bereits in früheren Projekten entwickelt und können im Idealfall direkt eingesetzt werden – oder es müssen Änderungen vorgenommen werden, bestenfalls genügt eine Parametrisierung der IP-Kerne. Eine weitere Möglichkeit ist das Verwenden „freier Hardware“. So entstehen auch im Hardwarebereich immer mehr Open-Source-Projekte (z. B. auf OpenCores.org), die sich oft noch im Entwicklungsstadium befinden. Was hier gegebenenfalls fehlt, muss der Nutzer selbst entwickeln oder entwickeln lassen.

Die Übergänge, was in Software und was in Hardware umgesetzt wird, sind anwendungsabhängig zunehmend fließend – siehe Software Defined Radio (SDR).

Debugging Interface

In der Regel besitzen SoCs eine Debug-Schnittstelle (englisch interface). Dies ist oft eine einfache RS-232-Schnittstelle, die häufig über USB emuliert wird. Sie bietet einen direkten Zugriff von außen auf zentrale Teile des SoC und ermöglicht es beispielsweise, im Betrieb von einer Terminalemulation aus Fehlermeldungen und allgemeine Informationen abzufragen. In komplexeren Umgebungen übernimmt diese Funktion oft auch eine JTAG-Schnittstelle. Diese wird typischerweise nicht nur zur Übertragung von Fehlermeldungen genutzt, sondern zur Kommunikation mit einem Hard- oder Softwaredebugmodul im SoC. Ein solches Modul erlaubt es dem Anwender, beispielsweise das SoC „anzuhalten“ und die Abarbeitung im CPU-Kern im Einzelschrittmodus („Step-by-Step“) durchzuführen und bei Bedarf währenddessen einzelne Registerwerte zu ändern oder beispielsweise eine Schleife abzukürzen oder einen Sprungbefehl zu umgehen.

Eine weitere Anwendung dieser Schnittstelle ist das Programmieren programmierbarer Bereiche eines SoC, wie z. B. RAM, EEPROM, Flash oder auch einzelner Schaltungsteile bis hin zum gesamten SoC-Design (nur in einem FPGA o. Ä.). Meist hängen weitere externe Bausteine als „Kette“ an derselben JTAG-Schnittstelle, welche über einen sogenannten Boundary Scan angesprochen werden.

Komponenten

Zusammenfassung

Kontext

Bus

Verbunden wird das System intern über einen oder mehrere Busse. In komplexeren SoCs kommt oft ein hierarchisches oder zumindest segmentiertes Bussystem zum Einsatz. Dieses besteht typischerweise aus einem schnellen Systembus, einem langsameren Peripheriebus und einem Register- bzw. Steuerbus. Schnelle Peripherieeinheiten werden mitunter aber auch direkt mit dem Systembus verbunden. Zwischen dem Systembus und dem Peripheriebus vermittelt eine Bridge. Weiterhin benötigt jeder Bus mit mehreren Mastern einen Arbiter. Für die besonders wichtige Verbindung zwischen dem Prozessor und seinem oder seinen Cache(s) bzw. einem kleinen lokalen Speicher wird oft ein proprietärer aber besonders schneller Prozessorbus eingesetzt. Ein Beispiel hierfür ist der LMB von Xilinx.

Als Systembus sind in SoCs beispielsweise AMBA von Arm (Busse: AHB bzw. ASB/APB) CoreConnect von IBM (Busse: PLB/OPB/DCR) oder in jüngster Zeit auch der WishBone von Silicore/OpenCores.org stark vertreten. Weit verbreitet sind heute Busbreiten von 32 bis 128 Bit. Bei leistungsfähigen SoCs findet sich oft ein DMA-Controller am Systembus, um die CPU von Speicherzugriffen zu entlasten.

Die Spezifikationen dieser Busse sind physikalisch alle auf die Implementierung in ASICs (anwendungsspezifischen integrierten Schaltungen) und/oder FPGAs (englisch Field Programmable Gate Array) ausgelegt und unterscheiden sich auch ansonsten stark von verbreiteten Systembussen wie PCI – beispielsweise wird auf Grund des festen Systemaufbaus im Allgemeinen kein Plug and Play verwendet.

Taktgeber

Als Taktgeber und Zeitgeber sind Funktionsgruppen enthalten, die Impulse in einer bestimmten Frequenz abgeben. Es wird sich dabei um einfache physikalische Schwinger und weitere elektronische Funktionen zur Stabilisierung der Taktrate handeln, die für die Ablaufsteuerung und gegebenenfalls eine Synchronisation erforderlich sind.

Eine Echtzeituhr (physikalische Uhr) empfängt oder misst und zählt lokal eine physikalische Zeit und kann ebenfalls enthalten sein. Dazu sind präzise physikalische Schwinger meist extern zum SoC angeordnet.

Im weiteren Sinne sind mit dem Taktgeber außer dem Taktgeber und der Echtzeituhr auch spezielle stromsparende Weckschaltungen enthalten, die eine Uhrzeit auch nach Ausschalten des Systems behalten bzw. fortschreiben. Der oder die Taktgeber steuern dann auch den Bereitschaftszustand oder Sleep-Modus.

Prozessor

Üblicherweise besteht ein SoC aus einem Prozessor, welcher über ein Bussystem mit Speicher und weiterer Peripherie verbunden ist. Bei diesem Prozessor kann es sich sowohl um einen sehr einfachen 8-Bit-Mikrocontroller handeln, als auch um eine sehr leistungsfähige Multicore-CPU. Mehrprozessorsysteme sind ebenfalls möglich.

Je nach Leistungsfähigkeit, Anwendungsanforderungen und weiteren Kriterien wie Stromverbrauch, Größe und Preis besitzt das SoC eventuell neben seinen Registern nur einen kleinen internen Speicher, oder (meist zusätzlich) einen oder mehrere deutlich größere externe Speicher. Dies kann beispielsweise SDRAM oder Flash-Speicher sein. Hierfür hängt dann in der Regel am Systembus ein Speichercontroller, welcher eine entsprechende Schnittstelle für den Speicher zur Verfügung stellt.

Weitere Prozessoren

Um den eigentlichen Hauptprozessor des SoCs zu entlasten, sind je nach Anwendung auch spezialisierte Prozessoren enthalten. Dies können beispielsweise Prozessoren zur digitalen Signalverarbeitung sein (DSPs) oder beispielsweise Ver-/Entschlüsselungseinheiten oder sonstige Hardwarebeschleuniger wie Physikbeschleuniger. Hierzu können einzelne Berechnungen oder auch nur Teile davon ausgelagert werden. Diese werden entweder ganz vom Coprozessor übernommen, oder der Hauptprozessor reicht nur einzelne, besonders rechenintensive Befehle weiter. Diese werden dann unter Umständen nicht mehr als Software auf einer General Purpose CPU oder DSP ausgeführt, sondern direkt in Hardware implementiert. Dies ist zumindest in FPGAs und ASICs gängige Praxis und wird daher auch dementsprechend direkt von den EDA-Werkzeugen unterstützt. Viele moderne FPGAs wie Virtex4/5 oder StratixII/III enthalten auch sogenannte DSP-Makros, womit sehr schnell in vielen parallelen Pfaden sogenannte MAC-Befehle ausgeführt werden können.

Speicher

Der Speicher in einem SoC dient entweder zur Ablage und Ausführung des Programms (Programmspeicher) oder zur Ablage und Bearbeitung von Daten (Datenspeicher). Handelt es sich bei dem Speicher um einen Cache, so ist dieser oft in zwei getrennten Speichern als Harvard-Architektur ausgeführt. Normaler RAM wird hingegen gewöhnlich in einer Von-Neumann-Architektur implementiert. Speichertechnisch handelt es sich intern meist um schnellen SRAM, bei externem Speicher, welcher über einen Speichercontroller angebunden wird, meist um langsameren, aber günstigeren DRAM oder um Flash.

Peripherie

Welche weiteren Peripherieeinheiten integriert werden, hängt sehr stark von der eigentlichen Anwendung, aber natürlich auch von vielen weiteren Faktoren wie den beim Prozessortyp erwähnten Kriterien ab. Diese Peripherieblöcke hängen meist nicht direkt am Systembus, sondern über eine sogenannte Bridge an einem separaten Peripheriebus. Dieser ist meist deutlich langsamer getaktet, genügt jedoch den Anforderungen der meisten Peripherie. Somit wird in erster Linie neben einigen anderen positiven Effekten die kapazitive Belastung des Systembusses gesenkt, und dieser kann somit schneller getaktet werden, was natürlich nur so lange hilft, bis die CPU tatsächlich auf eine Peripherieeinheit warten muss; dann sind im Normalfall beide Busse belegt, ohne etwas zu übertragen. Zusätzlich erleichtert ein Peripheriebus die Entwicklung einfacherer Komponenten, da die Integration dieses Bustyps im Gegensatz zum Systembus in der Regel deutlich leichter fällt und durch seine oft kleinere Bitbreite und langsamere Taktung deutlich geringere Anforderungen stellt.

Je nach Art und Anzahl der Peripherieblöcke sowie Einsatzzweck des SoC enthält dieses manchmal einen dedizierten Interrupt Controller. Bei einfachen, kleineren oder besonders günstigen Systemen wird aber oft auf einen solchen Controller verzichtet, hier muss dann die Software die Interruptquelle ermitteln. Fortschrittliche Interrupt Controller bieten nicht nur viele Kanäle um die Zuordnung der Interrupts zu übernehmen, sondern bieten auch Kanäle mit unterschiedlichen Interrupt-Prioritäten an. Dies ist wichtig, wenn in Teilen des Systems Echtzeitanforderungen gestellt werden, die mit Interrupts nicht einfach bzw. manchmal überhaupt nicht zu lösen sind, da Interrupts nicht vorhersehbar sind. Dieses Problem kann oft durch eine intelligente Priorisierung gelöst werden.

Oft sind weit mehr Peripherie-Module vorhanden, als in einer bestimmten Anwendung genutzt werden. Von den äußeren Anschlüssen bleiben weniger ungenutzt, da diese oft programmierbar verschiedenen Modulen zugeordnet werden können. Teilweise kann einzelnen Modulen der Takt und Gruppen von Modulen sogar die Spannung abgeschaltet werden, um die Leistungsaufnahme zu senken.

Grafik

Viele SoCs enthalten auch einen Grafikprozessor, der ein oder mehrere Displays ansteuert. Hierfür ist in einem PC sonst eine separate Grafikkarte oder ein im Chipsatz integrierter Grafikkern (GPU) zuständig (sogenannte Hardwarebeschleunigung). Wegen der immer weiter fortschreitenden Integration fertigen seit einigen Jahren große CPU-Hersteller wie AMD/ATI,[2] Intel und VIA/Nvidia, CPUs mit integrierten GPUs. Manche eingebetteten Systeme stellen hohe Anforderungen an die Grafikausgabe (Spielekonsolen, Blu-Ray/DVD-Player, bildgebende Geräte der Medizintechnik oder des Militärs), in anderen Fällen reichen oft LCDs oder einige Leuchtdioden zur Statusausgabe aus. Je nach Anwendung kann auch ganz auf eine grafische Ausgabe verzichtet werden.

Besonders erschwert wird die Realisierung der Grafikfähigkeit oft durch besonders rigide Vorgaben bei maximaler Leistung, der maximalen Chipfläche oder auch durch einen extremen Preisdruck, sofern es sich um Massenware handelt.

Audio

Ebenso anzutreffen sind in vielen SoCs spezielle Audiokerne. Diese werden beispielsweise in Mobiltelefonen, MP3-, DVD-Playern und ähnlichen Multimediageräten benötigt. Hierbei kommen je nach Anforderung, Stückzahl, finanziellen Möglichkeiten, Platzbeschränkungen usw. oft aber auch externe Hardware-Audio-Codecs zum Einsatz, welche dann nur über einen relativ kleinen IP-Block an den SoC-internen Bus angebunden sind. Sofern keine besonders hohen Anforderungen an die Audioqualität gestellt werden, kann beispielsweise ein AC’97-Codec zum Einsatz kommen. Kosten können mit solchen externen Komponenten aber nur bei kleinen Stückzahlen gespart werden, da sich hier die Entwicklungskosten für eine integrierte oder gar selbst entwickelte Lösung oft überproportional auswirken.

Schnittstellen

SoCs kommunizieren typischerweise viel stärker mit ihrer technischen Umgebung als mit einem Bediener. Hierzu werden je nach Anforderung diverse Schnittstellen implementiert. Dies geschieht oftmals durch Einbinden fertiger IP-Blöcke, welche je nach Geschwindigkeit- und Latenzanforderung mit dem internen System- oder Peripheriebus verbunden werden.

Zum Bediener hin kommt neben den bereits angesprochenen Audio- und Grafikschnittstellen hauptsächlich ein Tastaturcontroller (z. B. für Matrix-Tastaturen, serielle Tastaturen oder Touchpads) oder eine USB-Schnittstelle für entsprechende Geräte in Frage. Zur Kommunikation mit anderen Systemen kommen hauptsächlich Serielle Schnittstellen wie z. B. USB, RS232, CAN-Bus, LIN-Bus, MOST-Bus, ARINC 429 und Ethernet in Frage. Hierbei wird manchmal nur der MAC-Layer im SoC integriert, manchmal aber auch der PHY. Eine weitere Möglichkeit sind parallele Schnittstellen wie z. B. Centronics, Port-IO, IDE/CF usw.

System-on-a-programmable-Chip

Zusammenfassung

Kontext

In zunehmender Zahl werden SoCs auf programmierbaren Chips implementiert, sogenannten System-on-a-programmable-Chips. Hierbei handelt es sich um eine Kombination aus FPGA-Logik und weiterer Peripherie sowie CPUs. Hierbei kommen als Prozessor sowohl sogenannte HardCores (im Silizium vorhandene CPU-Kerne parallel zur programmierbaren FPGA-Logik) als auch SoftCores (in den FPGA-Quellcode eingefügte, synthetisierbare CPU-Makros) zum Einsatz. Als HardCore gibt es beispielsweise PowerPC- oder ARM-Kerne, als SoftCores meist herstellerspezifische Prozessoren wie den MicroBlaze von Xilinx oder den NIOS II von Intel (vormals Altera). Es existieren aber auch plattformunabhängige synthetisierbare Kerne von ARM, Lattice und anderen, welche entweder kommerziell als IP-Core vertrieben werden oder als Open Source zur Verfügung stehen. Auf diese Weise können die benötigten Funktionen eines Systems optimal auf die angebotenen Ressourcen verteilt werden.

Nicht zu verwechseln ist dies mit Lösungen wie den PSoCs von Cypress oder anderen Firmen, bei welchen nur ein klassischer Mikrocontroller programmierbar ist, nicht jedoch dessen ALU und das ganze System mit Bussen, Speicher und weiterer Peripherie.

Die üblichen Komponenten eines SoCs sind:

- Prozessor

- Grafikprozessor

- Soundchip

- Speicher

- Interne Einheiten

- Zeitgeber

- Zähler

- Interruptcontroller

- Watchdog-Timer

- Debug-Schnittstellen, z. B. JTAG

- Spezielle Recheneinheiten, wie z. B. in DSP-SoCs

- Kryptographie

- Peripherie-Einheiten und -Schnittstellen

- Tastaturcontroller, z. B. für Matrix-Tastaturen, serielle Tastaturen oder Touchpads

- Grafikschnittstellen, z. B. für LVDS, LCD, VGA, DVI, MPEG, HD/SDMI

- Serielle Schnittstellen, z. B. USB, RS232, CAN-Bus

- Parallele Schnittstellen, z. B. nach Centronics, Port-IO

- Pulsweitenmodulation, z. B. für DC-DC-Wandler oder Motorsteuerung

- Modulatoren, z. B. für GSM-Codierung, QAM, PSK

- Weitere Schnittstellen, z. B. Ethernet, MAC oder USB

- Analog-Digital-Umsetzer

Hersteller

Am Markt finden sich zahlreiche Angebote für System-on-a-Chip-Halbleiter. Wichtige Anbieter hierfür sind: (alphabetisch sortiert, nicht nach Größe)

- ARM und Intel mit der ARM-Architektur bzw. der Weiterentwicklung XScale (auch Intel Quark oder Intel Edison)

- Altera (Intel), Microsemi und Xilinx mit diversen SoC-Plattformen in FPGAs

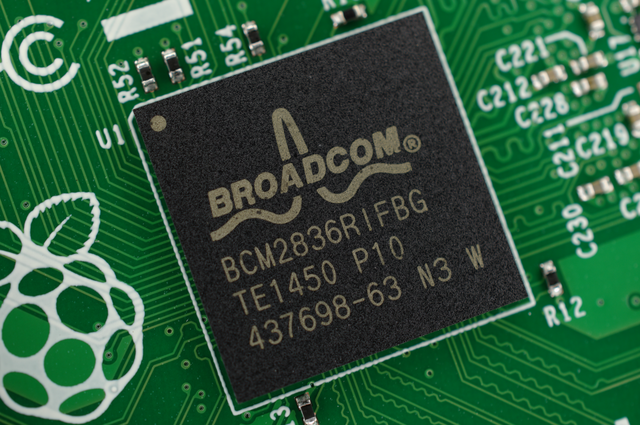

- Broadcom mit diversen Kommunikationschips

- Cypress Semiconductor Corporation für PSoC programmierbare System on Chip

- Infineon und NXP mit SoC-ICs für mobile Endgeräte wie Handys oder auch xDSL-Modems

- LSI Logic mit Chips für Netzwerk und Speicherprodukte

- MIPS und Lizenznehmer wie etwa AMD mit der AU1000 Serie

- Motorola/Freescale/NXP Semiconductors und IBM mit diversen PowerPC-Derivaten

- Qualcomm (Snapdragon) für moderne Smartphone-SoCs

- STMicroelectronics

- TDK-InvenSense mit SoC-ICs für Bewegung und Lage, Bild und Ton im Gamecontroller, Handy und Head-Mounted Display

- Texas Instruments mit OMAP, DSPs und RF-Modulen (z. B. ZigBee Modul µTiny)

Literatur

- Bashir M. Al-Hashimi: System-on-Chip: Next Generation Electronics. Institution of Engineering and Technology, 2006, ISBN 0-86341-552-0.

- F. Kesel und R. Bartholomä: Entwurf von digitalen Schaltungen und Systemen mit HDLs und FPGAs. Oldenbourg, 2006, ISBN 3-486-57556-2. – Erklärt den Entwurf digitaler Schaltungen und SoCs auf FPGA-Basis – VHDL-Beispiel ist ein kleiner Mikrocontroller. Ausblick zu SystemC enthalten (Hinweis: Ist kein VHDL-Einsteiger-Lehrbuch!)

- Steve Furber: ARM Rechnerarchitekturen für System-on-Chip-Design. Mitp-Verlag, 2002, ISBN 3-8266-0854-2.

Weblinks

- 1974: Digital Watch is First System-On-Chip Integrated Circuit. In: Computer History Museum. Archiviert vom am 27. März 2023 (englisch).

Einzelnachweise

Wikiwand - on

Seamless Wikipedia browsing. On steroids.