Loading AI tools

Gruppe von RISC-Prozessorarchitekturen Aus Wikipedia, der freien Enzyklopädie

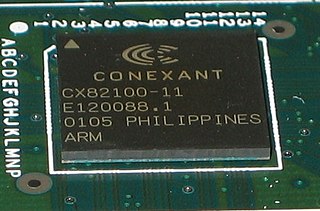

Die ARM-Architektur ist eine ursprünglich 1983 vom britischen Computerunternehmen Acorn entwickelte Mikroprozessor-Architektur, die seit 1990 von der aus Acorn ausgelagerten Firma ARM Limited weiterentwickelt wird. ARM stand für Acorn RISC Machines,[1] später für Advanced RISC Machines.[2] Obwohl der Name außerhalb der IT-Fachwelt wenig bekannt ist, gehören Implementierungen dieses Typs weltweit zu den meistverbreiteten Mikroprozessoren.

Das Unternehmen ARM Limited stellt keine eigenen ICs her, sondern vergibt unterschiedliche Lizenzen an Halbleiter-Entwicklungsunternehmen und Halbleiterhersteller. Dabei können die Kunden wählen zwischen Entwicklungslizenzen, die die Entwicklung eigener ICs auf Basis der ARM-Architektur ermöglichen, und dem Zukauf von sogenannten IP-Cores, Funktionsblöcken wie CPU-Kerne der Arm-Cortex-A-Reihe, GPU-Einheiten wie Mali oder Bussystemen wie AMBA, die dann zu eigenen System-on-a-Chip-Bausteinen konfiguriert werden.

Die Vielzahl dieser Lizenznehmer und verschiedene Vorteile der Architektur (z. B. geringer Energiebedarf bei hoher Leistungsfähigkeit) führten dazu, dass ARM-Implementierungen im Embedded-Bereich die meistgenutzte Architektur sind. Fast alle derzeitigen Smartphones und Tabletcomputer haben lizenzierte ARM-Prozessoren, darunter das iPhone und die meisten Android-Geräte. Die ersten ARM-Prozessoren (ARMv1) aus dem Jahr 1985 hatten eine 32-Bit-Architektur (ARM32), etwa 2013 erschienen dann Prozessoren mit 64-Bit-Architektur (Armv8-Serie, ARM64). Die ersten 64-Bit-Systeme waren der X-Gene der Firma Applied Micro Circuits Corporation im Juni 2013[3] und im September 2013 der A7 im iPhone 5s.[4]

Die ARM-Architektur wurde 1983 vom englischen Computerhersteller Acorn als Entwicklungsprojekt gestartet. Das Team begann unter der Leitung von Sophie Wilson und Steve Furber die Entwicklung eines leistungsfähigen Prozessors für einen Nachfolger der bis dahin auf dem 6502 basierenden Computer.

Anstatt wie die Konkurrenz auf Prozessoren der Unternehmen Intel oder Motorola zurückzugreifen, entwickelte man einen eigenen Prozessor, den ARM (Acorn Risc Machine) mit 32 Bit und einer geplanten Taktfrequenz von 4 MHz. Die Tests mit den Prototypen verliefen derart erfolgreich, dass die späteren Serienprozessoren (ARM2, 1986), die in den neu entwickelten Rechnern (Acorn Archimedes) verbaut wurden, direkt mit 8 MHz getaktet wurden. Tests ergaben, dass diese Rechner bei praktisch gleicher Taktfrequenz etwa achtmal schneller waren als die Konkurrenten Commodore Amiga und Atari ST mit Motorola-68000-Prozessor.

Nachdem der ARM2 1989 zum ARM3 (mit Cache und höherer Taktfrequenz) weiterentwickelt worden war, und immer mehr Unternehmen Interesse an diesen Prozessoren bekundet hatten, gründete Acorn im Jahre 1990 zusammen mit Apple und VLSI Technology das Unternehmen Advanced RISC Machines Ltd. mit Sitz in Großbritannien, das später in ARM Ltd. umbenannt wurde.

Die Architektur zeichnet sich durch einen effizienten Befehlssatz aus, erlaubt eine kompakte ASIC-Implementierung und ist gut für Optimierungen im Bereich der Ausführungsgeschwindigkeit und der Stromaufnahme geeignet.

Eine bedeutende Implementierung ist der als StrongARM bekannte Mikrocontroller.

Der Hersteller Intel ist neben anderen Marktteilnehmern Lizenznehmer des Unternehmens Advanced RISC Machines Ltd. und darf somit auf der ARM-Architektur basierende Prozessoren herstellen. Darüber hinaus darf Intel (neben z. B. Apple, Motorola/Freescale oder NXP), im Gegensatz zu den meisten anderen Lizenznehmern, Änderungen und Erweiterungen am ARM-Kern durchführen. So vertrieb Intel bis 2006 unter dem Namen XScale eine in Lizenz gefertigte ARM-CPU und weitere ebenfalls als XScale bezeichnete und per Bus angebundene Peripherie-Halbleiter. Dazu gehören die PXA250-, PXA260- und PXA270-Prozessoren, die häufig in PDAs und Smartphones zum Einsatz kamen, vor allem für Windows CE und Palm OS.

Die GNU Compiler Collection kann Code für ARM erzeugen und auch der XNU-Kernel (macOS/iOS), Linux-Kernel und Windows NT Kernel 6.2 laufen auf diesem CPU-Typ.

Aufgrund ihrer geringen Leistungsaufnahme kommen ARM-Prozessoren vor allem in eingebetteten Systemen wie Mobiltelefonen, PDAs und Routern zum Einsatz. Besondere Bedeutung hat die Architektur bei Smartphones, da sie von allen verbreiteten mobilen Betriebssystemen unterstützt wird. Bei tragbaren Spielkonsolen besteht eine ähnliche Verbreitung. Ebenfalls findet man die CPUs in vielen stationären Geräten der Unterhaltungselektronik.

Die Rechner der Acorn-Archimedes- und Risc-PC-Reihe von Acorn verwendeten ebenfalls ARM-CPUs. Nachfolgemodelle dieser Desktop-Rechner waren unter anderem vom Unternehmen Castle Technology unter dem Namen IYONIX pc erhältlich.

Im Herbst 2020 stellte Apple drei Systeme aus der Mac-Reihe vor, welche mit dem Apple M1 ein ARM-basiertes Ein-Chip-System (System on a Chip, SoC) als Prozessor verwenden.[5]

Auch auf dem Raspberry Pi ist ein Ein-Chip-System von Broadcom mit einem ARM-Mikroprozessor verbaut.

Mit der Fertigstellung der 64-Bit-Mikroarchitektur Armv8 im Jahre 2012 waren die Voraussetzungen für einen Einsatz von ARM-Prozessoren in Serversystemen gegeben. ARM stand hier vor der Aufgabenstellung, ein komplettes Marktsegment zu definieren, da Serversysteme auch spezialisierte Betriebssysteme und Anwendungen benötigen. Unter Mitarbeit von Red Hat und anderen Betriebssystemherstellern entstand 2016 die Server Base System Architecture (SBSA),[6] eine Spezifikation, die alle Hardware-Schnittstellen beinhaltet, die auf einem Serversystem für das Betriebssystem benötigt werden. Daraufhin entstanden ARM-Linux-Server-Distributionen von Red Hat, SuSE und Ubuntu sowie eine Windows-ARM-Server-Variante von Microsoft, welche wiederum eine Basis von wichtigen Infrastrukturanwendungen zur Verfügung stellen. Die Arm-Architektur ist auch für dieses Marktsegment wegen ihrer geringen Leistungsaufnahme (Preis / Watt und Preis / Performance Index) interessant, weswegen ARM Serverprozessoren auch für Höchstleistungsrechner und Supercomputer bewirbt.

Mehrere Partner (Architektur-Lizenznehmer) entwickelten daraufhin ARM-Server-Prozessoren:

Im Herbst 2018 gab ARM eine eigene Roadmap über Technologien für Server-Prozessoren, genannt Neoverse, heraus.[7][8] Dies dokumentiert, dass weitere ARM-Entwicklungen und Support für die Entwicklungspartner zu erwarten sind.

Die ARM-CPU ist eine RISC-Architektur und kennt als solche drei Kategorien von Befehlen:

Die ARM verwendet einen Drei-Adress-Code-Befehlssatz, alle arithmetisch-logischen Befehle akzeptieren also ein Zielregister und zwei Operandenregister.

ADD r0, r1, r2 ;r0 := r1 + r2

Die ARM ist sowohl Little-Endian- als auch Big-Endian-kompatibel, kann also mit beiden Byte-Reihenfolgen umgehen, was angesichts des Einsatzzwecks als Standard-CPU in Kommunikationsgeräten ein deutlicher Vorteil ist. Der Standardmodus der ARM ist Little-Endian.

Wie viele RISC-CPUs bietet ARM eine große Anzahl von Registern: Dem Programmierer stehen 13 Universal-Register zur Verfügung r0...r12. Drei zusätzliche Register r13...r15 sind wie Universal-Register adressierbar, haben aber spezifische Bedeutungen. Diese sind ein Stackpointer r13, ein „Link-Register“ r14, das die Rücksprungadresse bei Prozeduraufrufen (mit BL „branch with link“) enthält, die später zurück in den Programmzähler geschrieben wird, sowie der Programmzähler (Program-Counter, PC) selbst r15. Zusätzlich zu diesen direkt veränderbaren Registern gibt es das Status-Register (CPSR, Current-Program-Status-Register), das die Statusbits und andere Informationen, wie z. B. den momentanen Ausführungsmodus, enthält.

Die ARM kennt mehrere Ausführungsmodi, die über bestimmte Ereignisse betreten werden und teilweise dem ausgeführten Code zusätzliche Privilegien einräumen. Im Einzelnen sind das:

r13, r14 und das Statusregister werden für die Interrupt- und Exception-Modi gespiegelt (sogenannte Schattenregister), so dass Ausnahmebehandlungsroutinen sich nicht um die Sicherung des User-Stackpointers oder Link-Registers zu kümmern brauchen. Für die Fast Interrupts werden zusätzlich r8...r12 gespiegelt und stehen so dem Programmierer einer Interrupt-Service-Routine direkt zur Verfügung, ohne dass er den Inhalt dieser Register vorher sichern müsste.

Der Load/Store-Befehl des ARM unterstützt die üblichen Adressierungsmodi. Bei der unmittelbaren Adressierung und der absoluten Adressierung gibt es jedoch einige Einschränkungen, die im Folgenden näher erklärt werden sollen:

Sämtliche Befehle im ARM-Befehlssatz sind 32 Bit lang. Dies bedeutet auf der einen Seite, dass jede Instruktion mit einem Speicherzugriff geladen werden kann, wodurch sich die Architektur der Pipeline und die Instruction Fetch-Unit vereinfachen. Auf der anderen Seite können 32-Bit-Adressen oder 32-Bit-Werte nicht in einem 32 Bit breiten Befehl angegeben werden, da dann kein Platz mehr für den eigentlichen Befehlscode bleibt. Stattdessen hilft man sich folgendermaßen:

000000FF, 000003FC, 00000FF0, 00003FC0, … 0FF00000, 3FC00000, FF000000, FC000003, F000000F und C000003F direkt kodiert werden.MOV PC,LR ins Programmzähler-Register zurückkopieren, um wieder ins aufrufende Programm zurückzukehren).LDR PC,[PC,#-4] angesprungen wird.Der ARM-Befehlssatz enthält einige Besonderheiten, die zur Effizienz der Architektur beitragen:

CMP r0, r1 ;(setzt Bedingungsbits) ; "CMP" bedeutet: "CoMPare"

ADDGE r2, r2, r3 ;if r0 >= r1 then r2 := r2 + r3 ; "ADDGE" bedeutet: "ADD if Greater or Equal"

ADDLT r2, r2, r4 ; else r2 := r2 + r4 ; "ADDLT" bedeutet: "ADD if Less Than"

1111 stand zu Beginn für die Condition NV (never), diese Befehle werden also nie ausgeführt. Diese Opcodes werden in neueren CPUs für spezielle Befehle wie PLD und BLX verwendet (die dann nicht mehr bedingt ausgeführt werden können), von der Benutzung beliebiger Opcodes mit Kondition NV für NOPs wird daher abgeraten („deprecated“).S im Assemblercode gekennzeichnet und kann mit der bedingten Ausführung kombiniert werden.CMP r0, r1 ;(setzt Bedingungsbits)

ADDGES r2, r4, r5 ;if r0 >= r1 then r2 := r4 + r5

BCS overflow ;verzweige bei Überlauf der Addition

ADD r2, r3, r3, lsl #2 ;r2 := r3 + (r3 << 2)

; := r3 + 4*r3

; := 5*r3

Um die Code-Dichte zu erhöhen, also den Speicherbedarf für eine bestimmte Funktion zu verringern, hat ARM Ltd. den Thumb-Befehlssatz entwickelt, der nur aus 16 Bit breiten Befehlen besteht. Obwohl man oft mehr Assembler-Befehle benötigt, um ein Programm zu schreiben, wird die Code-Größe in der Praxis um etwa 30 bis 40 Prozent reduziert. Aus 16-Bit-Speicherbausteinen werden Befehle in nur einem Speicherzyklus geladen, aus 32-Bit-Speicherbausteinen lädt ein ARM-Prozessor stets zwei Thumb-Instruktionen auf einmal.

Die geringere Programmgröße wird allerdings oft durch eine geringere Ausführungsgeschwindigkeit erkauft. Zum einen sind viele Thumb-Befehle weniger leistungsfähig als die entsprechenden ARM-Befehle (und es werden mehr Thumb-Anweisungen benötigt), zum anderen gibt es in diesem 16-Bit-Befehlssatz keine bedingte Befehlsausführung außer den bedingten Sprüngen. Daher treten mehr Programmsprünge auf, und die Pipeline wird öfter entleert. Zumindest wenn der Speicher mit 32 Bit angesprochen wird, ist der 16-Bit-Befehlssatz schon deshalb oft langsamer als der ARM-Befehlssatz. Der Hersteller NXP gibt in den Datenblättern seiner LPC2000-Controller einen Geschwindigkeitsverlust von 30 Prozent an.

ARM- und Thumbcode können miteinander vermischt werden. Häufig ist in großen Teilen eines Programmes die Ausführungsgeschwindigkeit sekundär. Es bietet sich an, für diese Programmteile Thumb-Anweisungen zu verwenden, aber die kritischen Bereiche mit ARM-Anweisungen zu implementieren. Diese Technik nennt sich Thumb Interworking.

Mit ARMv6 wurde der Thumb-Befehlssatz auf 32-Bit-Code erweitert und Thumb-2 genannt. Mit Thumb-2 kann 16-Bit- und 32-Bit-Code frei vermischt werden.[10]

Thumb ist nur auf der klassischen 32-Bit-ARM-Architektur (retronym A32 bzw. AArch32 bezeichnet) verfügbar, es wurde nicht auf ARM64 (bzw. AArch64) übernommen.[11]

Die ARM ist als Mikroprozessor-Kern in eingebetteten Systemen gedacht, in denen meist keine Gleitkomma-Arithmetik benötigt wird. Der ARM wurde jedoch speziell im Hinblick auf Erweiterbarkeit um Coprozessoren entwickelt und besitzt ein eigenes Coprozessor-Interface und Befehle für optionale Coprozessoren.

Zusammen mit dem Cortex-A7 hat ARM das Big.LITTLE-Konzept eingeführt, das dazu dient, die mit 3,5 DMIPS/MHz hohe Rechenleistung des Cortex-A15[12] mit der niedrigen Energieaufnahme des Cortex-A7 zu verbinden. Dabei werden beide Cores in Form von Clustern mit jeweils zwei bis vier Kernen auf einem SoC zusammengefasst. Da der Cortex-A7 aus Software-Sicht wie ein Cortex-A15 aussieht, wird der Cortex-A15-Cluster bei Aufgaben, die nicht die volle Rechenleistung benötigen, abgeschaltet und die weiteren Berechnungen durch den Cortex-A7 durchgeführt. Wenn mehr Rechenleistung benötigt wird, wird der Cortex-A15-Cluster wieder eingeschaltet und der Cortex-A7-Cluster stillgelegt.[13]

Nach Erscheinen der 64-Bit-CPUs Cortex-A53 und A57 wurde das Big.LITTLE-Konzept auch auf diese übertragen. Gleichzeitig wurde es dahingehend erweitert, dass Tasks jetzt nicht nur clusterweise, sondern individuell von einer beliebigen CPU auf jede beliebige andere übertragen werden können.[14]

Das Konzept leidet jedoch an einigen Schwächen, so z. B. bei sprunghaften Laständerungen, die in hohen Latenzzeiten münden, oder durch fehlende Berücksichtigung des realen Energieverbrauchs der einzelnen CPUs.[14]

2017 führte Arm DynamIQ ein; eine DynamIQ Shared Unit (DSU) verwaltet mehrere CPU-Cores in einem Cluster mit gemeinsamem L3-Cache und gemeinsamer Anbindung nach außen.[15][16] Arm erweiterte dabei das Big.LITTLE-Konzept in mehreren Punkten:

2021 stellte Arm zusammen mit den ersten ARMv9-CPU-Cores Cortex-A510, -A710 und -X2 eine neue DynamIQ Shared Unit vor, DSU-110 genannt:[17][18]

Die DynamIQ-CCI-Einheiten werden für SoCs ausschließlich zusammen mit den Arm-eigenen 64-Bit-Kernen A55 und A510, A75 bis A710 und X1/X2 angeboten.

2014 stellte Arm eine Familie von Systemlösungen für Server-CPUs vor, die CCN-500 Interconnect Serie, die je nach Modell zwischen 4 und 12 Cluster mit je 4 CPU-Kernen in einem koherenten Netzwerk vereinen konnte; es waren 2 bis 4 Speicherkanäle möglich, der gemeinsame L3-Cache umfasste bis zu 8 bzw. bis zu 32 MB.[19]

2016 stellte Arm den Nachfolger, den CMN-600 Interconnect vor, der bis zu 32 Cluster mit je 4 CPU-Kernen in einem koherenten Mesh-Netzwerk mit 64 (8 × 8) Knoten vereinen kann. Es sind bis zu 8 Speicherkanäle und 4 CCIX-Ports (seit Revision 2) möglich und der gemeinsame L3-Cache kann bis zu 128 MB umfassen.[20]

2021 wurde von Arm der Interconnect CMN-700 vorgestellt. In einem kohärenten Mesh-Netzwerk mit 144 (12 × 12) Knoten können nun 256 CPU-Cores, 40 Speichercontroller (DRAM, HBM) und 32 CCIX-Ports eingebunden werden und der gemeinsame L3-Cache kann bis zu 512 MB umfassen.[21]

Die Architektur von ARM-Prozessoren erfuhr seit 1985 zahlreiche Veränderungen, zum Beispiel bei der Zahl der Register, der Größe des Adressraumes und dem Umfang des Befehlssatzes. Sie wird daher in Versionen unterteilt, abgekürzt mit ARMv[Versionsnummer]. Beginnend mit ARMv2 wurden die Architekturversionen in mehr als nur einem Prozessor implementiert.

Seit dem ARMv6 werden die sogenannten Cortex-Architekturen speziell für besondere Anwendungen entwickelt:

Seit 2018 bietet ARM die Neoverse-Familie für Serverlösungen an. 2020 wurde die Cortex-A-Familie um Cortex X erweitert. Diese Cores wurden auf Leistung optimiert.

| Gene- ration | Architektur / Familie(n) | Release- Jahr | üblicher CPU- Takt (MHz) | Befehlsdurchsatz (DMIPS/MHz) |

|---|---|---|---|---|

| ARMv1 | ARM1 | 1985 | 4 | − |

| ARMv2 | ARM2, ARM3 | 1986, 1989 | 8...25 | 0,5 |

| ARMv3 | ARM6, ARM7 | 1991, 1993 | 12...40 | 0,89 |

| ARMv4 | ARM7TDMI, ARM8, StrongARM ARM9TDMI | 1995, 1997 | 16,8...75 203...206 180 | 0,9 |

| ARMv5 | ARM7EJ, ARM9E, ARM10E | 2002 | 104...369 133...1250 | 1,25 |

| ARMv6 | ARM11 (1176, 11 MPCore, 1136, 1156) Arm Cortex-M (M0, M0+, M1) | 2002 ? | 427.[22]..1000+[23] bis 200[24] | 0,6.[22].1,54[25] 0,84...0,94[26] |

| Armv7 | Arm Cortex-A (A8, A9, A5, A15, A7, A12, A17) Arm Cortex-M (M3, M4, M7) Arm Cortex-R (R4, R5, R7, R8) | 2004 2005 2011 | bis 2500.[27] ? ? | 1,58.[28] 3,5[29] 1,25...2,14[26] ? |

| Armv8 | Arm Cortex-A (A32, A53, A57, A72, A35, A73, A55, A75, A76, A77, A78, X1)[30] Arm Cortex-M (M23, M33) Arm Cortex-R (R52) Arm Neoverse (E1, N1, V1) | 2012–2020 ? 2016 2018–2021 | 1200...3000.[31] ? ? ...3300 | 2,3.[32] 4,1[33] ? ? ? |

| ARMv9 | Arm Cortex-A (A510, A710, X2) Arm Neoverse (N2) | 2021 2021 |

Die ersten Versionen eines ARM-Prozessors (ARMv1) wurden 1985 als Zweitprozessor im ARM Development System für den BBC Master eingesetzt.

Die ARMv2-Architektur umfasst zwei Familien: ARM2 und ARM3.

Der ARM2 ist ein von dem englischen Unternehmen Acorn Computers Ltd. entwickelter 32-Bit-RISC-Prozessor. Dieser wurde 1986 veröffentlicht und ab 1987 im Acorn Archimedes eingesetzt. Beim Standardtakt von 8 MHz wurden für damalige Verhältnisse unglaubliche 4 MIPS erreicht. 1991 erschien der ARM250, der ebenfalls auf dem ARM2 basierte, aber nun mit 12 MHz getaktet war und 7 MIPS erreichte. Außerdem wurden eine MMU-Einheit sowie ein Grafik- und IO-Prozessor integriert. Eingesetzt wurde diese CPU nur in den Archimedes-Modellen A3010, A3020 und A4000.

Der ARM3 ist ebenfalls ein 32-Bit-RISC-Prozessor, der von Acorn Computers Ltd. entwickelt wurde. Er wurde 1989 veröffentlicht und in den Archimedes-Modellen A540, A5000 und A4 eingesetzt. Bei diesem Prozessor hat Acorn erstmals einen Cache mit 4 KiB integriert. Mit einer Taktfrequenz von 25 MHz erreicht der ARM3 12 MIPS.

Der ARM6 ist ein von der mittlerweile gegründeten ARM Limited 1991 veröffentlichter 32-Bit RISC-Prozessor, der als CPU beispielsweise im Apple Newton oder Acorns Risc PC eingesetzt wurde. Der CPU-Takt betrug 12–33 MHz.

Der ARM7TDMI war das Low-End-Modell der ARM-Familie und wurde vor allem als Komponente in SoCs für Mobiltelefone und andere portable Kommunikations- oder Multimediageräte verwendet, darunter der Game Boy Advance, Nintendo DS (als Subprozessor) und Nintendo 3DS (ebenso als Subprozessor). Die Kürzel im Modellnamen stehen für Thumb Instruction Set (Programmspeichersparender 16-Bit-Modus des 32-Bit-Kernes), Debug Port, 64-Bit-Result Multiplier und Embedded ICE Modul.

Der ARM7TDMI hat eine dreistufige Pipeline und einen gemeinsamen Bus für Instruktionen und Daten.

Der gemeinsam mit DEC entwickelte ARM StrongARM war die erste Abspaltung der Arm-Architektur, die 1995 als SA-110 im Newton 2000 durch einen Stromsparmodus für lange Akkulaufzeiten sorgte. Der Nachfolger SA-1100 (1997) war mit einer LCD-Schnittstelle, einer MCP-Audio/Touchscreen-Schnittstelle, PCMCIA-Unterstützung, IrDA, USB und DMA-Controller eines der ersten System-on-a-Chip.

Die Architekturversion 5TE wurde von ARM in den Prozessormodellen ARM7EJ, ARM9E und ARM10E implementiert. ARM9 ist eine Weiterentwicklung der StrongARM- und ARM8-Prozessoren. Der wesentliche Unterschied des ARM9 gegenüber dem ARM7 ist je ein getrennter Bus für Instruktionen und Daten (Harvard-Architektur). Meist werden diese an separate Caches für Daten und Instruktionen angeschlossen. Außerdem hat der ARM9 eine fünfstufige Pipeline und kann so höhere Taktraten erreichen und weist bessere CPI-Werte (Cycles per Instruction) auf. Wird der ARM9 ohne Caches an einem externen Speicher mit nur einem Datenbus betrieben, schrumpft der Geschwindigkeitsvorteil gegenüber der ARM7-Architektur wegen häufiger Pipeline-Stalls mit einer höheren Latenz durch die längere Pipeline. Ohne Cache kann in einem solchen ungünstigen Szenario ein ARM7 aufgrund seiner kürzeren Pipeline trotz eines deutlich niedrigeren Taktes schneller sein. Allerdings sollte dieser Fall in realen Systemen nicht auftreten, da ein ARM9 teurer ist und nur wegen seiner besseren Performance ausgewählt wird. Kommt es eher auf die Kosten an, so spart man sinnvollerweise nicht am Cache, sondern verwendet einen ARM7.

Intel stellte ab dem Jahr 2002 auf Basis der ARMv5TE die Prozessoren der XScale-Reihe (802xx, PXA25x, XA263, PXA26x, PXA27x, PXA3xx) vor, die mit einer Taktfrequenz bis zu 1250 MHz in viele mobile Geräte (Palm Tungsten, Sony Clié) Eingang fanden. 2006 wurde die XScale-Entwicklung an die Marvell Technology Group verkauft. Im Juni 2008 stellte Marvell den auf Basis der ARMv5TE entwickelten Sheeva-Mikroprozessor vor. Dieser ist als Hauptprozessor für die Integration in die hauseigenen Ein-Chip-Systeme vorgesehen.[34] Ein von Marvell entwickeltes SoC mit Sheeva-CPU bildet die Basis für den ersten zur Marktreife gebrachten „Plug Computer“. Der sogenannte SheevaPlug wurde im Jahr 2009 vorgestellt.

Mit ARMv6, angekündigt im Oktober 2001, kamen SIMD-Befehle hinzu, Multiprozessorunterstützung und eine neue Cache-Architektur. Implementierungen dieser Architekturversion sind die ARM11-Familie, die sich auch durch eine verbesserte Pipeline von den Familien ARM9 und ARM10 absetzte, und die kleineren Prozessorkerne für Mikrocontroller Arm Cortex-M0, Arm Cortex-M0+ und Arm Cortex-M1.

Mit ARMv6 wurde auch der Thumb-Befehlssatz auf 32-Bit erweitert. Diese nun Thumb-2 genannte Erweiterung erlaubt die freie Verwendung von 16-Bit- und 32-Bit-Instruktionen im Code und ist auf 32-Bit-ARM (retronym AArch32) seit ARMv6T2 verfügbar, allerdings ist beim ARMv6-M nur ein eingeschränkter 32-Bit-Befehlssatz in Thumb-2 implementiert.[10]

ARM11-Kerne – der erste, ARM1136, wurde Lizenznehmern im Oktober 2002 angeboten – wurden in Smartphones verbaut, unter anderem von Apple und Nokia.

Es wird eine SIMD-Einheit eingeführt, die mit 32 Registern von 128 Bit Breite arbeitet, genannt NEON, primär für Multimediaverarbeitung gedacht, die aber wie konkurrierende SIMD-Einheiten (AltiVec/VSX in der POWER-Architektur oder SSE/AVX in der Intel-Architektur) vielfältige Arithmetik und Vektorbefehle ausführen kann.

Ab der Armv7-Architektur werden die sie implementierenden Prozessorkerne drei Anwendungsfeldern zugeteilt:

Spätere ARMv7-Kerne, etwa Cortex-A15 und Cortex-A7, bieten zusätzlich zur klassischen 32-Bit-MMU mit 2 Seitentabellen eine neue „Extended VMSAv7 MMU“ mit Large Physical Address Extensions (LPAE). Damit arbeitet die MMU mit drei Seitentabellen, um mit normalerweise 40 Bits bis zu 1 TB Speicher adressieren zu können.[35][36]

Die achte Version der Arm-Architektur wurde im Oktober 2011 vorgestellt. Mit Armv8-A wurde erstmals von ARM eine 64-Bit-Architektur für die Datenverarbeitung und Speicheradressierung realisiert. Die Kompatibilität zur vorhandenen 32-Bit-Software sollte dabei aufrechterhalten werden. Armv8 ist abwärtskompatibel bis hin zu ARMv5. Es existieren zwei unabhängige Ausführungsmodi: AArch32 für die Verarbeitung von 32-Bit-Software und AArch64 für die Verarbeitung von 64-Bit-Software. Im AArch64-Modus kommt ein neuer Befehlssatz – A64 genannt – zum Einsatz, während der AArch32-Modus den herkömmlichen ARM-Befehlssatz unterstützt.[37][38] Mit ARMv8-A machte ARM VFPv3/v4 und SIMD (NEON) obligatorisch und ergänzte Kryptographie-Instruktionen für AES und SHA-1/SHA-256.

Im Oktober 2012 stellte ARM mit dem Cortex-A53 und Cortex-A57 die ersten Prozessoren vor, die Armv8 implementieren.[39] Die erste Fremdimplementierung vom Armv8 erfolgte für die CPU-Kerne des X-Gene-SoC der Firma Applied Micro Circuits Corporation (AMCC). X-Gene wurde im Juni 2013 vorgestellt und wird vom Hersteller als „Server-on-a-Chip“-Lösung vermarktet.[3] Das erste Mobilgerät mit einem auf Armv8-basierenden SoC ist das im September 2013 vorgestellte iPhone 5s. Das verbaute SoC integriert zwei von Apple entworfene CPU-Kerne namens Cyclone.[4] Qualcomm entwickelte auf der Grundlage von Armv8 die CPU-Architektur Kryo. Ein SoC mit solchen CPU-Kernen wurden erstmals 2015 vorgestellt. Qualcomm verspricht für Kryo eine höhere Leistung und Energieeffizienz gegenüber dem Arm Cortex-A57.[40]

ARM entwickelte mehrere Erweiterungen für Armv8-A: Armv8.1-A (Dezember 2014),[41] Armv8.2-A (Januar 2016),[42] Armv8.3-A (Oktober 2016),[43] Armv8.4-A (November 2017),[44] Armv8.5-A (September 2018),[45] Armv8.6-A (August 2019)[46] und Armv8.7-A (Dezember 2020).[47]

Die neunte Version der Arm-Architektur wurde im März 2021 vorgestellt. Mit Armv9-A setzt Arm auf der Basis von Armv8.5-A auf, die Erweiterungen für Memory Tagging (MTE) und Transactional Memory (TME) werden Pflicht, ebenso Scalable Vector in der Version 2 (SVE2) bei Erhalt der Kompatibilität zu NEON. Neu ist auch das Sicherheitskonzept Realms. Die Kompatibilität zur vorhandenen AArch32-Software wurde auf Applikationsebene beschränkt (EL0) und ist nur noch optional. So wie Armv9-A eine volle Implementierung von Armv8.5-A voraussetzt, wird Armv9.1-A nach einer vollen Implementierung von Armv8.6-A und Armv9.2-A nach einer von Armv8.7-A verlangen.[48][49]

ARM Ltd. verkauft neben den ARM-CPU-Kernen auch Erweiterungen als synthetisierbare Makrozellen für den SoC-Entwurf, unter anderem Memory Management Units, Floating-Point-Coprozessoren sowie Signalprozessor-Erweiterungen (Piccolo).

Folgende Unternehmen haben die Arm-Architektur von ARM Ltd. lizenziert:

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.