Arm Cortex-M (in älterer Schreibweise ARM Cortex-M) ist eine Familie von IP-Cores primär für 32-Bit-Mikrocontroller, die vom Unternehmen ARM entwickelt wird und an verschiedene Hersteller lizenziert wird. Der Kern stellt eine Reduced Instruction Set Computer (RISC) dar, ist ein Teil der ARMv6- bzw. Armv7-Architektur[1] und unterteilt sich in aufsteigender Komplexität in die Einheiten Cortex-M0,[2] Cortex-M0+,[3] Cortex-M1,[4] Cortex-M3,[5] Cortex-M4[6], Cortex-M7 und die auf der Armv8-Architektur basierenden Cortex-M23,[7] und Cortex-M33.[8]

Allgemeines

ARM Limited stellt selbst keine Mikroprozessoren bzw. Microcontroller her, sondern lizenziert den Kern an Hersteller und Chipproduzenten, sogenannte integrated device manufacturers (IDM), welche den eigentlichen ARM-Kern um eigene und herstellerspezifische Peripherie wie z. B. Controller Area Network (CAN), Local Interconnect Network (LIN), Universal Serial Bus (USB), I²C-Bus, Serial Peripheral Interface (SPI), Serielle Schnittstellen, Ethernet-Schnittstellen, Pulsweitenmodulation-Ausgänge, Analog-Digital-Wandler, Universal Asynchronous Receiver Transmitter (UART) und viele weitere erweitern. Diese Einheiten werden über den Advanced Microcontroller Bus Architecture (AMBA) an den ARM-Kern angeschlossen. ARM Limited bietet für den Kern verschiedene Lizenzmodelle an, welche sich in den Kosten und Umfang der zur Verfügung gestellten Daten unterscheiden. In allen Fällen wird das Recht gewährt, eigene Hardware mit ARM-Prozessoren frei vertreiben zu dürfen.

Die „Arm Cortex-M“-Prozessoren sind für den Lizenznehmer als IP-Core in der Hardwarebeschreibungssprache Verilog verfügbar und können mittels Logiksynthese als digitale Hardwareschaltung abgebildet werden, um dann entweder in Field Programmable Gate Arrays (FPGAs) oder Anwendungsspezifische integrierte Schaltungen (ASICs) eingesetzt zu werden. Je nach Lizenzmodell ist entweder die Verwendung des IP-Core gestattet (IP-Core Lizenz) oder aber es kann eine vollkommen neue, eigene Mikroarchitektur entwickelt werden, die die ISA von ARM implementiert (Architektur-Lizenz). Bei Besitz beider Lizenzen ist auch das Erweitern und Verändern der IP-Cores möglich. Vorteile der Architekturlizenz sind, dass für Hersteller neben der Integration eigener Peripherie auch andere Erweiterungen wie eigene Maschinenbefehle, Integration spezieller Debugschnittstellen oder aufgrund einer eigenen Architektur eine Optimierung für einen bestimmten Einsatzzweck (wie beispielsweise Mobilgeräte) möglich werden.

Befehlssatz

Die Prozessoren Cortex-M0 und M1 basieren auf einer ARMv6-M Architektur,[9] die Cortex-M3 auf einer Armv7-M Architektur,[10] und die Cortex-M4 sowie Cortex-M7 auf einer Armv7E-M Architektur.[10] Die Unterschiede betreffen primär den Befehlssatz und die zur Verfügung stehenden Maschinenbefehle. Die Linien sind so festgelegt, dass die binären Maschinenbefehle aufwärts kompatibel sind, das heißt, ein Maschinenprogramm von einem Cortex-M0 oder M1 ist ohne Veränderung auch auf einem Cortex-M3, M4 oder M7 lauffähig. Umgekehrt können nicht alle Befehle des Cortex-M3, M4 oder M7 auf der Cortex-M0 oder M1 ausgeführt werden.[9][10]

Alle Prozessoren aus der Cortex-M-Familie unterstützen die Basisbefehle aus dem so genannten Thumb-Befehlssatz, dem Thumb-2-Befehlssatz, und bieten zusätzlich eine Multipliziereinheit in Hardware. M0 und M1 fehlen allerdings im Thumb-Befehlssatz neuere Erweiterungen wie die Befehle CBZ, CBNZ und IT, welche erst in der später entwickelten Armv7-M-Architektur verfügbar sind. Und der Thumb-2-Befehlssatz ist auf einige wenige Befehle wie BL, DMB, DSB, ISB, MRS und MSR limitiert.[9][10] Die Einschränkungen bei M0 und M1 sind Folge der Vorgabe, die Chipfläche möglichst klein zu halten.

Cortex-M3, mit größerer Chipfläche, umfasst den vollständigen Thumb- und Thumb-2-Befehlssatz, bietet darüber hinaus einige spezielle Instruktionen, eine eigene Divisionseinheit in Hardware und kann mathematische Befehle wie Addition statt mit Überlauf auch mit Sättigung behandeln, was insbesondere im Bereich der Signalverarbeitung von Bedeutung ist. Cortex-M4 erweitert diese Möglichkeiten um einige spezielle Befehle, wie sie bei digitalen Signalprozessoren (DSP) üblich sind, und bietet optional eine Gleitkommaeinheit für die Bearbeitung von Gleitkommazahlen nach der Norm IEEE 754 für einfache Genauigkeit.[9][10] Der Cortex-M7 erweitert die Gleitkommaeinheit für die Bearbeitung von Gleitkommazahlen für doppelte Genauigkeit.[11]

| ARM Cortex-M | Thumb | Thumb-2 | Zyklen Hardware- Multiplizierer | Hardware- Dividierer | DSP- Erweite- rung | Sättigungs- arithmetik | Gleit- komma- einheit | Trust Zone | ARM- Architektur |

|---|---|---|---|---|---|---|---|---|---|

| Cortex-M0 | größten- teils | Subset | 1 oder 32 | nein | nein | nein | nein | nein | ARMv6-M[9] |

| Cortex-M1 | 3 oder 33 | nein | nein | nein | nein | nein | ARMv6-M[9] | ||

| Cortex-M3 | komplett | komplett | 1 | ja | nein | teil- weise | nein | nein | Armv7-M[10] |

| Cortex-M4 | 1 | ja | ja | ja | optional | nein | Armv7E-M[10] | ||

| Cortex-M7 | 1 | ja | ja | ja | optional | nein | Armv7E-M[10] | ||

| Cortex-M23 | 1 oder 32 | ja | nein | nein | nein | ja | Armv8-M Baseline[12] | ||

| Cortex-M33 | 1 | ja | ja | ja | optional | ja | Armv8-M[12] |

Die meisten Cortex-M3 und -M4-Chips bieten Bit-Banding. Dies bedeutet, dass bestimmte Bits im Speicher auf eine eigene Word-Adresse gemappt und dadurch einfacher angesprochen werden können. Es ist nicht zu verwechseln mit Bit-Banging. Ob die Funktion aber auf einer konkreten Cortex-M-Implementierung tatsächlich vorhanden ist, sollte im Einzelfall geprüft werden.[13]

Typen

Cortex-M0

Besonderheiten

Besonderheiten des Cortex-M0 sind:

- ARMv6-M-Architektur[9]

- Von-Neumann-Architektur (anders als M3 und M4)[14]

- Wake-Up-Interrupt-Controller[14]

- Befehlssatz

- Thumb – fast vollständig bis auf CBZ, CBNZ, IT.

- Thumb-2 – Teilmenge bestehend aus BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit-Multipliziereinheit, zur Synthese wählbar mit einem Zyklus, was eine größere Chipfläche bedingt, oder mit 32 Zyklen und weniger Chipfläche.

- 3-stufige Pipeline

Implementierungen

Unter anderem bieten folgende Halbleiterhersteller Cortex-M0 basierende Mikrocontroller an:

- Infineon: XMC1000 Familie

- nuvoTon: NuMicro-Familie

- NXP: LPC11xx- und LPC12xx-Familien

- STMicroelectronics: STM32-F0-Familie

- Toshiba: TX00-Familie

Cortex-M0+

Besonderheiten

Besonderheiten des Cortex-M0+ sind:

- ARMv6-M-Architektur[9]

- Von-Neumann-Architektur (anders als M3 und M4)[15]

- Wake-Up-Interrupt-Controller[15]

- Interrupt-Vektor-Tabellen-Verschiebung ins RAM[15]

- Befehlssatz

- Thumb – fast vollständig bis auf CBZ, CBNZ, IT.

- Thumb-2 – Teilmenge bestehend aus BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit-Multipliziereinheit, zur Synthese wählbar mit einem Zyklus, was eine höhere Chipfläche bedingt, oder mit 32 Zyklen und weniger Chipfläche.

- 2-stufige Pipeline

Implementierungen

Unter anderem bieten folgende Halbleiterhersteller Cortex-M0+ basierende Mikrocontroller an:

- Freescale: Kinetis-KL-Familie

- Microchip/Atmel: SAM-D20/21- und SAM-D10/11-Familie

- NXP: LPC800-Familie

- Renesas: Synergy-Familie (S1)

- Raspberry Pi Foundation: RP2040

- Silicon Laboratories: Zero-Gecko-Familie (EFM32ZG)

- Spansion/Cypress: FM0+-Familie

- STMicroelectronics: STM32L0-, STM32C0- und STM32G0-Familien

- Texas Instruments: MSPM0L-Familie

Cortex-M1

Besonderheiten

Besonderheiten des Cortex-M1 sind:

- ARMv6-M-Architektur[9]

- Befehlssatz

- Thumb – fast vollständig bis auf CBZ, CBNZ, IT.

- Thumb-2 – Teilmenge bestehend aus BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit-Multipliziereinheit, zur Synthese wählbar mit einem Zyklus, was eine höhere Chipfläche bedingt, oder mit 32 Zyklen und weniger Chipfläche.

Implementierungen

Unter anderem bieten folgende Halbleiterhersteller von Field Programmable Gate Array (FPGA) sogenannte Soft-Cores für ihre Logikbausteine an:

Cortex-M3

Besonderheiten

Besonderheiten des Cortex-M3 sind:[5]

- Armv7-M-Architektur[10]

- Befehlssatz

- vollständiger Thumb-Befehlssatz

- vollständiger Thumb-2-Befehlssatz

- 32-bit-Multipliziereinheit mit einem Zyklus, 2 bis 12 Zyklen langer Divisionsbefehl, Mathematische Funktionseinheit mit Überlauf- oder Sättigungseigenschaft.

- 3-stufige Pipeline mit Sprungvorhersage

- 1 bis 240 physikalische Hardwareinterrupt, eine spezielle Form von Interrupts mit 12 Zyklen Latenz.

- Verschiedenartiger Bereitschaftsbetrieb (Sleep Modes)

- Speicherschutzeinheit (MPU) mit 8 Regionen als Option

- 1,25 DMIPS pro MHz Taktfrequenz

- herstellbar mit 90 nm-Halbleitertechnologie.[16]

- Fläche am Chip für den Kern: 0,12 mm²

Implementierungen

Unter anderem bieten folgende Halbleiterhersteller Cortex-M3 basierende Mikrocontroller an:

- Actel: SmartFusion-Familie

- Microchip/Atmel: SAM3-Familie

- Cypress Semiconductor: PSoC 5

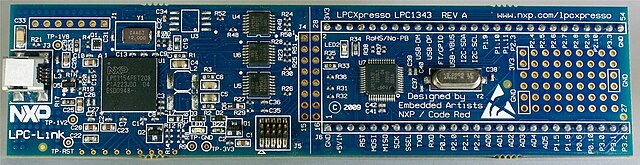

- NXP: LPC13xx, LPC15xx, LPC17xx, LPC18xx Familien

- Silicon Laboratories: Tiny Gecko (EFM32TG), Gecko (EFM32G), Leopard Gecko (EFM32LG) und Giant-Gecko Familien (EFM32GG)

- Spansion/Cypress: FM3 Familie

- STMicroelectronics: STM32 F2, F1, L1, W Familien

- Texas Instruments: Stellaris, TMS470, und einige Prozessoren aus der OMAP4-Familie

- Toshiba: TX03 Familie

Cortex-M4

Besonderheiten

Im Aufbau entspricht der Cortex-M4 einem M3, welcher um spezielle DSP-Befehle und optional eine Gleitkommaeinheit erweitert ist. Cortex-M4 mit Gleitkommaeinheit wird als Cortex-M4F bezeichnet. Besonderheiten des Cortex-M4 sind:[6]

- Armv7E-M Architektur[10]

- Befehlssatz

- vollständiger Thumb-Befehlssatz

- vollständiger Thumb-2-Befehlssatz

- 32-bit-Multipliziereinheit mit einem Zyklus, 2 bis 12 Zyklen langer Divisionsbefehl, mathematische Funktionseinheit mit Überlauf- oder Sättigungseigenschaft.

- DSP-Erweiterungen: 16/32-bit MAC-Befehl mit einem Zyklus, 8/16-Bit SIMD-Arithmetik.

- optionale Gleitkommaeinheit mit der Bezeichnung FPv4-SP, IEEE-754 kompatibel.

- 3-stufige Pipeline mit Sprungvorhersage

- 1 bis 240 physikalische Hardwareinterrupt, eine spezielle Form von Interrupts mit 12 Zyklen Latenz.

- verschiedenartiger Bereitschaftsbetrieb (Sleep Modes)

- Speicherschutzeinheit (MPU) mit 8 Regionen als Option

- 1,25 DMIPS pro MHz Taktfrequenz (1,27 DMIPS / MHz mit FPU)

Implementierungen

Unter anderem bieten folgende Halbleiterhersteller Cortex-M4 basierende Mikrocontroller an:

- Microchip/Atmel: SAM4-Familie (Cortex-M4)

- Infineon: XMC4000-Familie (Cortex-M4F)

- NXP: Kinetis-Familie (Cortex-M4 und Cortex-M4F), LPC40xx- und LPC43xx-Familien (Cortex-M4)

- Renesas: Synergy-Familie (S3, S5 und S7), RA-Familie (RA4 und RA6)

- Silicon Laboratories: Pearl-Gecko-Familie (EFM32PG, Cortex-M4) und Wonder Gecko Familie (EFM32WG, Cortex-M4F)

- Spansion/Cypress: FM4-Familie (Cortex-M4F)

- STMicroelectronics: STM32-F4, L4-, F3-, G4-Familien (Cortex-M4F)

- Texas Instruments: Stellaris-LM4F- und Tiva-TM4C-Familie (Cortex-M4F)

- Toshiba: TX04-Familie (Cortex-M4F)

Cortex-M7

Besonderheiten

Im Vergleich zum Cortex-M4 wurde der M7 mit einer längeren Dual-Issue-Pipeline für höhere Taktfrequenzen, einem neu konzipierten Speichersystem u. a. mit L1-Caches und TCMs, einer Verdoppelung der DSP-Performance gegenüber dem M4 und einem optionalen Lockstep ausgestattet. Besonderheiten des Cortex-M7 sind:[11]

- Armv7E-M Architektur[10]

- Befehlssatz

- vollständiger Thumb-Befehlssatz

- vollständiger Thumb-2-Befehlssatz

- L1-Caches für Befehle und Daten von jeweils 4–64 kB

- TCM für Befehle und Daten jeweils 0–16 MB

- insgesamt 6 Speicherschnittstellen, davon 2 × 64 bit und 4 × 32 bit

- 32-bit-Multipliziereinheit mit einem Zyklus, 2 bis 12 Zyklen langer Divisionsbefehl, mathematische Funktionseinheit mit Überlauf- oder Sättigungseigenschaft.

- DSP-Erweiterungen: 16/32-bit MAC-Befehl mit einem Zyklus, 8/16-Bit SIMD-Arithmetik.

- Gleitkommaeinheit mit der Bezeichnung FPv5, IEEE-754 kompatibel, mit Instruktionen für einfache Genauigkeit (32 Register à 32 bit) oder optional, je nach Implementierung, auch doppelte Genauigkeit (16 Register à 64 bit).[17]

- 6-stufige Dual-Issue-Pipeline mit Sprungvorhersage

- 1 bis 240 physikalische Hardwareinterrupt, eine spezielle Form von Interrupts mit 11–12 Zyklen Latenz.

- verschiedenartiger Bereitschaftsbetrieb (Sleep Modes)

- Speicherschutzeinheit (MPU) mit 8 oder 16 Regionen als Option[18]

- optional Lockstep mit zwei unabhängig arbeitenden Cores

- maximale Taktfrequenz 1 GHz

- 2,14 DMIPS pro MHz Taktfrequenz

Implementierungen

Bislang bieten nur wenige Hersteller Cortex-M7 basierende Mikrocontroller an:

Entwicklungswerkzeuge

Als integrierte Entwicklungsumgebungen steht unter anderen die GNU Toolchain mit Eclipse zur Verfügung. Daneben gibt es noch verschiedene kommerzielle Angebote beispielsweise von IAR oder Keil. Als Betriebssysteme können unter anderem Echtzeitbetriebssysteme wie embOS,[23] FreeRTOS, OpenRTOS, SafeRTOS oder SCIOPTA[24] verwendet werden. Auf Prozessoren mit externem Speicherinterface ist es auch möglich, µClinux auszuführen. Als Debugger für die JTAG-Schnittstelle sind unter anderem der GNU Debugger in Verbindung mit OpenOCD für die Hardwareanbindung verfügbar.

Die Dokumentation ist sehr umfangreich. Insbesondere sind die Kernfunktionen der Cortex-M-Familie in den Unterlagen von ARM beschrieben und für alle Implementierungen identisch. Die diversen konkreten Hardwareimplementierungen und herstellerspezifische Erweiterungen sind hingegen in den jeweiligen Herstellerunterlagen beschrieben.

Literatur

- Joseph Yiu: The Definitive Guide to the ARM Cortex-M0. 2. Auflage. Newnes, 2011, ISBN 978-0-12-385477-3, S. 552.

- Joseph Yiu: The Definitive Guide to the ARM Cortex-M3. 2. Auflage. Newnes, 2009, ISBN 978-1-85617-963-8, S. 479.

Weblinks

- ARM Cortex-M Website

- Quick Reference Cards für die Befehlssätze: Thumb (PDF; 127 kB), ARM and Thumb-2 (PDF; 226 kB), Vector Floating Point (PDF; 99 kB)

| Cortex-M-Serie | ARM-Website | ARM-Core | Arm-Architektur |

|---|---|---|---|

| M0 | M0 | Cortex™-M0 Revision: r0p0 - Technical Reference Manual (PDF; 472 kB) | ARMv6-M |

| M0+ | M0+ | Cortex-M0+ Revision: r0p1 Technical Reference Manual (PDF; 427 kB) | ARMv6-M |

| M1 | M1 | Cortex™-M1 Revision: r1p0 - Technical Reference Manual (PDF; 943 kB) | ARMv6-M |

| M3 | M3 | Cortex™-M3 Revision: r2p1 - Technical Reference Manual (PDF; 889 kB) Cortex™-M3 Revision: r1p1 - Technical Reference Manual (PDF; 2,1 MB) | Armv7-M |

| M4 | M4 | Cortex®-M4 Revision: r0p1 - Technical Reference Manual (PDF; 813 kB) Cortex™-M4 Technical Reference Manual ARM DDI 0439B Errata 01 (PDF; 121 kB) | Armv7E-M |

| M7 | M7 |

Einzelnachweise

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.