Media-independent interface

MAC-PHY間接続 ウィキペディアから

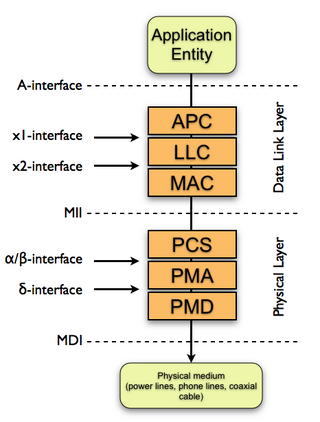

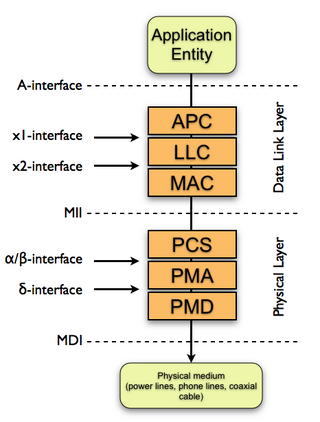

MII (Media-independent Interface または Medium-independent Interface, 「伝送媒体に依存しないインタフェース」の意)は、イーサネットにおいてMAC (データリンク層デバイス)とPHY (物理層デバイス)との接続部分を指す[1]。本稿では以下の拡張版を含めて記述する。

- MII - 100Mbps通信用途

- RMII (reduced MII) - 100Mbps通信用途

- GMII (gigabit MII) - 1Gbps通信用途

- RGMII (reduced gigabit MII) - 1Gbps通信用途

- SGMII (serial gigabit MII) - 1Gbps通信用途

- QSGMII (quad serial gigabit MII) - 5Gbps通信用途

- XGMII (10-gigabit MII) - 2.5Gbps・5Gbps・10Gbps通信用途

概要

MIIはさまざまなタイプのPHYをMACに接続するのに使われる。MIIがあることで、MAC側の回路を再設計や交換せずとも、ツイストペアケーブル・光ファイバーなどの多種多様な伝送媒体を接続するPHYを使用できる。名称に"Media-independent" (媒体に依存しない)とあるように、MIIによって伝送媒体とは無関係に、任意のMACを任意のPHYと組み合わせて使える[2]。MIIとは対照的に、伝送媒体を接続する部分にはMedium-dependent interface (MDI)が設けられている。

MIIの仕様は1995年に100Mbps通信規格であるIEEE 802.3u (ファーストイーサネット)で初めて規定された[3]。当時は主流のPHY規格が複数あり、初期には外部PHYにMII配線したコネクタを接続するために、マザーボードにCNRスロット(CNRコネクタ Type B)が備え付けられているものがあった[4]。現在はMACとPHYが同一基板上に実装されることが一般的であり、MIIは機器内部における回路基板上のチップ間インタフェースとして扱われる。

イーサネットの高速化に伴い、1998年に1Gbps通信規格が登場した際も同様の目的のインタフェースとしてGMIIなどが用いられている[5]。さらに高速通信になると、PHYとMACの接続を切り離してPHYを差し替えることが現実的でなくなり、MIIの代わりにPHYの一部のみを置き換える要求が高まった。10Gbps以上の通信ではこのような目的のインタフェースとして、10Mbps通信の時代にPHYの延伸として使われていたAttachment Unit Interface (AUI)の名称が再び用いられるようになっている[6]。

初期 MII

要約

視点

IEEE 802.3uによる初期のMIIでは、送受4ビットずつの送受バスを25 MHzのクロックで動作させ、合計100 Mbpsで通信する。また、10Mbps通信との後方互換性も考慮されている。

MIIには下表の18個の信号が必要である。このうちMDCとMDIOは複数のPHYで共有できるが、それ以外の16配線はポートごとに必要である。これは特に多ポート機器では問題となり、例えば8ポートスイッチでは、8つのPHYに対して 8×16 + 2 = 130本を配線することになる。

| 種別 | 信号名 | 説明 | 方向 |

|---|---|---|---|

| 送信 | TX_CLK | 送信クロック | PHY→MAC |

| TXD0 | 送信データビット0(先頭ビット) | MAC→PHY | |

| TXD1 | 送信データビット1 | MAC→PHY | |

| TXD2 | 送信データビット2 | MAC→PHY | |

| TXD3 | 送信データビット3 | MAC→PHY | |

| TX_EN | 送信中 | MAC→PHY | |

| TX_ER | 送信エラー(オプション) | MAC→PHY | |

| 受信 | RX_CLK | 受信クロック(受信信号から復元) | PHY→MAC |

| RXD0 | 受信データビット0(先頭ビット) | PHY→MAC | |

| RXD1 | 受信データビット1 | PHY→MAC | |

| RXD2 | 受信データビット2 | PHY→MAC | |

| RXD3 | 受信データビット3 | PHY→MAC | |

| RX_DV | 受信中 | PHY→MAC | |

| RX_ER | 受信エラー | PHY→MAC | |

| CRS | キャリア検知(半二重通信のみ) | PHY→MAC | |

| COL | 衝突検出(半二重通信のみ) | PHY→MAC | |

| 管理 | MDIO | 管理データ (Management Data Input/Output) | MAC⇔PHY |

| MDC | 管理データ用クロック (Management Data Clock) | MAC→PHY |

それぞれのピンについて概説する。

- TXD[3..0], RXD[3..0]では、イーサネットの主信号を送受する。信号はイーサネットフレームとして伝送され、データとしてプリアンブル、開始フレーム識別子(SFD)、イーサネットヘッダ、ペイロード、巡回冗長検査(CRC)を含んだ形をとる。

- TX_CLK (送信クロック)はPHYからMACにクロックを与えるもので、100Mbps通信の場合は25MHz、10Mbps通信の場合は2.5MHzのクロック信号が供給される[8]。TX_CLKの立ち上がりエッジのタイミングでMACがTXD[3..0]にデータを送る。この構成により、MACはリンク速度を意識せずに動作することができる。

- TX_EN (送信中)ピンは、フレーム送信中はハイに、アイドル状態のときはローに保持される。

- TX_ER (送信エラー)は、フレーム送信中に発生することがある。これは、PHYにフレームを故意に破棄するよう要求して、有効なフレームとして受信されるのを防止するためのものである。これはオプションのため MAC にその機能がないこともあり、その場合はローに固定する必要がある。さらに、主信号の送信データTXD[3..0]を特殊な用途に使っていることを示すために、このTX_ERを故意に発生させる方法をとるものがある。例えばEEE対応のPHYでは、特殊シンボル

0b0001を使って低電力モードに入るように要求するときに「TX_ENをロー、TX_ERをハイ」とするように規定されている[9]。

- RX_ER (受信エラー)は、オプションではなく必須ピンであり、受信信号が有効データとして復号できなかったことを示す。またTX_ERと同様、特殊シンボル

0b0001(対向がEEE低電力モードにある)と0b1110(false carrier)が定義されており、これらの受信時にRX_ERをハイにする[10]。

- RX_CLK (受信クロック)は、フレーム受信中に入力信号から復元される。伝送媒体に信号が流れていないときは、PHYが代わりに自身のクロックを供給する。

- RX_DV (受信中)は、フレーム受信中にハイを維持する。受信開始直後からハイになる必要はないが、遅くともプリアンブル後のSFDが届くまでにはハイを示す必要がある[11]。

- CRS (キャリア検知)・COL (衝突検出)は、半二重通信(CSMA/CD)でのみ用いるもので、RX_CLK とは無関係に動作する。CRSは、送受信中または他機器による伝送路占有の検出時にハイにする。COLは、衝突検出や衝突継続中にハイにする。また、MAC側はCOLに弱いプルアップを接続しており、COLハイとCRSローとの組み合わせ(PHY側がこのパターンで動作することはない)をPHYの接続検出に使っている[12]。

- MDIO (管理データI/O)・MDC (管理データ用クロック) は 2線シリアルバスで、MDIOレジスタへアクセスして状態取得や設定をするために使う。詳細は次節。

MDIO レジスタ

MDIO (Management Data Input/Output)は、PHYの各種設定や状態取得が可能な管理用インタフェース。I2Cに似た2線シリアルバス(MDIO・MDC)を用いて、内蔵の16ビットレジスタにアクセスする。

100Mbps・1Gbps通信用のPHYは、下表のような32個のレジスタを備えている。前半のアドレス0~15のレジスタはその書式が規定されているが、後半のアドレス16~31のレジスタはPHY固有となっている[13]。

| アドレス | 内容 |

|---|---|

| 0 | 基本設定 |

| 1 | 基本状態 (以下は主な16ビット値)

|

| 2-3 | PHY ID |

| 4 | オートネゴシエーション 送信ベースページ設定 |

| 5 | オートネゴシエーション 受信ベースページ状態 |

| 6 | オートネゴシエーション 状態 |

| 7 | オートネゴシエーション 送信ネクストページ設定 |

| 8 | オートネゴシエーション 受信ネクストページ状態 |

| 9 | マスター/スレーブ 設定 |

| 10 | マスター/スレーブ 状態 |

| 11 | PoE 給電設定 |

| 12 | PoE 給電状態 |

| 13 | MDIO設定 |

| 14 | MDIO状態 |

| 15 | 1Gbps状態 |

| 16-31 | PHY固有レジスタ |

10Gbps通信および後発規格用のPHYにもMDIOレジスタが用意されているが、初期のものから大きく拡張されており、管理用に65536個の16ビットレジスタが実装可能となっている[14]。

RMII

要約

視点

RMII (Reduced MII) は、100Mbps通信用途のMIIの一種で、配線数を減らしたもの。下表の9本の配線からなる。この仕様は、1998年にRMIIコンソーシアムによるベンダ間合意によって規定された[15]。

| 種別 | 信号名 | 説明 | 方向 |

|---|---|---|---|

| 送受共通 | REF_CLK | 50MHz クロック | 外部ソース→MAC・PHY または MAC→PHY |

| 送信 | TXD0 | 送信データビット0 | MAC→PHY |

| TXD1 | 送信データビット1 | MAC→PHY | |

| TX_EN | 送信中 | MAC→PHY | |

| 受信 | RXD0 | 受信データビット0 | PHY→MAC |

| RXD1 | 受信データビット1 | PHY→MAC | |

| CRS_DV | CRS(キャリア検知)・RXDV(受信中)の交互出力 | PHY→MAC | |

| RX_ER | 受信エラー(スイッチではオプション) | PHY→MAC | |

| 管理 | MDIO | 管理データ | MAC⇔PHY |

| MDC | 管理データ用クロック | MAC→PHY |

初版 MII から以下の4点が変更された。

- TXCLKとRXCLKを共通のクロックREF_CLKに置き換える。このクロックはPHYへの入力になるため、スイッチなどの多ポート機器内の全てのPHYでクロック信号を共有できる。

- クロックを25MHzから50MHzと倍速にし、主信号を4本から2本に減らす。

- RXDVとCRSを1ピンにまとめる。100Mbps通信では1クロックごと、10Mbps通信では10クロックごとに交互にCRS_DVピンに出力する。

- COLを削除する。

これにより、MIIの18本に対してRMIIでは9本となったが、多ポート機器ではさらに MDIO, MDC, REF_CLKの3本を各PHYで共有できるので、PHYごとに必要なのは6~7本となる。

RMIIでは50MHzのクロックを必要とし、データは1クロックに対し2ビットずつ出力される(MIIでは25MHzで4ビット)。入力信号は立ち上がりエッジでのみ読み取る。

100M・10Mbpsのいずれの通信でも REF_CLK は 50MHz で動作する。そのため10Mbps通信では、送受の出力信号の値を10クロック分維持しておき、入力信号は10クロックに1度だけ読み取る。

制限事項

通信が全二重・半二重のいずれか、また10M・100Mbpsの速度のいずれかを示す信号がなく、これらはMDIO/MDCで設定する必要がある。RMIIの第1.2版では MDIO/MDCはIEEE 802.3u-1995の仕様と同一のものと規定しているが、後のIEEE 802.3改版時にMDIOによるオートネゴシエーション設定が追加されており、旧版規格に基づいた古い設計のPHYには速度と二重通信モードを独自の方法で設定しているものがある。

RX_ER信号をサポートしないMACと接続する場合は、MAC側で受信データのCRCをしないようにエラー時にPHYがデータを置き換えて対処するものがある。

RMIIには COL (衝突検出)がないが、CRS_DV信号からCRS (キャリア検知)だけを取り出して、論理演算 COL = CRS and TX_ENによって求められる。ただし、この方法では MIIと動作が若干異なり、MIIでは送受両方でキャリア検知ができるが、RMIIでは受信のみとなる。その結果、RMIIでは「キャリアなし」「キャリア損失」の2つのエラーを検出できず、10BASE2や10BASE5などのバス共有型の規格に対応できない。

RMIIでは CRS_DVが交互出力である一方で、TX_ENは交互出力ではなく対称的ではないため、2つのPHYをRMIIで背中合わせに直接接続してリピータにすることはできない。National DP83848を使えば、RX_DVだけを取り出して補助信号として出力できる[16]。

信号レベル

TTL信号レベルは5Vまたは3.3Vロジックが使用され、入力の0/1しきい値は0.8V・2.0Vである。入力に5V耐性の規定があるが、実際は5V耐性がないチップがほとんどであり、MAC実装に必要なFPGAにも一般的に5V耐性がない。5V駆動は主に古いMII専用デバイスにのみ見られ、半導体業界のトレンドや、PHYとMACが通常同一基板上にある点を考えると、チップでの対応はおそらく稀である。新しいものでは2.5Vと1.8Vの両方のロジックに対応するチップもある。

RMIIでは、少なくとも規格上は主信号配線を伝送線路ではなく集中定数回路として扱っており、終端処理やインピーダンスの制御は不要である。しかし、初期 MIIでは 68Ωの特性インピーダンスが規定されている[17]。ナショナルセミコンダクタは、MII・RMIIのいずれでもインピーダンス50Ωと直列抵抗33Ωを設けるよう推奨しており、さらにスキューの低減のために配線長は150cm未満、配線長の差を50cm未満に収めたほう良いとしている[18]。

GMII

GMII (gigabit MII) は MII の一種で、1Gbps通信用途のもの。下表の27本の配線からなる。送受それぞれ8本の配線が125MHzで動作し、合計1Gbpsで通信する。10M/100Mbps通信も可能である。 この仕様は、IEEE 802.3z-1998 (1000BASE-X) の Clause 35 で初めて規定された[5]。

| 種別 | 信号名 | 説明 | 方向 |

|---|---|---|---|

| 送信 | GTXCLK | 1Gbps通信用のクロック(125MHz) | MAC→PHY |

| TXCLK | 10Mbps or 100Mbps通信用のクロック (2.5 MHz or 25 MHz) | PHY→MAC | |

| TXD[7..0] | 送信データ | MAC→PHY | |

| TXEN | 送信中 | MAC→PHY | |

| TXER | 送信エラー | MAC→PHY | |

| 受信 | RXCLK | 受信クロック(受信信号から復元) | PHY→MAC |

| RXD[7..0] | 受信データ | PHY→MAC | |

| RXDV | 受信中 | PHY→MAC | |

| RXER | 受信データエラー | PHY→MAC | |

| COL | 衝突検出(半二重通信のみ) | PHY→MAC | |

| CS | キャリア検知(半二重通信のみ) | PHY→MAC | |

| 管理 | MDIO | 管理データ | PHY⇔MAC |

| MDC | 管理データ用クロック | MAC→PHY |

送信クロックは2種類の方式がある。1Gbps通信では、GTXCLKがMACからPHYに供給され、TXD, TXEN, TXER信号はこれに同期する[19]。10M/100Mbps通信の場合は、TXCLK がPHYからMACに供給され、100 Mbps接続では25 MHz、10 Mbps接続では2.5 MHzで動作する。一方で受信クロックはシンプルであり、受信データから復元した RXCLK のみである。その結果として、GTXCLK と RXCLKとが同じタイミングをとるとは限らない。

RGMII

RGMII (reduced gigabit MII)は、1Gbps通信用途の MIIの1つで、配線数を減らしたもの。下表の12本の配線からなる。この仕様は2000年にヒューレット・パッカードが中心となってまとめた規定に基づいている[20]。

| 種別 | 信号名 | 説明 | 方向 |

|---|---|---|---|

| 送信 | TXC | クロック信号 | MAC→PHY |

| TXD[3..0] | 送信データ | MAC→PHY | |

| TX_CTL | 送信中(TXEN)・送信エラー(TXER) | MAC→PHY | |

| 受信 | RXC | 受信クロック(受信信号から復元) | PHY→MAC |

| RXD[3..0] | 受信データ | PHY→MAC | |

| RX_CTL | 受信中(RXDV)・受信エラー(RXER) | PHY→MAC | |

| 管理 | MDIO | 管理データ | MAC⇔PHY |

| MDC | 管理データ用クロック | MAC→PHY |

GMIIと比べると、送受の主信号配線を半減させ、さらに半二重通信用の不要なCSとCOLを削除している。

主信号は、1Gbps通信では立ち上がり・立ち下がりの両方のエッジで読み取ることで実現している。10M・100Mbps通信では従来どおり立ち上がりエッジのみで入力信号を読み取る[21]。

TXC (送信クロック信号)は、GMIIとは異なり常にMAC側から供給される。データとクロックを同時に出力しているため、初期仕様ではこれを読み取る側のセットアップ時間とホールド時間を確保するために、基板配線の引き回しでクロック信号を1.5~2ナノ秒ほど遅延させる必要があった。RGMII 第2.0版では内部遅延(RGMII-ID)のオプションが追加されたため、基板設計でこれを考慮する必要がなくなった。

RX_CTL (受信中・受信エラー)は、立ち上がりエッジでRXDVを、立ち下がりエッジでRXDV xor RXER を示す。TX_CTL (送信中・送信エラー)も同様に、立ち上がりエッジでTXENを、立ち下がりエッジでTXEN xor TXERを示す。これらは1G・100M・10Mbps通信で共通仕様である。

電圧レベルは、RGMII 第1.3版[20]は2.5V CMOSを使用し[22]、RGMII第2版では1.5V HSTLを使用する[23]。

SGMII

SGMII (serial gigabit MII)は、1Gbps通信用途の MIIの1つ。低消費電力な差動シリアルバス(LVDS)を利用して信号数を10に減らしている。この仕様は、1999年にシスコ・システムズが規定したものに基づく[24]。主にSFPトランシーバとの接続において使われる。

データ・クロックとしてそれぞれ1対ずつ差動配線を使うため4配線となり、これが送受で8配線、さらにMDIO/MDCを加えた10配線で構成される。

データ用の差動配線バスは一般にSerDesと呼ばれ、主信号に8b/10b符号を用い、クロック周波数625MHz、データレート1.25Gbpsで動作する。これは1000BASE-Xの伝送路符号と同じものをそのまま基板上に流してMACに引き渡す形になる。GMIIに備えられているTXEN, TXER, RXDV, RXER, COL, CSはPHYの機能の一部をMACが受け持って処理する。クロックは常に625MHzであるため、10M・100Mbps用途では16ビットデータをそれぞれ100回・10回反復して送る。

クロックは出力側で生成する必要があるが、入力のオプションもある。また、CDRによる受信信号からの復元クロックを使うこともできる。

QSGMII

QSGMII (quad serial gigabit MII)は、5 Gbps通信用途のMII。2005年にシスコ・システムズが規定したものに基づく[25]。

SGMIIを4つ組み合わせたものであるが、配線数はSGMIIバス4つ分よりもはるかに少なく、4対のLVDS送受信号と1対のLVDSクロック信号のみで済む。

XGMII

XGMII (10 gigabit MII, "X"はローマ数字で10を意味する) は、10Gbps通信用途の MII。2002年に IEEE 802.3ae で規定された。

72本の配線からなり、156.25MHz (2エッジで312.5 Mbps)で動作する主信号 TXD/RXD 各32本と、制御フロー RXC/TXC 各4本が送受方向にそれぞれ用意されている[26]。配線数の多さから、ほとんどXAUIに置き換えられている。

nGMII

nGMII は、25Gbps以上の高速通信用途のMIIの総称。以下のものが規定されている。

- 25GMII[27] - 25Gbps通信用途

- XLGMII[28] - 40Gbps通信用途 ("XL"はローマ数字で40)

- 50GMII[29] - 50Gbps通信用途

- CGMII[28] - 100Gbps通信用途 ("C"はローマ数字で100)

- 200GMII[30] - 200Gbps通信用途

- 400GMII[30] - 400Gbps通信用途

- 800GMII[31] - 800Gbps通信用途

10GbpsのXGMIIまでは物理的な配線が規定されたものの実装上は内部バスとして扱われたことを反映し、25Gbps以上のMIIはすべて論理インタフェースとして規定された。PHYとMAC間で64ビット単位のデータ送受が規定の速度で可能でさえあれば任意の実装ができるような柔軟性を持たせている。

関連項目

- Attachment Unit Interface (AUI) - 10Mbps通信でMIIとほぼ同様の目的のもの

- XAUI - 10Gbps通信でMIIとほぼ同様の目的のもの

- G.hn - データリンク層と物理層との間のインタフェースを指すのにMIIという用語を使用するITU-T勧告

- デバイス帯域幅の一覧

- SFPトランシーバ

- XFPトランシーバ

出典

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.