プレーナ プロセス(英: Planar process)は、集積回路を製造するために、最初に個々のトランジスタの集合体を作成し、次に、それら個々のトランジスタを相互に接続する際に使用される製造方法である。この工程は、シリコン集積回路(IC)チップ製造の主要な工程で、表面不動態を形成するために熱酸化法を利用する。

プレーナー プロセスは、1959年にフェアチャイルドセミコンダクターでジャン・ヘルニによって開発された。

概要

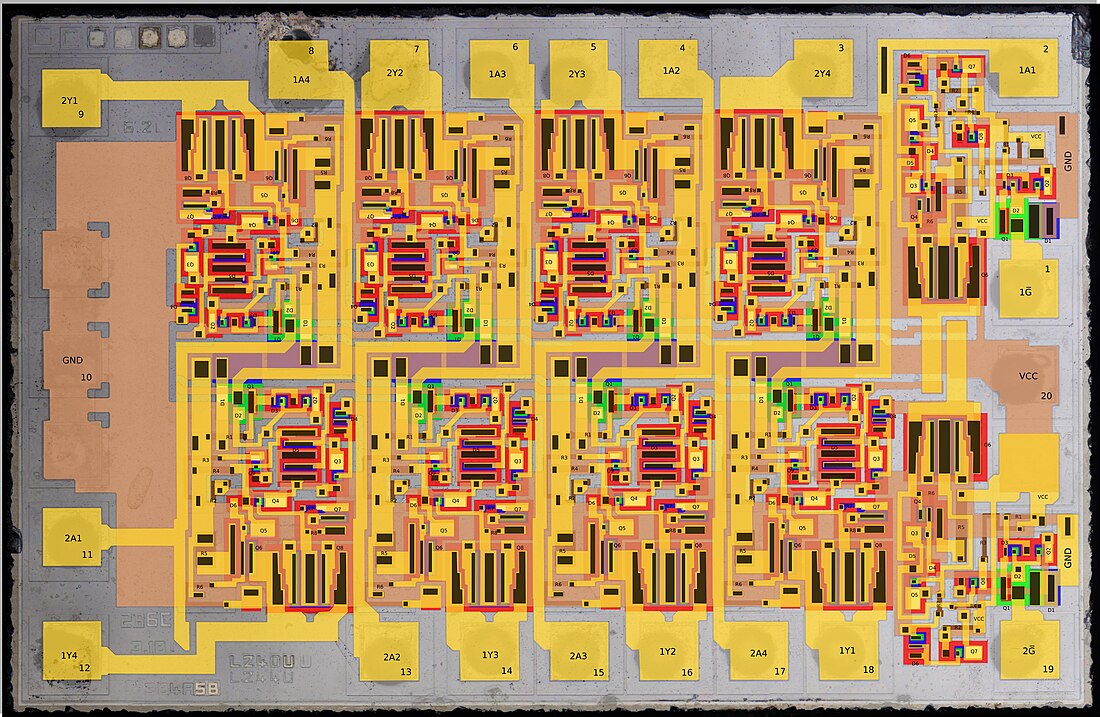

プレーナー プロセスに関して重要な概念は、2次元投影 (平面) で回路を投影することであり、そのためにネガフィルムなどの写真処理の概念を応用して、化学物質の上にフォトマスクに描画された回路パターン投影し露光させる。これにより、シリコン基板上で一連の露出を使用して、二酸化シリコン(絶縁体)またはドープ領域(導体)を作成できる。メタライゼーション[1]の使用、およびpn接合分離と表面不動態化の概念と共に、棒状単結晶シリコンをスライスしてできたウェーハ上に回路を作成することが可能となる。

このプロセスの基本的な手順は、二酸化シリコン(SiO2 ) の酸化、SiO2のエッチング、および熱拡散である。熱拡散では、ウェーハ全体を SiO2層で酸化し、トランジスタへの接続孔をエッチングし、酸化物上に被覆金属膜を堆積させて、手動で配線することなくトランジスタを接続する。

開発史

1958年の米国電気化学学会で、 モハメド・M・アタラは、1957年の ベル電話研究所でのメモに基づいて、熱酸化によるpn接合の表面不動態化に関する論文を発表した[2]。

スイスのエンジニア、ジャン・ヘルニは、この1958年の学会に出席していて、アタラの講演に興味をそそられた。ヘルニは、ある朝、アタラの装置について考えているときに「平面的なアイデア」を思いついた[2]。シリコン表面に対する二酸化シリコンの不動態化効果を利用して二酸化シリコン層で保護されたトランジスタを作ることを考案した[2]。これにより、アタラのアイデアをもとにした、熱酸化膜によるシリコン トランジスタ 不動態化技術の製品実装が初めて成功した[3]。

プレーナー プロセスは、フェアチャイルド セミコンダクターで働いていたときに、「裏切り者8人」の1人であるジャン・ヘルニによって開発され、1959年に登録された最初の特許である[4][5]。

フェアチャイルドの研究者たちは、被覆金属膜の堆積による集積回路の接合方法と、クルト・レホヴェックによるpn接合分離の概念により、単結晶シリコンブールをスライスして作られたウエハー上に回路を作ることに成功した。

1959年、 ロバート・ノイスは ヘルニの研究に基づいて集積回路(IC) の概念を構築した。この IC は、ヘルニの基本構造の上部に金属層を追加して、トランジスタ、コンデンサ、抵抗などのさまざまなコンポーネントを接続することを繰り返しおこなう方法である。プレーナー プロセスは、集積回路の以前の概念よりも優れた集積回路を実装する強力な方法となった[6]。ノイスの発明は、最初のモノリシックIC チップとなった[7][8]。

プレーナ プロセス法によるIC製造の初期の段階では、光源に水銀灯からの近紫外光を使用したフォトリソグラフィプロセスが使用されていた。 2011年には、小さなフィーチャは通常、波長193nm の「ディープ」紫外線リソグラフィで作成されていた[9]。2022年現在、ASML社のNXE型光源機は、スズベースのプラズマ光源によって生成された13.5nm の極端紫外線を使用している。

脚注・参考文献

関連項目

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.