RISC-V

סט פקודות למעבד בקוד פתוח מוויקיפדיה, האנציקלופדיה החופשית

RISC-V (מבוטא בעבריתː ריסק-5) הוא תקן פתוח המגדיר תצורת סט פקודות (ISA) עבור מעבד, על פי העקרונות של "סט פקודות מצומצם" (RISC).

RISC-V כולל תצורת סט פקודות עבוד מעבד בן 32 ביטים, 64 ביטים ו-128 ביטים. כמו כן הוא כלל הרחבות עבור עיבוד מתמטי, פעולות אטומיות, חישובים עם נקודה צפה וחישובים עם נקודה צפה בדיוק כפול.

היסטוריה

תכנון ופיתוח של מעבד דורש ידע והתמחות בתחום התכנון הספרתי, טכנולוגית מהדרים ומערכות הפעלה. חלק מחברות שתכנונו תצורת סט פקודות עבור מעבדים, כגון אינטל, יצרו ומכרו את מעבדים בעצמם על בסיס הטכנולוגיה שפיתחו. חברות אחרות, כגון ARM ו-MIPS טכנולוגיות (אנ'), התבססו על מודל עסקי של מכירת רישיון לשימוש בקניין הרוחני שפיתחו לחברות המפתחות SOC, תוך התחייבות הלקוחות לשמור על סודיות ובכפוף לתשלום תמלוגים.

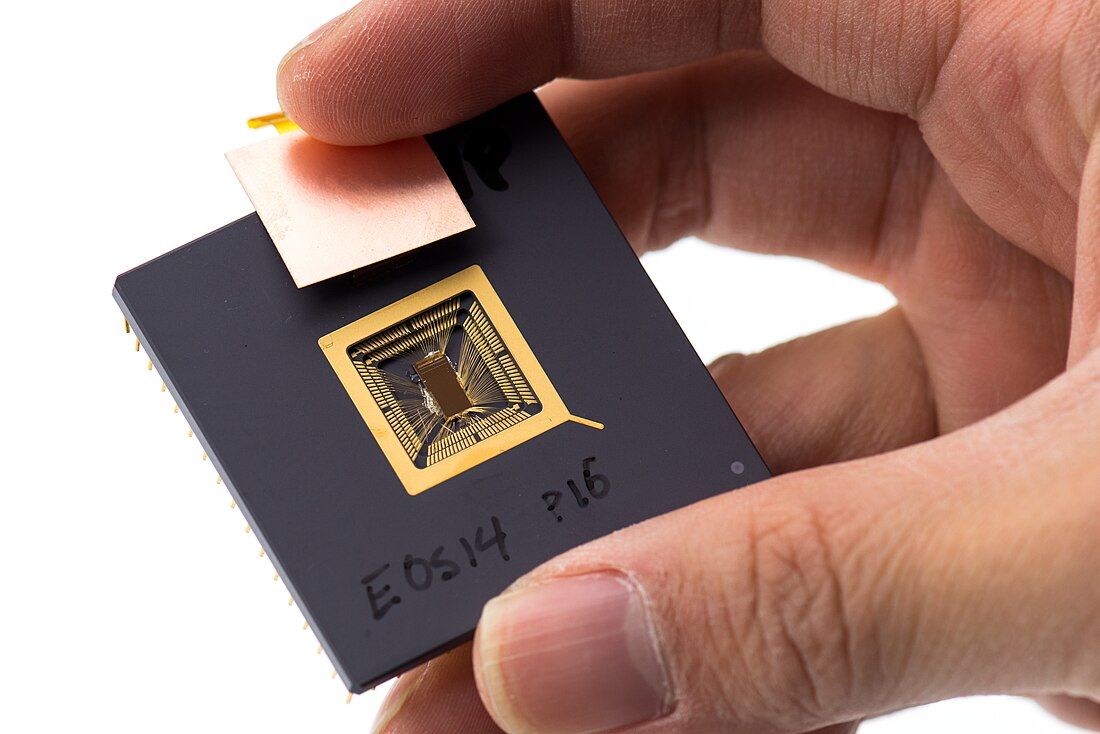

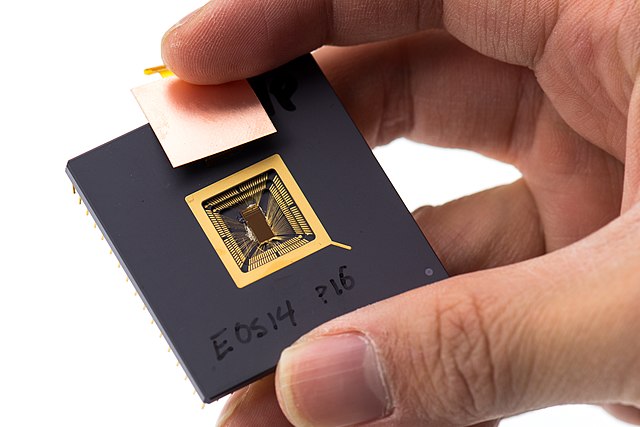

בשנת 1981 נבנה לצרכים מחקריים המעבד הראשון שנקרא RISC באוניברסיטת ברקלי וזכה לשם RISC-I. לאחר מכן נבנה RISC-II. במשך שנות ה-80 של המאה העשרים פותחו גרסאות נוספות שנקראו SOAR ו-SPUR. בשנת 2010 קבוצה באוניברסיטת ברקלי פיתחה מעבד RISC והיא כינתה אותו RISC-V כהמשך לארבעה דגמי ה-RISC שפותחו בעבר.[1][2]

בשנת 2015 הוקמה קרן RISC-V כארגון ללא כוונות רווח שמטרתו, ליצור קהילת קוד פתוח על בסיס סט תצורת הפקודות של RISC̠-V, כך שיוכל להיות משולב במוצרי חומרה או לשמש למחקר אקדמי ללא תשלום תמלוגים. מפתחי RISC-V העבירו את הזכויות על תצורת סט הפקודות שפיתחו לקרן.

בשנת 2020 עבר הארגון מארצות הברית לשווייץ ושינה את שמו לארגון RISC-V הבינלאומי. המעבר בוצע בגלל חשש ששינויים בתקנות הסחר בארצות הברית יפגעו בפעולת הארגון.

קישורים חיצוניים

אתר האינטרנט הרשמי של RISC-V (באנגלית)

אתר האינטרנט הרשמי של RISC-V (באנגלית) אתר האינטרנט הרשמי של RISC-V (ביפנית)

אתר האינטרנט הרשמי של RISC-V (ביפנית) אתר האינטרנט הרשמי של RISC-V (בסינית מפושטת)

אתר האינטרנט הרשמי של RISC-V (בסינית מפושטת)

RISC-V, ברשת החברתית אקס (טוויטר)

RISC-V, ברשת החברתית אקס (טוויטר) RISC-V, סרטונים בערוץ היוטיוב

RISC-V, סרטונים בערוץ היוטיוב- אתר האינטרנט של RISC-V

הערות שוליים

Wikiwand - on

Seamless Wikipedia browsing. On steroids.