SBus

From Wikipedia, the free encyclopedia

SBus is a computer bus system that was used in most SPARC-based computers (including all SPARCstations) from Sun Microsystems and others during the 1990s. It was introduced by Sun in 1989 to be a high-speed bus counterpart to their high-speed SPARC processors, replacing the earlier (and by this time, outdated) VMEbus used in their Motorola 68020- and 68030-based systems and early SPARC boxes. When Sun moved to open the SPARC definition in the early 1990s, SBus was likewise standardized and became IEEE-1496. In 1997 Sun started to migrate away from SBus to the Peripheral Component Interconnect (PCI) bus, and today SBus is no longer used.[1]

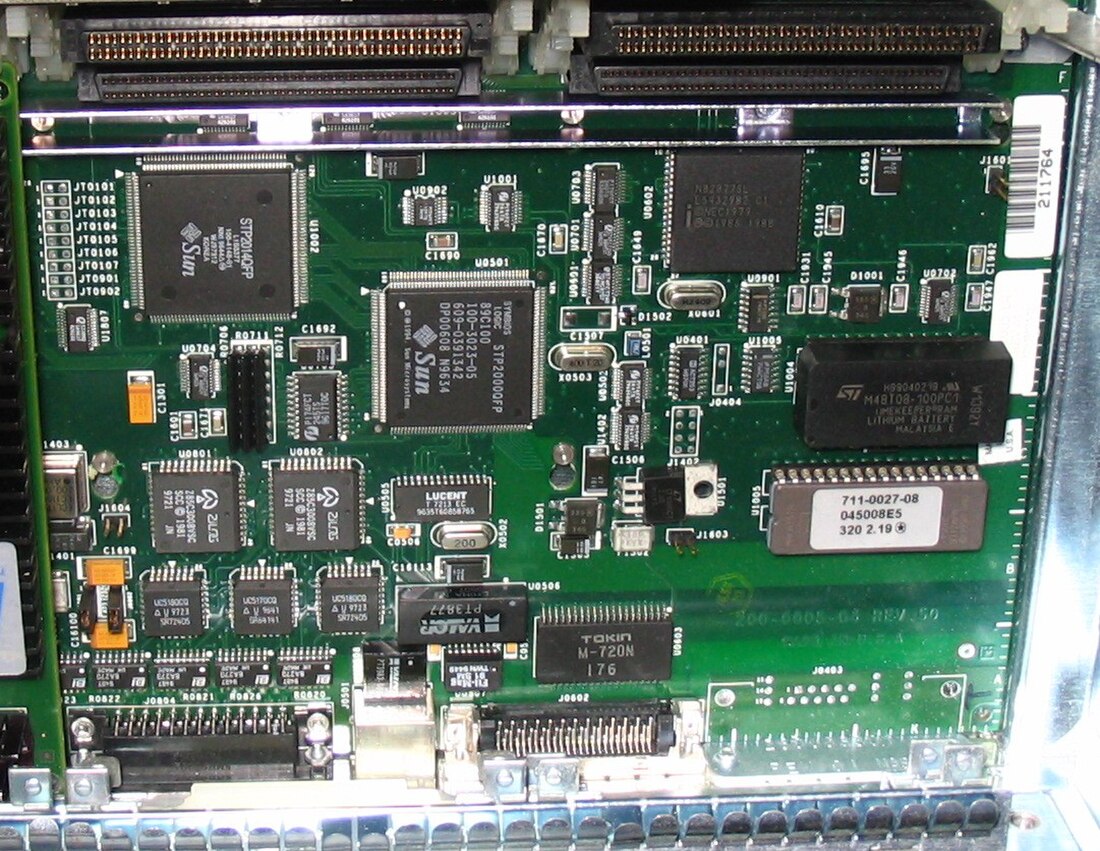

Four SBus connectors (top of photograph) | |

| Year created | 1989 |

|---|---|

| Created by | Sun Microsystems |

| Superseded by | PCI (1997) |

| Width in bits | 32 |

| No. of devices | 8 masters, unlimited slaves |

| Speed | 16.67 MHz - 25 MHz |

| Style | Parallel |

The industry's first third-party SBus cards were announced in 1989 by Antares Microsystems; these were a 10BASE2 Ethernet controller, a SCSI-SNS host adapter, a parallel port, and an 8-channel serial controller.

The specification was published by Edward H. Frank and James D. Lyle.[1] A technical guide to the bus was published in 1992 in book form by Lyle,[2] who founded Troubador Technologies. Sun also published a set of books as a "developer's kit" to encourage third-party products.[3]

At the peak of the market over 250 manufacturers were listed in the SBus Product Directory, which was renamed to the SPARC Product Directory in 1996.

SBus is in many ways a "clean" design. It was targeted only to be used with SPARC processors, so most cross-platform issues were not a consideration. SBus is based on a big-endian 32-bit address and data bus, can run at speeds ranging from 16.67 MHz to 25 MHz, and is capable of transferring up to 100 MB/s. Devices are each mapped onto a 28-bit address space (256 MB). Only eight masters are supported, although there can be an unlimited number of slaves.

When the 64-bit UltraSPARC was introduced, SBus was modified to support extended transfers of a 64 bits doubleword per cycle to produce a 200 MB/s 64-bit bus. This variant of the SBus architecture used the same form factor and was backward-compatible with existing devices, as extended transfers are an optional feature.

SBus cards had a very compact form factor for the time. A single-width card was 83.82 millimetres (3.300 in) wide by 146.7 millimetres (5.78 in) long and is designed to be mounted parallel to the motherboard. This allowed for three expansion slots in the slim "pizza box" enclosure of the SPARCstation 1.[4] The design also allows for double- or triple-width cards that take up two or three slots, as well as double-height (two 3x5 inch boards mounted in a "sandwich" configuration) cards.

SBus was originally announced as both a system bus and a peripheral interconnect that allowed input and output devices relatively low latency access to memory.[5] However, soon memory and central processing unit (CPU) speeds outpaced I/O performance. Within a year some Sun systems used MBus, another interconnection standard, as a CPU—memory bus. The SBus served as an input/output bus for the rest of its lifetime.

See also

References

External links

Wikiwand - on

Seamless Wikipedia browsing. On steroids.