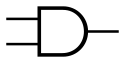

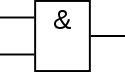

与门(英語:AND gate)是数字逻辑中实现逻辑与的逻辑门,功能见右侧真值表。仅当输入均为高電壓(1)时,输出才为高電壓(1);若输入中至多有一个高電壓时,则输出为低電壓。换句话说,与门的功能是得到两个二进制数的最小值,而或门的功能是得到两个二进制数的最大值。

| 基本逻辑閘 | |

| 緩衝 | 非 |

| 与 | 与非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蘊含 | 蘊含非 |

| 输入 | 输出 | |

| A | B | A AND B |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

概述

下列包括逻辑门的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标(中国大陆)符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑门符号见逻辑门符号表。

若与门的其中一个输入取反则成为禁门(INHIBIT logic gate,INHIBITOR)。

实现

与门是基本的逻辑门,因此大多数半导体制造商都会生产这种集成电路。例如,在TTL集成电路7408和CMOS集成电路4081均由四个2输入与门构成。

|

与门通常用n通道(NMOS)或p通道(PMOS)的MOSFET实现。数字输入a与b引起输出F,这和与门的功能一致。

备选方案

如果没有现成的与门,则可用与非门{x and y=(x nand y)nand (x nand y)}或或非门{(x and y=(x nor x)nor(y nor y)}来实现,因为与非门和或非门被认为是“通用的逻辑门电路”[1],因为通过这两种门电路可以实现其他所有门电路的功能。若用与非门实现与门,则将一个与非门的两个输入结在一起,然後在其输入端接入一个双输入的与非门;若用或非门实现与门,则将两个输入接在一起的或非门分别作另外一个或非门的两个输入,然後在後者的输入接一个输入接在一起的或非门。异或门也可用来实现与门,但很少使用。

参见

参考文献

外部連結

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.

, ...

, ...