Loading AI tools

计算机随机存储器 来自维基百科,自由的百科全书

高頻寬記憶體(英文:High Bandwidth Memory,縮寫HBM)是三星電子、超微半導體和SK海力士發起的一種基於3D堆疊工藝的高效能DRAM,適用於高記憶體頻寬需求的應用場合,與高性能圖形處理器、網路交換及轉發裝置(如路由器、交換器)、高性能數據中心的AI特殊應用集成電路結合使用,在 CPU 中用作包內高速緩存,在即將推出的 CPU 和 FPGA 中用作包內 RAM,還用於某些超級計算機(如 NEC SX-Aurora TSUBASA 和富士通 A64FX)。[1][2]首款HBM內存芯片由SK海力士於2013年生產,[3]首款使用高頻寬記憶體的裝置是AMD Radeon Fury系列顯示核心[4][5]。

2013年10月,高頻寬記憶體正式被JEDEC採納為業界標準。[6]第二代高頻寬記憶體(HBM2)於2016年1月被JEDEC採納。[7]NVIDIA在該年發表的新款旗艦型Tesla運算加速卡 —— Tesla P100、AMD的Radeon RX Vega系列、Intel的Knight Landing也採用了第二代高頻寬記憶體。

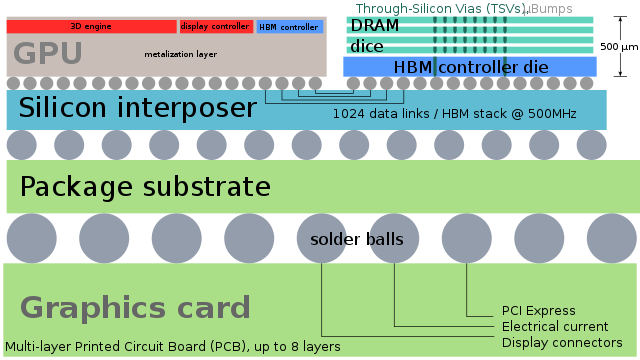

相比較DDR4或GDDR5而言,高頻寬記憶體以更小的體積、更少的功率達到更高的帶寬。[8]通過堆疊多達八個DRAM芯片裸晶(即三維集成電路)和一個可選的基本芯片(包括緩衝電路和測試邏輯)來實現。[9]堆棧通常通過基板連接到 GPU 或 CPU 上的內存控制器。另外,存儲器芯片也可以直接堆疊在CPU或GPU芯片上。[10][11]堆棧內,芯片通過硅穿孔(TSV)及微突起相連接的可選基底裸晶,附帶內存控制器。高頻寬記憶體技術原理上與美光科技開發的混合內存立方體接口類似,但不相兼容。[12][13]

高頻寬記憶體內存總線與其他DRAM內存(如DDR4或GDDR5)相比更加寬闊。在擁有四塊DRAM裸晶的高頻寬記憶體堆(4-Hi)上,每個裸晶均有兩條128比特的信道,四塊加起來總共有八條。搭載四塊4-Hi高頻寬記憶體堆的圖形卡(GPU)將擁有4096比特寬的內存總線。做個比較,GDDR內存給圖形顯示卡的信道寬度為32比特,其內存接口則為512比特。[14]高頻寬記憶體最高支持每個封裝4GB的內存。

相比較DDR4或GDDR5而言,內存的最大連接數越多,高頻寬記憶體就需要以更新的方法連接至圖形處理器(或其他處理器)。[15]AMD和英偉達均使用為特定目的打造的硅片——中介層,來連接內存及圖形處理器。中介層需要將內存與處理器放置在相鄰的位置,以減短內存路徑。但由於半導體器件製造的製造費用比印刷電路板的高出不少,客戶也需花費更多金錢購買此類產品。

高頻寬記憶體DRAM需要將宿主計算裸晶與分為多個獨立信道的分布式接口緊密結合起來。這些信道相互之間完全獨立,且不一定同步。高頻寬記憶體DRAM使用寬接口架構來執行高速、節能的計算操作。高頻寬記憶體DRAM使用500 MHz的差分時鐘 CK_t / CK_c(前綴「_t」表示「真」(True)、「正值」(Positvie)及差分對組件(Components of differential pair),「_c」則代表「互補」部分(Complementary))。指令在CK_t和CK_c的信號上升沿註冊。每個信道以雙數據速率(DDR)管理128比特的數據總線。高頻寬記憶體支持每針1 GT/s(1比特)的傳輸速率,總體封裝帶寬則能達到128 GB/s。[16]

第二代高頻寬記憶體(HBM2)指定了每堆8個裸晶及每幀傳輸速度上至2 GT/s的標準。為保持1024比特寬的訪問,第二代高頻寬記憶體得以在每個封裝中達到256GB/s的內存帶寬及上至8GB的內存。業界預測第二代HBM在極其需要性能的應用程序(如虛擬現實)中至關重要。[17]

2016年1月19日,三星集團宣布進入大量生產第二代高頻寬記憶體的早期階段,每堆擁有高達8GB的內存。[18][19]SK海力士同時宣布於2016年8月發布4GB版本的內存。[20]

2018年下半年,JEDEC宣布升級第二代HBM標準,提升帶寬及其能力。[21]官方標準中明確每堆最高307GB/s(有效數據速率則為2.4Tbit/s),但就實際而言,市面上已早有以此速度運行的產品。除此之外,標準還添加了對12-Hi堆的支持,使每堆24GB的內存成為可能。

2019年3月20日,三星發布了Flashbolt HBM2E,每個堆棧有8個芯片,傳輸速率為3.2 GT/s,每個堆棧總共提供16 GB和410 GB/s。[22]8月12日,SK海力士宣布推出HBM2E,每個堆棧有8個芯片,傳輸速率為3.6 GT/s,每個堆棧總共提供16 GB和460 GB/s,[23][24]2020年7月2日,宣布開始量產。[25]

第三代高頻寬記憶體(HBM3)於2016年正式發布,[26][27]此代標準擴大了內存容量、提升了內存帶寬(512GB/s或更高)並降低了電壓與價格。人們猜測高頻寬記憶體的密度增加是因為裸晶數量及其密度的增加導致。業界尚未宣布正式發布日期。三星專家預測在2020年前進行第三代高頻寬記憶體的量產。

為了打造能進行百億億次計算的高性能計算機,慧與科技預測OPGHC HBM3+及HBM4將在2022年至2024年間發布。更為強大的堆疊能力及更高的物理密度理論上應能讓每塊插槽的可尋址內存及運行速度更上一層樓。HBM3+的計劃速度為4 TB/s,每塊插槽的計劃可尋址內存(做個類比,AMD的高端EPYC芯片在每個插槽上可以150GB/s的速度尋址)。[28]有了32 Gbit(4 GB)的DRAM裸晶,再加上HBM3+每堆上的16片裸晶,每個HBM3+組件理論上能提供64GB的容量。

早在2008年,AMD就開始着手研發高頻寬記憶體來解決日益增長的能源使用及計算機內存的形狀因數。其中,AMD高級研究員布賴恩·布萊克(Bryan Black)解決了裸晶堆疊問題。AMD還從內存行業(SK海力士)、插入器行業(聯華電子)及封裝行業(日月光半導體)的合作夥伴中獲得了幫助,讓高頻寬記憶體從設想變成現實。[29]2015年,SK海力士在韓國利川市的工廠正式開始量產。

在2010年AMD與SK海力士共同發表提案後的2013年10月,高頻寬記憶體被JEDEC設立為業界標準(JESD235)。[6]首款使用高頻寬記憶體的裝置是AMD Radeon Fury系列顯示核心,其驅動了AMD Radeon R9 Fury X。[30][4][31]

第二代高頻寬記憶體則於2016年1月被JEDEC認可為業界標準(JESD235a)。[7]首款使用第二代高頻寬記憶體技術的圖形處理器是於2016年4月發布的英偉達 Tesla P100。[32][33]

在2016年8月的熱門芯片上,三星與海力士均宣布了下一代高頻寬記憶體技術。[34][35]兩家公司都預計下一代產品的裸晶密度、帶寬得到提升,同時減少能源消耗。三星還宣布將發布低成本版本的高頻寬記憶體,此類產品將移除緩存裸晶、減少硅穿孔,並將總帶寬降至200GB/s。

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.