热门问题

时间线

聊天

视角

積體電路設計

電子硬體工程流程 来自维基百科,自由的百科全书

Remove ads

集成電路設計(英語:Integrated circuit design,簡稱IC design),多直稱IC設計,根據當前集成電路的集成規模,亦可稱之為超大規模集成電路設計(VLSI design)[1],是指以集成電路、超大規模集成電路為目標的設計流程。

概述

集成電路設計涉及對電子器件(例如晶體管、電阻器、電容器等)、器件間互連線模型的建立。所有的器件和互連線都需安置在一塊半導體襯底材料之上,這些元件通過半導體器件製造工藝(例如光刻等)安置在單一的硅襯底上,從而形成電路。[2]:7-10目前最常使用的襯底材料是硅。設計人員會使用技術手段將硅襯底上各個器件之間相互電隔離,以控制整個芯片上各個器件之間的導電性能。PN結、金屬氧化物半導體場效電晶體等組成了集成電路器件的基礎結構,而由後者構成的互補式金屬氧化物半導體則憑藉其低靜態功耗、高集成度的優點成為數字集成電路中邏輯門的基礎構造。[2]:197-198設計人員需要考慮晶體管、互連線的能量耗散,這一點與以往由分立電子器件開始構建電路不同,這是因為集成電路的所有器件都集成在一塊硅片上。金屬互連線的電遷移以及靜電放電對於微芯片上的器件通常有害,因此也是集成電路設計需要關注的課題。

隨着集成電路的規模不斷增大,其集成度已經達到深亞微米級(特徵尺寸在130納米以下),單個芯片集成的晶體管已經接近十億個。[3]:48-49由於其極為複雜,集成電路設計相較簡單電路設計常常需要計算機輔助的設計方法學和技術手段。集成電路設計的研究範圍涵蓋了數字集成電路中數字邏輯的優化、網表實現,寄存器傳輸級硬件描述語言代碼的書寫,邏輯功能的驗證、仿真和時序分析,電路在硬件中連線的分布,模擬集成電路中運算放大器、電子濾波器等器件在芯片中的安置和混合信號的處理。相關的研究還包括硬件設計的電子設計自動化(EDA)、計算機輔助設計(CAD)方法學等,是電機工程學和計算機工程的一個子集。

對於數字集成電路來說,設計人員現在更多的是站在高級抽象層面,即寄存器傳輸級甚至更高的系統級(有人也稱之為行為級),使用硬件描述語言或高級建模語言來描述電路的邏輯、時序功能,而邏輯綜合可以自動將寄存器傳輸級的硬件描述語言轉換為邏輯門級的網表。對於簡單的電路,設計人員也可以用硬件描述語言直接描述邏輯門和觸發器之間的連接情況。網表經過進一步的功能驗證、後端設計、布局、布線,可以產生用於工業製造的GDSII文件,工廠根據該文件就可以在晶圓上製造電路。[4]:388-389模擬集成電路設計涉及了更加複雜的信號環境,對工程師的經驗有更高的要求,並且其設計的自動化程度遠不及數字集成電路。[5]:3

逐步完成功能設計之後,設計規則會指明哪些設計符合製造要求,而哪些設計不符合,而這個規則本身也十分複雜。集成電路設計流程需要符合數百條這樣的規則。在一定的設計約束下,集成電路物理版圖的布局、布線對於獲得理想速度、信號完整性、減少芯片面積、減少芯片能耗來說至關重要。半導體器件製造的不可預測性使得集成電路設計的難度進一步提高。在集成電路設計領域,由於市場競爭的壓力,電子設計自動化等相關計算機輔助設計工具得到了廣泛的應用,工程師可以在計算機軟件的輔助下進行寄存器傳輸級設計、功能驗證、靜態時序分析、物理設計等流程。[6]:2-3

Remove ads

抽象級別

集成電路設計通常是以「模塊」作為設計的單位的。例如,對於多位全加器來說,其次級模塊是一位的加法器,而加法器又是由下一級的與門、非門模塊構成,與、非門最終可以分解為更低抽象級的CMOS器件。

從抽象級別來說,數字集成電路設計可以是自頂向下的,即先定義了系統最高邏輯層次的功能模塊,根據頂層模塊的需求來定義子模塊,然後逐層繼續分解;設計也可以是自底向上的,即先分別設計最具體的各個模塊,然後如同搭積木一般用這些最底層模塊來實現上層模塊,最終達到最高層次。[7]:257在許多設計中,自頂向下、自底向上的設計方法學是混合使用的,系統級設計人員對整體體系結構進行規劃,並進行子模塊的劃分,而底層的電路設計人員逐層向上設計、優化單獨的模塊。最後,兩個方向的設計人員在中間某一抽象層次會合,完成整個設計。[8]:9

硬件實現

對於不同的設計要求,工程師可以選擇使用半定製設計途徑,例如採用可編程邏輯器件(現場可編程邏輯門陣列等)或基於標準單元庫的特殊應用積體電路來實現硬件電路;也可以使用全定製設計,控制晶體管版圖到系統結構的全部細節。[9]:2-6

這種設計方式要求設計人員利用版圖編輯器來完成版圖設計、參數提取、單元表徵,然後利用這些自己設計的單元來完成電路的構建。通常,全定製設計是為了最大化優化電路性能。如果標準單元庫中缺少某種所需的單元,也需要採取全定製設計的方法完成所需的單元設計。不過,這種設計方式通常需要較長的時間。[10]:3

與全定製設計相對的設計方式為半定製設計。簡而言之,半定製集成電路設計是基於預先設計好的某些邏輯單元。例如,設計人員可以在標準元件庫(通常可以從第三方購買)的基礎上設計專用集成電路,從中選取所需的邏輯單元(例如各種基本邏輯門、觸發器等)來搭建所需的電路。[10]:4他們也可以使用可編程邏輯器件來完成設計,這類器件的幾乎所有物理結構都已經固定在芯片之中,僅剩下某些連線可以由用戶編程決定其連接方式。[10]:9與這些預先設計好的邏輯單元有關的性能參數通常也由其供應商提供,以方便設計人員進行時序、功耗分析。

可編程邏輯器件通常由半導體廠家提供商品芯片,這些芯片可以通過JTAG等方式和計算機連接,因此設計人員可以用電子設計自動化工具來完成設計,然後將利用設計代碼來對邏輯芯片編程。可編程邏輯陣列芯片在出廠前就提前定義了邏輯門構成的陣列,而邏輯門之間的連接線路則可以通過編程來控制連接與斷開。[11]:197隨着技術的發展,對連接線的編程可以通過EPROM(利用較高壓電編程、紫外線照射擦除)、EEPROM(利用電信號來多次編程和擦除)、SRAM、閃存等方式實現。現場可編程邏輯門陣列是一種特殊的可編程邏輯器件,它的物理基礎是可配置邏輯單元,由查找表、可編程多路選擇器、寄存器等結構組成。查找表可以用來實現邏輯函數,如三個輸入端的查找表可以實現所有三變量的邏輯函數。[11]:199

Remove ads

專用集成電路(ASIC)只能在整個集成電路設計完成之後才能開始製造,而且需要專業的半導體工廠的參與。專用集成電路可以是基於標準單元庫,也可以是全定製設計。在後一種途徑中,設計人員對於晶圓上元件的位置和連接有更多的控制權,而不像可編程邏輯器件途徑,只能選擇使用其中部分硬件資源,從而造成部分資源被浪費。專用集成電路的面積、功耗、時序特性通常可以得到更好的優化。然而,專用集成電路的設計會更加複雜,並且需要專門的工藝製造部門(或者外包給晶圓代工廠)才能將GDSII文件製造成電路。一旦專用集成電路芯片製造完成,就不能像可編程邏輯器件那樣對電路的邏輯功能進行重新配置。對於單個產品,在專用集成電路上實現集成電路的經濟、時間成本都比可編程邏輯器件高,因此在早期的設計與調試過程中,常用可編程邏輯器件,尤其是現場可編程邏輯門陣列;如果所設計的集成電路將要在後期大量投產,那麼批量生產專用集成電路將會更經濟。[9]:103-106

Remove ads

設計流程

集成電路設計可以大致分為數字集成電路設計和模擬集成電路設計兩大類。不過,實際的集成電路還有可能是混合訊號積體電路,因此不少電路的設計同時用到這兩種流程。

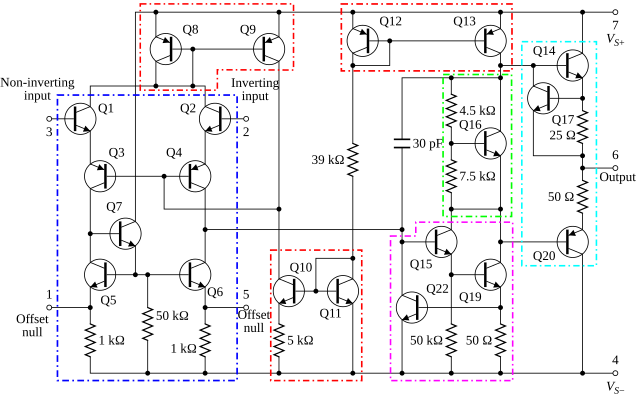

集成電路設計的另一個大分支是模擬集成電路設計,這一分支通常關注電源集成電路、射頻集成電路等。[3]:7由於現實世界的信號是模擬的,所以,在電子產品中,類比-數位、數位-類比相互轉換的集成電路也有着廣泛的應用。模擬集成電路包括運算放大器、線性整流器、鎖相環、振盪電路、有源濾波器等。相較數字集成電路設計,模擬集成電路設計與半導體器件的物理性質有着更大的關聯,例如其增益、電路匹配、功率耗散以及阻抗等等。模擬信號的放大和濾波要求電路對信號具備一定的保真度,因此模擬集成電路比數字集成電路使用了更多的大面積器件,集成度亦相對較低。

在微處理器和計算機輔助設計方法出現前,模擬集成電路完全採用人工設計的方法。由於人處理複雜問題的能力有限,因此當時的模擬集成電路通常是較為基本的電路,運算放大器集成電路就是一個典型的例子。在當時的情況下,這樣的集成電路可能會涉及十幾個晶體管以及它們之間的互連線。為了使模擬集成電路的設計能達到工業生產的級別,工程師需要採取多次迭代的方法以測試、排除故障。重複利用已經設計、驗證的設計,可以進一步構成更加複雜的集成電路。1970年代之後,計算機的價格逐漸下降,越來越多的工程師可以利用這種現代的工具來輔助設計,例如,他們使用編好的計算機程序進行仿真,便可獲得比之前人工計算、設計更高的精確度。SPICE是第一款針對模擬集成電路仿真的軟件(事實上,數字集成電路中標準單元本身的設計,也需要用到SPICE來進行參數測試),其字面意思是「以集成電路為重點的仿真程序(英語:Simulation Program with Integrated Circuit Emphasis)」 。[12]基於計算機輔助設計的電路仿真工具能夠適應更加複雜的現代集成電路,特別是專用集成電路。使用計算機進行仿真,還可以使項目設計中的一些錯誤在硬件製造之前就被發現,從而減少因為反覆測試、排除故障造成的大量成本。此外,計算機往往能夠完成一些極端複雜、繁瑣,人類無法勝任的任務,使得諸如蒙地卡羅方法等成為可能。實際硬件電路會遇到的與理想情況不一致的偏差,例如溫度偏差、器件中半導體摻雜濃度偏差,計算機仿真工具同樣可以進行模擬和處理。總之,計算機化的電路設計、仿真能夠使電路設計性能更佳,而且其可製造性可以得到更大的保障。儘管如此,相對數字集成電路,模擬集成電路的設計對工程師的經驗、權衡矛盾等方面的能力要求更嚴格。

粗略地說,數字集成電路可以分為以下基本步驟:系統定義、寄存器傳輸級設計、物理設計。而根據邏輯的抽象級別,設計又分為系統行為級、寄存器傳輸級、邏輯門級。[1]:29-32[13]:13設計人員需要合理地書寫功能代碼、設置綜合工具、驗證邏輯時序性能、規劃物理設計策略等等。在設計過程中的特定時間點,還需要多次進行邏輯功能、時序約束、設計規則方面的檢查、調試,以確保設計的最終成果合乎最初的設計收斂目標。[14]:3-4

系統定義是進行集成電路設計的最初規劃,在此階段設計人員需要考慮系統的宏觀功能。設計人員可能會使用一些高抽象級建模語言和工具來完成硬件的描述,例如C語言、C++、SystemC、SystemVerilog等事務級建模語言,以及Simulink和MATLAB等工具對信號進行建模。儘管目前的主流是以寄存器傳輸級設計為中心,但已有一些直接從系統級描述向低抽象級描述(如邏輯門級結構描述)轉化的高級綜合(或稱行為級綜合)、高級驗證工具正處於發展階段。[15]

系統定義階段,設計人員還對芯片預期的工藝、功耗、時脈頻率、工作溫度等性能指標進行規劃。

目前的集成電路設計常常在寄存器傳輸級上進行,利用硬件描述語言來描述數字集成電路的信號儲存以及信號在寄存器、存儲器、組合邏輯裝置和總線等邏輯單元之間傳輸的情況。在設計寄存器傳輸級代碼時,設計人員會將系統定義轉換為寄存器傳輸級的描述。設計人員在這一抽象層次最常使用的兩種硬件描述語言是Verilog、VHDL,二者分別於1995年和1987年由電氣電子工程師學會(IEEE)標準化。[11]:110正由於有着硬件描述語言,設計人員可以把更多的精力放在功能的實現上,這比以往直接設計邏輯門級連線的方法學(使用硬件描述語言仍然可以直接設計門級網表,但是少有人如此工作)具有更高的效率。

設計人員完成寄存器傳輸級設計之後,會利用測試平台、斷言等方式來進行功能驗證,檢驗項目設計是否與之前的功能定義相符,如果有誤,則需要檢測之前設計文件中存在的漏洞。[16]現代超大規模集成電路的整個設計過程中,驗證所需的時間和精力越來越多,甚至都超過了寄存器傳輸級設計本身,人們設置些專門針對驗證開發了新的工具和語言。

例如,要實現簡單的加法器或者更加複雜的算術邏輯單元,或利用觸發器實現有限狀態機,設計人員可能會編寫不同規模的硬件描述語言代碼。功能驗證是項複雜的任務,驗證人員需要為待測設計建立一個虛擬的外部環境,為待測設計提供輸入信號(這種人為添加的信號常用「激勵」這個術語來表示),然後觀察待測設計輸出端口的功能是否合乎設計規範。

當所設計的電路並非簡單的幾個輸入端口、輸出端口時,由於驗證需要儘可能地考慮到所有的輸入情況,因此對於激勵信號的定義會變得更加複雜。有時工程師會使用某些腳本語言(如Perl、Tcl)來編寫驗證程序,藉助計算機程序的高速處理來實現更大的測試覆蓋率。現代的硬件驗證語言可以提供一些專門針對驗證的特性,例如帶有約束的隨機化變量、覆蓋等等。作為硬件設計、驗證統一語言,SystemVerilog是以Verilog為基礎發展而來的,因此它同時具備了設計的特性和測試平台的特性,並引入了面向對象程序設計的思想,因此測試平台的編寫更加接近軟件測試。[17]諸如通用驗證方法學的標準化驗證平台開發框架也得到了主流電子設計自動化軟件廠商的支持。針對高級綜合,關於高級驗證的電子設計自動化工具也處於研究中。

工程師設計的硬件描述語言代碼一般是寄存器傳輸級的,在進行物理設計之前,需要使用邏輯綜合工具將寄存器傳輸級代碼轉換到針對特定工藝的邏輯門級網表,並完成邏輯化簡。

和人工進行邏輯優化需要藉助卡諾圖等類似,電子設計自動化工具來完成邏輯綜合也需要特定的算法(如奎因-麥克拉斯基算法等)來化簡設計人員定義的邏輯函數。輸入到自動綜合工具中的文件包括寄存器傳輸級硬件描述語言代碼、工藝庫(可以由第三方晶圓代工服務機構提供)、設計約束文件三大類,這些文件在不同的電子設計自動化工具套件系統中的格式可能不盡相同。邏輯綜合工具會產生一個優化後的門級網表,但是這個網表仍然是基於硬件描述語言的,這個網表在半導體芯片中的走線將在物理設計中來完成。[8]:201-204

選擇不同器件(如專用集成電路或者現場可編程門陣列等)對應的工藝庫來進行邏輯綜合,或者在綜合時設置了不同的約束策略,將產生不同的綜合結果。寄存器傳輸級代碼對於設計項目的邏計劃分、語言結構風格等因素會影響綜合後網表的效率。

目前大多數成熟的綜合工具大多數是基於寄存器傳輸級描述的,而基於系統級描述的高級綜合工具還處在發展階段。

為了比較門級網表和寄存器傳輸級的等效性,可以通過生成諸如不二可滿足性、二元決策圖等途徑來完成形式等效性檢查(形式驗證)。實際上,等效性檢查還可以檢查兩個寄存器傳輸級設計之間,或者兩個門級網表之間的邏輯等效性。

現代集成電路的時鐘頻率已經到達了兆赫茲級別,而大量模塊內、模塊之間的時序關係極其複雜,[13]:7-8因此,除了需要驗證電路的邏輯功能,還需要進行時序分析,即對信號在傳輸路徑上的延遲進行檢查,判斷其是否符合時序收斂要求。[14]:7時序分析所需的邏輯門標準延遲格式信息可以由標準單元庫(或從用戶自己設計的單元從提取的時序信息)提供。隨着電路特徵尺寸不斷減小,互連線延遲在實際的總延時中所占的比例愈加顯著,因此在物理設計完成之後,把互連線的延遲納入考慮,才能夠精準地進行時序分析。

邏輯綜合完成之後,通過引入器件製造公司提供的工藝信息,前面完成的設計將進入布圖規劃、布局、布線階段,工程人員需要根據延遲、功耗、面積等方面的約束信息,合理設置物理設計工具的參數,不斷調試,以獲取最佳的配置,從而決定元件在晶圓上的物理位置。如果是全定製設計,工程師還需要精心繪製單元的集成電路版圖,調整晶體管尺寸,從而降低功耗、延時。[14]:8-9

隨着現代集成電路的特徵尺寸不斷下降,超大規模集成電路已經進入深亞微米級階段,互連線延遲對電路性能的影響已經達到甚至超過邏輯門延遲的影響。這時,需要考慮的因素包括線網的電容效應和線網電感效應,芯片內部電源線上大電流在線網電阻上造成的電壓降也會影響集成電路的穩定性。[13]:6-7為了解決這些問題,同時緩解時鐘偏移、時鐘樹寄生參數的負面影響,合理的布局布線和邏輯設計、功能驗證等過程同等重要。[3]:49隨着移動設備的發展,低功耗設計在集成電路設計中的地位愈加顯著。在物理設計階段,設計可以轉化成幾何圖形的表示方法,工業界有若干標準化的文件格式(如GDSII)予以規範。

值得注意的是,電路實現的功能在之前的寄存器傳輸級設計中就已經確定。在物理設計階段,工程師不僅不能夠讓之前設計好的邏輯、時序功能在該階段的設計中被損壞,還要進一步優化芯片按照正確運行時的延遲時間、功耗、面積等方面的性能。在物理設計產生了初步版圖文件之後,工程師需要再次對集成電路進行功能、時序、設計規則、信號完整性等方面的驗證,以確保物理設計產生正確的硬件版圖文件。[14]

半導體製造工廠根據物理設計最後完成、已經通過各項檢查後生成的標準化GDSII文件,即可製造出實際的物理電路。

這個步驟不再屬於集成電路設計和計算機工程的範疇,而是直接進入半導體製造工藝領域,關注的重心亦轉向具體的材料、器件製作,例如光刻、刻蝕、物理氣相沉積、化學氣相沉積等。

傳統的集成電路公司能夠同時完成集成電路設計和集成電路製造。由於集成電路製造所需的設備、原料耗資巨大,因此一般的公司根本無力承受。一旦發生工藝節點的改變(如從65納米工藝進步到45納米工藝),公司可能需要花費相當高的成本來更換現有工藝設備,這給許多公司帶來了相當沉重的經濟負擔)。現在,有些公司逐漸放棄既設計、又製造的模式,業務範圍縮小至設計、驗證本身,而將具體的半導體工藝流程,委託給專門進行集成電路製造的工廠。上述無製造工藝(fabless),只進行設計、驗證公司被稱為無廠半導體公司,典型的例子包括高通(Qualcomm)、超微半導體(AMD)、英偉達(NVIDIA)等;而專門負責製造的公司則被稱為晶圓代工廠,典型的例子包括台積電(TSMC)、格羅方德(GlobalFoundries,前身為AMD的直屬工藝廠)等。某些公司在從事設計的同時,還保留了自己的工藝廠,這樣的公司包括英特爾、三星電子等。還有一類特殊的無廠半導體公司,它們把設計項目以IP核的形式封裝起來,作為商品銷售給其他無廠半導體公司,典型的例子包括ARM公司。

可測試性設計

隨着超大規模集成電路的複雜程度不斷提高,電路製造後的測試所需的時間和經濟成本也不斷增加。以往,人們將絕大多數精力放在設計本身,而並不考慮之後的測試,因為那時的測試相對今天更為簡單。近年來,測試本身也逐漸成為一個龐大的課題。

比如,從電路外部控制某些內部信號使得它們呈現特定的邏輯值比較容易,而某些內部信號由於依賴大量其它內部信號,從外部很難直接改變它們的數值。此外,內部信號的改變很多時候不能在主輸出端觀測(有時主輸出端的信號輸出看似正確,其實內部狀態是錯誤的,僅觀測主輸出端的輸出不足以判斷電路是否正常工作)。以上兩類問題,即可控制性和可觀測性,是可測試性的兩大組成部分。

人們逐漸發現,電路在設計時向電路添加一些特殊的結構(例如掃描鏈和內建自測試),能夠大大方便之後的電路測試。這樣的設計被即為可測試性設計,它們使電路更加複雜,但是卻能憑藉更簡捷的測試降低整個項目的成本。[18]

重用

隨着超大規模集成電路的集成難度不斷提高,同時市場競爭壓力不斷增加,集成電路設計逐漸引入了可重用設計方法學[19]。

可重用設計方法學的主要意義在於提供IP核(知識產權核)的供應商可以將一些已預先完成之設計以商品的形式提供給設計方,後者可以將IP核作為一個完整的模塊在自己的設計項目中使用。由此,在實現類似功能時,各個公司就不需反覆設計類似模塊。這樣做雖會提高商業成本,但亦顯著降低了設計的複雜程度,從而縮短設計大型電路所需的時間周期並提高市場競爭力。

IP核供應商提供的產品可能是已驗證的硬件描述語言代碼,為了保護供應商的知識產權,這些代碼大多是加密的。IP核本身也是作為集成電路進行設計,但是它為了在不同設計項目中能夠得到應用,會重點強化其可移植性,因此它的設計代碼規範更加嚴格。有的芯片公司專門從事IP核的開發和銷售,ARM就是一個典型的例子,這些公司通過知識產權的授權營利[19]。

輔助和自動化

由於集成電路系統的複雜性,工程師往往需要藉助電子設計自動化工具來進行計算機輔助設計。邏輯綜合就是電子設計自動化在數字集成電路設計中最顯著的體現。以往在設計小規模、中規模集成電路時,工程師設計數字集成電路需要根據邏輯功能,通過類似卡諾圖這樣的手工途徑來優化邏輯函數,然後確定使用何種邏輯門來實現電路。而在當前超大規模集成電路,乃至更大的甚大規模集成電路的設計中,這樣的工作方式不太現實。電子設計自動化工具使得工程師能夠從複雜的邏輯閘設計轉到功能設計,而底層的轉換由自動工具完成,工程師只需要掌握如何設置這些工具工作策略的知識。硬件描述語言是集成電路設計自動化的重要基礎。[8]:2-3電子設計自動化發展十分迅速,現在已經成立了諸如設計自動化會議的一些學術論壇,定期討論業界的發展。[20]

完成整個集成電路設計常常涉及多個電子設計自動化工具的運用。[21]有些公司專門從事集成電路計算機輔助設計工具套件的開發和銷售,例如Synopsys、Cadence、Mentor Graphics、Agilent、Altium、Xilinx等。電子設計自動化工具的本身作為一種軟件,背後依靠的是各種計算機算法。因此電子設計自動化工具的開發更加接近軟件設計的範疇,其開發人員需要重點關注邏輯簡化、布局布線等方面的算法實現,但是他們同樣需要了解集成電路的硬件知識。[5]:3-30

參考文獻

參見

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads