トップQs

タイムライン

チャット

視点

MOSFET

ウィキペディアから

Remove ads

MOSFET(金属酸化膜半導体電界効果トランジスタ・英: metal-oxide-semiconductor field-effect transistor)は、電界効果トランジスタ (FET) の一種で、LSIの中では最も一般的に使用されている構造である。材質としては、シリコンを使用するものが一般である。「モス・エフイーティー」や「モスフェット」と呼ばれたり、「MOS-FET」と記述されることもあり、IGFET[注釈 1]やMISFET[注釈 2]がMOSFETとほぼ同義で用いられることがある。ユリウス・エドガー・リリエンフェルトが考案した。

集積回路で使われる微細MOSFETと、高電圧・高電流の用途で使われるパワーMOSFETがあり、素子構造も大きく異なる。基本的にはパワーMOSFETは個別半導体(ディスクリート半導体)であり、高い耐圧を実現するために縦方向の電荷の流れを用いているが、微細MOSFETでは基板表面に電荷の流れを作っている。 [1]

Remove ads

構造と特徴

MOSFETは、通常p型のシリコン基板上に作成される。n型MOS(NMOS) の場合、p型のシリコン基板上のゲート領域にシリコンの酸化膜とその上にゲート金属を形成し、ドレイン・ソース領域には高濃度の不純物をイオン注入し、n型(n+型)の半導体にする。

p型MOS(pMOS)の場合は、p型のシリコン基板にイオン注入でn層の領域を作成し、n型の注入領域中のゲート領域にシリコンの酸化膜とその上にゲート金属を形成し、ドレイン・ソース領域には高濃度の不純物を再度イオン注入し、p型(p+型)の半導体にする。

過去においては、空乏層による疑似交流キャパシターのみを持つバイポーラトランジスタや他の構造FETと比べると、ゲートの下に絶縁層を持つ関係上キャパシターを構造的に抱えているために、原理的には動作速度が遅くなる点や、トランスコンダクタンス(gm)が低い点などがMOSFETの課題であった。しかしながら、ゲート電流がほとんど流れない事やプロセス工程が比較的単純であるため、一部の高周波用素子を除き、多くのデジタル集積回路やアナログ回路にMOSFETが使用されている。更に、ドレイン-ソース間抵抗を低くできるため、特に電力スイッチング用途ではバイポーラトランジスタを代替した。近年では、ゲート長を小さくし、ゲート絶縁体の厚さを薄くすることや、SOI技術の使用により、動作速度やgmの問題を概ね解消している。シリコン製で数GHzの動作が可能になるとシリコンMOSによる製品領域が拡大し、従来は高速動作用として一般的だったヒ化ガリウム製FETの存在を脅かしている。

シリコンによるMOSFET製の集積回路では、ゲートはポリシリコン(多結晶珪素)で形成することが長い間一般的であったが、ポリシリコンより抵抗値が低い金属を使用したり、リーク電流を減らすためにゲート絶縁体の厚さを厚くできる高誘電率のゲート絶縁膜を用いれば、高速動作が可能で低消費電力なICが作れるため、米インテル社は高誘電率 (High-κ) 絶縁膜とメタルゲートを組み合わせた新たなプロセス技術を開発し、2007年秋の45nmのプロセスルールによる製品の製造に採用するようになった[2]。その後、高性能なデジタル半導体を製造する各社も同技術を開発し製造している。

これら、MOSと類似の構造についてはシリコン-酸化膜-シリコンであったり、金属-絶縁膜-シリコンであるが、同様の原理を使っているため、一般にはMOS半導体素子として扱われている。

図のように集積回路内部では4端子素子として扱う。一方でディスクリート部品の場合、MOSFETは、ボディ(サブストレート)とソースが内部で接続されているので、3端子デバイスとして扱われる[3]。

Remove ads

動作

要約

視点

理論的にn型とp型の違いはドレイン-ソース間の電流に寄与するキャリアの違いだけなので、ここではn型についてのみ扱う。

MOSFETではゲートと基材の間に構成されたキャパシターにより、ゲートに正電圧が印加された場合、p型のサブストレートと絶縁層の境界面に電子を引き寄せドレイン-ソース間に反転層(n型)を作り上げる事でソース-ドレイン間を高コンダクタンスにする。ドレイン-ソース間電圧(Vds)が比較的低く、ゲート-ソース間の電圧(Vgs)からしきい値電圧(Vth)を引いた値(Vgs-Vth)がそれを超えている領域を線形領域と呼ぶ(図2)。線形領域においてはゲート電圧に比例して反転層が厚みを増すため、コンダクタンスがゲート電圧に比例して上がる。

一方、ドレイン-ソース間電圧(Vds)がゲート-ソース間の電圧(Vgs)からしきい値電圧(Vth)を引いた値(Vgs-Vth)を上回るとドレイン領域近辺には反転層が形成されなくなる。この状態をピンチオフしたと言う。 この状態(ピンチオフ)よりドレイン電圧が高い領域を飽和領域と呼び、MOSのコンダクタンスは反転層の長さによって一定に決まる(図3)。この状態では定電流源として扱われる。

ここで注意したいのは、MOSFETのしきい値電圧は、基本的にはゲート-ソース間の条件で決まるのであり、ピンチオフと言うのは単にドレイン側で反転層が形成される条件が満たされなくなったと言う事である。従って、ピンチオフしてドレイン側でチャネルが消失しても、電子の流れが止まるというものではない。ゲート-ソース間にしきい値電圧以上の電圧が印加されていればソース端では反転層が形成され、電子はソースから流入する。ピンチオフ点以降のドレイン側でチャネルが消失してもドレイン側に大きな電界は存在するので流入した電子はドレイン電極に向かって加速される。また、ピンチオフ以降でドレイン電圧がさらに高くなっても、それはドレイン側の空乏層が拡大するだけで、ソース側の電子の流入には(基本的には)関係しないので定電流源として動作すると考えてよい。 [注釈 3]

ここで言う「飽和領域」とはピンチオフした後、ドレイン電圧を上げてもドレイン電流が増加しない状態、つまり電流値が飽和している状態であって、電子速度が飽和するいわゆる電子の速度飽和現象とは異なるものである。

微細加工が進みチャネル長が短くなると、ドレイン電圧を高くするにつれてピンチオフ条件が成立する場所がドレイン端からソース方向に移動することにより、実効的なチャネル長が短くなり、ドレイン電流が増加する効果が現れる。これをチャネル長変調効果と呼び、バイポーラ・トランジスタのアーリー効果[4]に相当する。チャネル長変調効果を低減するには、なるべくチャネル長を大きく設計することが必要となる。

Remove ads

寄生ダイオード

ボディ(サブストレート)とドレインの間、あるいはボディとソースの間に寄生ダイオード(ボディーダイオード)が存在する[5]。 例えば、n型MOSFETの場合、ボディがp型半導体であり、ソースとドレインがn型半導体なので、pn接合を形成してしまう。これが寄生ダイオードとなる。 MOSFETの記号の矢印は、この寄生ダイオードの順方向バイアスを示している。通常、この寄生ダイオードに電流を流してはいけないので、ドレイン-ソース間に流れる電流の方向は記号の矢印と逆方向にしないといけない。

寄生ダイオードには利点もある。パワーMOSFETの場合、寄生ダイオードの特性が良ければ、電力インバーター回路などで必要なフリーホイールダイオード(環流ダイオード)として用いることもできるからである[5]。

バイポーラ・トランジスタとの比較

バイポーラ・トランジスタはスイッチや増幅といった働きを入力電流で制御しているのに対して、MOSFETは入力電圧による電界で制御している。動作のためにベース電流が流れるバイポーラ・トランジスタと違い、MOSFETのゲートには原理的に、直流的には[注釈 4]わずかなリーク電流以外は流れないため一般に低消費電力である。また、バイポーラ・トランジスタは正孔と電子という2種類のキャリアによる動作なのに対して、MOSFETでは1種類のキャリアによる動作であり、「ユニポーラ・トランジスタ」とも呼ばれる。IC化の際、バイポーラ・トランジスタはPNP、NPNという二つのPN接合を縦方向に作りこまなければならないのに対して、MOSFETでは並んだ両極間の上面に絶縁層とゲート電極を設ける構造なので平面的であり、高集積化するのに適する。バイポーラ・トランジスタでは入出力が「エミッタ」「ベース」「コレクタ」であるのに対して、MOSFETでは「ソース」「ゲート」「ドレイン」である[6]。

バイポーラ・トランジスタの動作と比較を考えるのはMOSFETの動作を理解するうえで有意義である。どちらもPN接合の基本的原理に基づいているからである。バイポーラ・トランジスタでは、ベース-エミッタ間のPN接合にベース電流を流すことで、ベース領域とエミッタ領域の不純物濃度比に比例するエミッタ電流を引き出すことにより増幅作用を得ているが、MOSFETではソース領域と、それに接するチャネル領域とで形成するPN接合のチャネル領域にゲート絶縁膜を介して電界を与えることにより、ソース領域からチャネル領域へのポテンシャル障壁を下げ、ソース領域からチャネル領域への電子の流入を実現している。

バイポーラ・トランジスタではエミッタから流入した電子は、薄いベース層を通過してコレクタで集められる(コレクトされる)が、MOSFETではソース領域から流入した電子はドレイン側からの電界によってチャネルを通過してドレイン(排水口)領域に流れ込むと言うイメージは同じである。しかし、バイポーラ・トランジスタではすべての電流はPN接合によるものなので電子とホールの両方が伝導に寄与しているが、MOSFETではチャネルを通過するのはNチャネル型では電子のみ、Pチャネル型ではホールのみである。それがMOSFETがユニポーラ型とも呼ばれるゆえんである。

Remove ads

電気的特性を示す諸特性(大信号)

要約

視点

ドレイン-ソース電圧(以下Vds)、ゲート-ソース電圧(以下Vgs)としきい値(以下Vt)の関係から、MOSの動作領域は4つに大別される。

カットオフ: :

線形領域:

飽和領域:

ブレイクダウン:

:ブレークダウン電圧

それぞれにおいて、ドレイン電流(以下Id)は下記のように理論式(実験式ではない)が求められている。

カットオフ:

線形領域:

飽和領域:

ブレークダウン:

:主要原因の現象により異なるが、一般に素子破壊に至るまで電流が増加すると扱われている。

:n型MOSの場合

:p型MOSの場合

:単位面積あたりのゲート酸化膜容量

:正孔移動度

:チャネル長変調係数

Remove ads

電気的特性を示す諸特性(小信号)

要約

視点

小信号特性は等価回路上に規定された各パラメータが下記のように理論式が求められている。

:相互コンダクタンス、伝達コンダクタンス、トランスコンダクタンス

: オーバーラップキャパシタンス

: 接合容量

は固有容量[注釈 5]を表し、その値は動作領域により下記のように変化する。

カットオフ:

線形領域:

飽和領域:

Remove ads

チャネルの極性による分類

MOSFETの場合、基本的にソース・ドレイン端子に金属(アルミなどの配線層)を接合する。その際に接触抵抗を下げる目的で、比較的高濃度の不純物を打ち込む。 打ち込む不純物が n 型(p 型シリコン基板に対しては、III価の物質(B:ホウ素など))の場合、その部分は n+ 型(n ウェル)、 不純物が p 型(n 型シリコン基板に対しては、V価の物質(P:リンなど))の場合は p+ 型(p ウェル)と呼ばれる。

接触抵抗が十分に低い場合は不純物を打ち込む必要がなく、結果 p、n どちらにも属さない。 これはアンバイポーラ・トランジスタと呼ばれる。 この素子は、ゲートにマイナスの電圧(対ソース)を加えてもプラスの電圧を加えても、しきい値以上であれば電流を流す。

1980年代中頃までのメモリICやロジックICには、当時の集積技術の問題から p、n 両方を堆積する事が難しかったために、抵抗などでCMOSの片側を代用したp-MOS・n-MOSが用いられた。出現当初は製造しやすかったp-MOSが主力だったが、後に移動度の大きい電子をキャリアとするn-MOSが主力となった。

1980年代初めに標準ロジックICがCMOS構造で作られた。1990年代には電気的特性がアナログでの実用レベルに到達したのと、システムLSI等で論理回路とアナログ回路が混在して集積されるようになった関係でアナログ回路もCMOSで製作されるようになった。

Remove ads

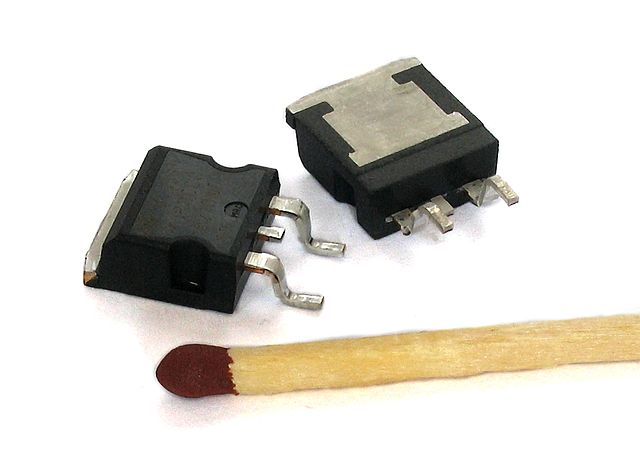

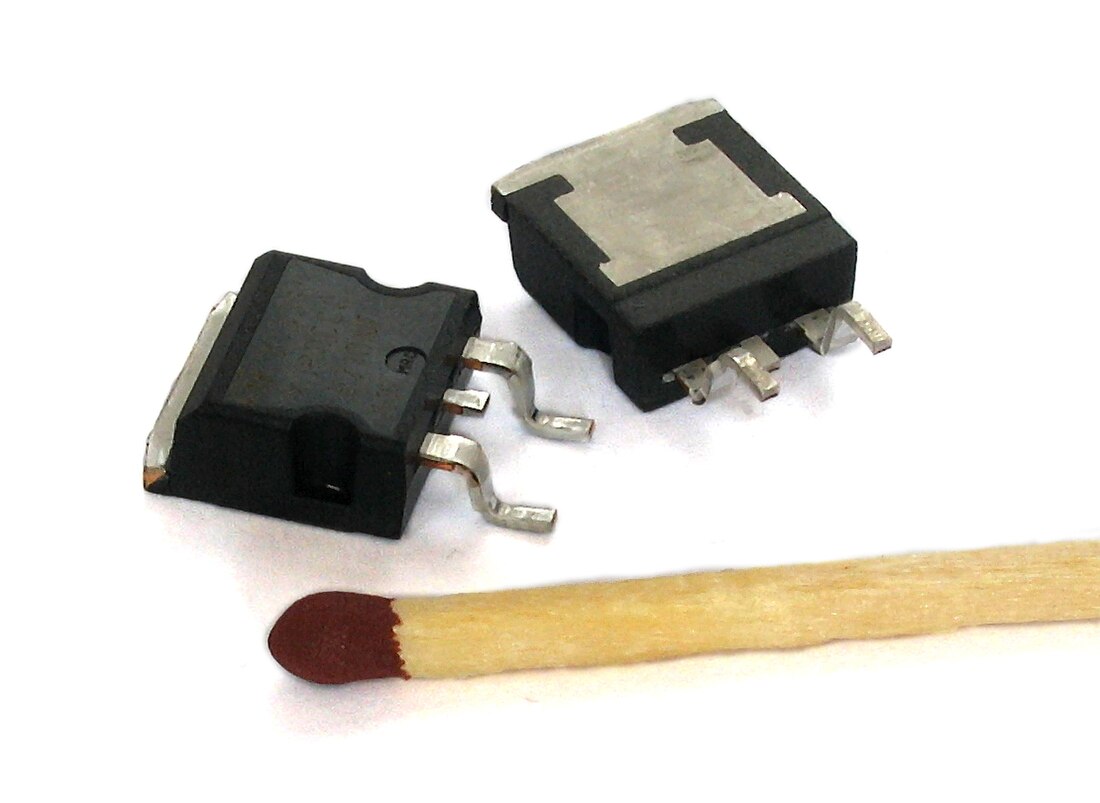

パワーMOSFET

→「パワーMOSFET」も参照

MOSFET のうち特に大電力のスイッチング用に設計されたものである。バイポーラパワー・トランジスタに比べて、電圧駆動形素子であるので駆動回路の電力ロスが小さい。また、多数キャリアデバイスであり、本質的に高速スイッチングが可能で、スイッチングロスが小さい。しかし、耐圧が高くなるにしたがってオン抵抗が高くなるという問題がある。

2000年代に入り、トレンチゲート・擬平面接合などの構造の工夫により、高耐電圧化、オン抵抗・スイッチング損失の低減をともに満足するものも開発された。さらに、2006年現在、超接合構造を用い、シリコンの理論的限界を超える低損失のものも開発されている。

型番

日本におけるFETの型番は

- 2SJxxx PチャネルFET

- 2SKxxx NチャネルFET

というように番号が付けられているものが多い。ただし、JFETとMOSFETの区別は無い。混合(周波数変換)、利得調整などの目的で2個のゲートを持つ品種があり、その場合は3SK〜のように3で始まる番号が付けられている。メーカーにより電流・電圧定格が判るような独自の型番をつける場合がある。

脚注

参考文献

関連項目

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads

![{\displaystyle I_{d}=K'{\frac {W}{L}}[(V_{gs}-V_{t})V_{ds}-{\frac {1}{2}}V_{ds}^{2}]}](http://wikimedia.org/api/rest_v1/media/math/render/svg/c42a038d81c989e3bb3f1d3eabc7cdaaf4536ee2)

![{\displaystyle C_{gdi}={\frac {1}{2}}WLC_{ox}[1-({\frac {V_{ds}}{V_{dsat}}})^{2}]}](http://wikimedia.org/api/rest_v1/media/math/render/svg/025c1d200655a3a63a58d78bf413f6f3e0328d34)