Loading AI tools

Da Wikipedia, l'enciclopedia libera

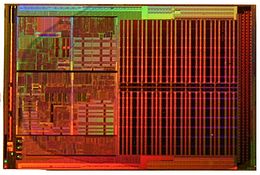

Opteron è un microprocessore x86 per server e workstation prodotto da AMD. È stato il primo processore della serie K8 ed il primo ad implementare un set di istruzioni a 64 bit grazie all'estensione AMD64. La prima versione di Opteron (nome in codice SledgeHammer) fu pubblicata il 22 aprile 2003 e destinata a competere sul mercato server e workstation, in particolare contro i processori Intel Xeon ed Itanium. Una nuova generazione di processori basata sulla microarchitettura K10 (nome in codice Barcelona) e in configurazione a 4 core fu annunciata il 10 settembre 2007. A febbraio 2011, le CPU Opteron più recenti (nome in codice Magny-Cours) adottano configurazioni a 8 e 12 core su socket G34.

| Opteron Central processing unit | |

|---|---|

| |

| Prodotto | dal aprile 2003 al presente |

| Produttore | AMD |

| Successore | AMD EPYC e AMD Ryzen Threadripper |

| Specifiche tecniche | |

| Frequenza CPU | 1,4 GHz / 3,2 GHz |

| Processo (l. canale MOSFET) | 130 nm / 45 nm |

| Frequenza HyperTransport | 800 MHz / 3200 MHz |

| Set di istruzioni | IA-32, x86-64 |

| N° di core (CPU) | 1, 2, 4, 6, 8, 12 |

| Socket |

|

Una delle principali caratteristiche di questa CPU è quella di poter eseguire programmi a 32 bit senza decrementi di velocità, offrendo allo stesso tempo la compatibilità con il software a 64 bit e la possibilità di accedere a più di 4 GB di memoria RAM (uno dei limiti fisici dei processori x86 a 32 bit). All'epoca della sua introduzione, questa combinazione di fattori conferiva all'Opteron un sensibile vantaggio prestazionale rispetto ai processori Itanium e agli Xeon a 64 bit di prima generazione (nome in codice Nocoma) che erano nettamente più lenti nell'esecuzione di software nativo a 32 bit. Inoltre, nonostante fossero disponibili da anni - sul mercato server/workstation - microprocessori basati su architettura RISC a 64 bit (SPARC, Alpha, PA-RISC, PowerPC, MIPS) l'adozione del set di istruzioni x86 garantiva - a costi contenuti - la compatibilità con la vasta base di software x86 installata permettendo, in questo modo, alla CPU di AMD di ottenere un positivo riconoscimento sul mercato.

Un'altra caratteristica dell'Opteron è il controller di memoria integrato. Questo componente, di solito incluso nel northbridge, mette in comunicazione la CPU con la memoria. L'implementazione nel die del processore, oltre a ridurre i costi dei chipset, fa in modo che i segnali elettrici non debbano più percorrere il Front Side Bus verso il northbridge e, da lì, verso la memoria (e viceversa), ma permette una comunicazione diretta con la RAM riducendone la latenza e migliorando le prestazioni complessive del sistema.

In sistemi multiprocessore (due o più processori su singola scheda madre), le CPU utilizzano l'architettura Direct Connect Architecture per comunicare con il sottosistema di input/output attraverso i link ad alta velocità del bus HyperTransport. In questo modo, ogni microprocessore può accedere alla memoria principale dell'altro in modo del tutto trasparente al programmatore. L'approccio degli Opteron ai sistemi multiprocessore è di tipo Non-Uniform Memory Access (NUMA) e differisce dalla più comune architettura a multiprocessore simmetrico; la RAM del sistema, infatti, non è equalmente accessibile a tutti i processori, ma ogni CPU possiede i propri banchi di memoria.

La CPU Opteron supporta nativamente sistemi multiprocessore a 8 vie (8 CPU su singola scheda), ma i server di fascia enterprise utilizzano sistemi di routing che possono estendere il supporto ad un numero maggiore di CPU per modulo.

Diversi benchmark evidenziano una migliore scalabilità dei sistemi multiprocessore Opteron rispetto alle controparti Intel Xeon delle generazioni precedenti alla serie Bloomfield.[1] Poiché ogni Opteron dispone di un proprio controller e di propri banchi RAM, l'aggiunta di nuove CPU aumenta, infatti, progressivamente la larghezza di banda della memoria; le CPU Opteron, inoltre, utilizzano uno switch interno per suddividersi i processi piuttosto che un bus comune condiviso e l'integrazione del controller della memoria garantisce un più rapido accesso alla RAM. Al contrario, gli Xeon condividono solo due bus per la comunicazione processore-processore e processore-memoria; di conseguenza, alla crescita del numero di CPU, la concorrenza tra i microprocessori per l'accesso alle risorse comuni produce una diminuzione dell'efficienza globale del sistema. Per ovviare al problema, nel novembre 2008, Intel è migrata ad una architettura di memoria simile a quella degli Opteron a partire dalla famiglia di processori Xeon (serie 35xx e successive) che si basano sulla microarchitettura Nehalem.

Il 21 aprile 2005, la compagnia di Sunnyvale presentò la prima versione multi core (serie 8yy Egypt su socket 940) del suo processore di classe server. Questa generazione di Opteron era costituita da processori dual core a 90 nm che integravano al proprio interno due cache L1 e L2 separate ed un controller di memoria comune; nonostante la presenza di due core, la dissipazione di calore si manteneva sugli stessi livelli (TDP di 85-95 W) delle serie più veloci a singolo core (serie 2yy Troy, serie 8yy Athens) che utilizzavano il medesimo processo produttivo. L'adozione di un'architettura dual core (e successivamente multicore) raddoppiava le prestazioni per singolo socket diminuendo, di conseguenza, il costo di allestimento di un sistema multiprocessore; il costo della scheda madre per questo tipo di sistemi, infatti, cresce notevolmente con l'aumento del numero di socket.

All'epoca della sua introduzione, il modello multi core più veloce era l'Opteron 875 (dual core a 2,2 GHz); il modello a singolo core più veloce dello stesso periodo era, invece, l'Opteron 252 a 2,6 GHz. Nonostante la minore velocità del modello 875, l'architettura dual core gli garantiva prestazioni superiori rispetto al 252 sia nelle applicazioni multithreaded che nell'esecuzione di molte applicazioni a thread singolo.

La seconda generazione di Opteron dual core a 90 nm (serie 12yy Santa Ana, serie 22yy e 82yy Santa Rosa) implementava il supporto alle memorie DDR2 e adottava due nuovi modelli di socket: il socket AM2 per la serie 12xx che supportava configurazioni a singolo processore e il socket F per i modelli Santa Rosa che supportavano configurazioni sia a doppio processore (serie 22yy) che a quattro o otto processori (serie 82yy).

AMD lanciò la terza generazione di Opteron multi core (quad core a 65 nm) nel settembre 2007. Basata sul core design dal nome in codice Barcelona, la nuova serie supportava configurazioni quad core a doppio processore su socket F con un TDP vicino (95-119 W) alle precedenti soluzioni dual core. Un ulteriore step produttivo (45 nm) fu raggiunto nell'aprile/giugno 2009 con il rilascio di nuovi modelli a quattro e sei core appartenenti, rispettivamente, alle serie 23yy e 83yy Shanghai e alla serie 24yy Istanbul.

A febbraio 2011, la serie Opteron più performante è la 61yy Magny-Cours a 45 nm su socket G34. Queste CPU a 8 e 12 core su modulo multi-chip sono costituite da due die a 4 e 6 core interconnessi tra loro attraverso un link HyperTransport (versione 3.1); supportano le memorie DDR3 e una maggiore velocità del link HyperTransport che raggiunge i 3,20 GHz (6,40 GT/s) contro i 2,40 GHz (4,80 GT/s) della serie Istanbul.

La prima versione di Opteron adottava il socket 940 che rimase il connettore di riferimento per tutti i modelli a singolo core. Nell'agosto 2005, vennero rilasciate, tuttavia, anche due serie (1yy Venus a singolo core e 1yy Denmark dual core) su socket 939 - lo stesso connettore delle CPU Athlon 64 dell'epoca - destinate al mercato dei server e delle workstation a basso costo. Fatta eccezione per la cache L2 di 1 MB (contro i 512 KB degli Athlon 64), queste CPU erano identiche agli Athlon con core design San Diego e Toledo, ma presentavano una velocità di clock inferiore a quella supportata dai core al fine di aumentare la stabilità di esercizio.

Il socket AM2 venne introdotto nella linea Opteron nel corso del 2006 attraverso la serie 12yy Santa Ana. Questi processori dual core a 90 nm supportavano esclusivamente configurazioni a singolo processore e presentavano una cache L2 di dimensioni doppie (2x1 Mb) rispetto a quella dei corrispettivi Athlon 64 X2 del settore home.

Sempre nel 2006, vennero introdotti gli Opteron su socket F che rimase il connettore di riferimento per tutte le serie multi core da 2 fino a 6 core (nomi in codice Santa Rosa, Barcelona, Shanghai e Istanbul) e con processi costruttivi a 90, 65 e 45 nm che furono rilasciate tra il 2006 e il 2009. Il nuovo connettore presentava un'interfaccia Land Grid Array con 1207 contatti (meccanicamente identica, ma generalmente non compatibile con la variante 1207 FX dello stesso socket) che, a differenza della più classica PGA, prevedeva che i pin di interconnessione fossero saldati direttamente sul connettore (e quindi sulla scheda madre) invece che sul processore. Il nuovo socket introdusse, nella linea Opteron, il supporto alla memoria DDR2 e alla versione 3.x del bus HyperTransport.

Nell'aprile 2008, AMD introdusse tre modelli Opteron quad core su socket AM2+ (nome in codice Budapest) per server a singolo processore. Si trattava di CPU a 65 nm con velocità comprese tra 2,1 e 2,3 GHz e simili alla serie Agena dei Phenom quad core. Il modello con stepping B2 era affetto dallo stesso bug al Translation Lookaside Buffer che affliggeva tutte le revisioni B2 della famiglia Phenom. Nel giugno 2009, AMD presentò tre modelli Opteron quad core a 45 nm su socket AM3 (nome in codice Suzuka) sempre destinati al mercato dei server a singolo processore. Questi processori, simili alla serie Deneb della famiglia Phenom II, presentavano velocità di clock comprese tra 2,5 e 2,9 GHz.

Tra il 2010 e il 2011, AMD introduce due nuove serie di processori multicore a 45 nm su socket C32 (LGA con 1207 contatti) e socket G34 (LGA con 1944 contatti). Il socket C32 (serie 41yy Lisbon a 4 e 6 core in configurazione a doppio processore) supporta la memoria DDR3; pur essendo fisicamente simile al socket F, è mappato in modo tale da prevenire l'inserzione accidentale delle CPU per socket F (che supportano solo memoria DDR2). Il socket G34 (serie 61yy Magny-Cours a 8 e 12 core in configurazione a 2 e 4 processori) supporta quattro canali di memoria DDR3 (due canali per die) e ne è previsto l'utilizzo anche da parte delle future versioni di Opteron come la serie Interlagos della famiglia Bulldozer. A differenza dei socket precedenti, al tradizionale supporto alla RAM ECC registrata viene aggiunto anche quello alle memorie ECC non registrate (unbuffered) e non-ECC.

La linea Opteron ha assistito, a partire dal 2007 con la serie Barcelona, anche all'implementazione della microarchitettura AMD K10. I nuovi processori incorporano una serie di migliorie rispetto alla precedente architettura K8 in particolare nel prefetch della memoria, e nelle capacità di esecuzione speculativa, SIMD e predizione delle diramazioni che ne aumentano le prestazioni nel calcolo parallelo pur mantenendo il medesimo profilo della generazione precedente in termini di consumi.[2] Con l'architettura K10, AMD ha introdotto anche un nuovo schema per la valutazione del consumo elettrico medio giornaliero dei processori denominato Average CPU Power (ACP).

Tutti gli Opteron per socket 940 e 939 sono marchiati con un numero di modello (model number) a tre cifre espresso nella forma Opteron XYY. Gli Opteron per i socket successivi adottano, invece, un numero di modello a quattro cifre nella forma Opteron XZYY. Per gli Opteron di prima, seconda e terza generazione, la prima cifra (X) indica il numero di CPU supportate dal sistema di riferimento:

Per gli Opteron su socket F, AM2, AM2+ e AM3 la seconda cifra (Z) rappresenta la generazione del processore:

Gli Opteron su socket C32 e G34 adottano, invece, un nuovo schema a quattro cifre. La prima cifra (X) indica sempre il numero di CPU supportate dal sistema di riferimento, ma con una differente nomenclatura:

La seconda cifra (Z) indica la generazione del processore: 1 si riferisce ai modelli basati sull'architettura K10 (Magny-Cours and Lisbon) mentre il numero 2 è riservato ai modelli basati sull'architettura Bulldozer.

Per tutti i modelli, le cifre YY indicano la frequenza di clock relativa tra i processori di una data serie per cui a valori più alti corrispondono frequenze di funzionamento più elevate. L'indicazione numerica è comparabile esclusivamente tra CPU della medesima generazione e con il medesimo numero di core.

Il suffisso HE o EE indica, rispettivamente, i modelli ad alta efficienza ed efficienza energetica (high-efficiency e energy-efficiency) con un profilo TDP più basso rispetto agli Opteron standard. Il suffisso SE indica invece i modelli top di gamma con un TDP superiore agli Opteron standard.

Con il passaggio al sistema produttivo a 65 nm, il nome in codice degli Opteron riprende il nome delle città che ospitano i gran premi di Formula 1 (AMD sponsorizza da lungo tempo il team Ferrari).

| Famiglia di processori AMD Opteron | |||

|---|---|---|---|

| Serie (nome in codice) | Processo costruttivo | Introduzione | Tipo |

| SledgeHammer Venus Troy Athens |

130 nm 90 nm 90 nm 90 nm |

Giu 2003 Ago 2005 Gen 2006 Gen 2006 |

Single core |

| Denmark Italy Egypt Santa Ana Santa Rosa |

90 nm 90 nm 90 nm 90 nm 90 nm |

Mar 2006 Mag 2006 Giu 2006 Ago 2006 Ago 2006 |

Dual core |

| Barcelona Budapest Shanghai |

65 nm 65 nm 45 nm |

Set 2007 Apr 2008 Nov 2008 |

Quad core |

| Istanbul | 45 nm | Giu 2009 | Esa core |

| Magny-Cours | 45 nm | Mar 2010 | Octa core |

| Magny-Cours | 45 nm | Mar 2010 | Dodeca core |

I seguenti supercomputer basati su Opteron sono menzionati tra i 10 supercomputer più veloci al mondo nella classifica TOP 500 del novembre 2010 (il numero in grassetto indica la posizione in classifica):[3]

AMD ha rilasciato alcuni Opteron (indicati in tabella) che non supportano la tecnologia Optimized Power Management (OPM). I processori dotati di OPM riducono il consumo energetico e la produzione di calore regolando automaticamente la tensione dei core e la frequenza di clock.

| Frequenza massima di P-State | Frequenza minima di P-State | Modello | Socket | Core # | TDP (W) | Processo costruttivo | Numero di serie (OPN) |

|---|---|---|---|---|---|---|---|

| 1400 MHz | N/A | 140 | Socket 940 | 1 | 82.1 | 130 nm | OSA140CEP5AT |

| 1400 MHz | N/A | 240 | Socket 940 | 1 | 82.1 | 130 nm | OSA240CEP5AU |

| 1400 MHz | N/A | 840 | Socket 940 | 1 | 82.1 | 130 nm | OSA840CEP5AV |

| 1600 MHz | N/A | 142 | Socket 940 | 1 | 82.1 | 130 nm | OSA142CEP5AT |

| 1600 MHz | N/A | 242 | Socket 940 | 1 | 82.1 | 130 nm | OSA242CEP5AU |

| 1600 MHz | N/A | 842 | Socket 940 | 1 | 82.1 | 130 nm | OSA842CEP5AV |

| 1600 MHz | N/A | 242 | Socket 940 | 1 | 85.3 | 90 nm | OSA242FAA5BL |

| 1600 MHz | N/A | 842 | Socket 940 | 1 | 85.3 | 90 nm | OSA842FAA5BM |

| 1600 MHz | N/A | 260 | Socket 940 | 2 | 55.0 | 90 nm | OSK260FAA6CB |

| 1600 MHz | N/A | 860 | Socket 940 | 2 | 55.0 | 90 nm | OSK860FAA6CC |

AMD ha richiamato alcuni processori Opteron single core con stepping E4, compresi i modelli x52 (2,6 GHz) e x54 (2,8 GHz) che utilizzano memoria DDR. La tabella seguente indica i processori richiamati, come indicato nelle note di produzione di AMD Opteron x52 e x54.[4]

| Frequenza massima di P-State | Singolo processore | Doppio processore | Multi processore | Socket |

|---|---|---|---|---|

| 2600 MHz | 152 | 252 | 852 | Socket 940 |

| 2800 MHz | N/A | 254 | 854 | Socket 940 |

| 2600 MHz | 152 | N/A | N/A | Socket 939 |

| 2800 MHz | 154 | N/A | N/A | Socket 939 |

I processori indicati possono produrre risultati inconsistenti quando occorrono simultaneamente le seguenti condizioni:

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.