circuit électronique numérique De Wikipédia, l'encyclopédie libre

Un circuit asynchrone est un circuit électronique numérique qui n'utilise pas de signal d'horloge global pour synchroniser ses différents éléments. À la place, ces derniers communiquent souvent localement en indiquant l'envoi et la réception de données. On parle parfois de « circuit auto-séquencé ».

Ils sont envisagés comme une alternative possible aux circuits synchrones, plus répandus, particulièrement pour diminuer la consommation d'énergie, puisqu'une horloge reste active en permanence. L'absence d'horloge peut apporter d'autres avantages, comme une vitesse accrue, une conception facilitée et une plus grande fiabilité.

En 2012, malgré ces nombreux atouts et bien qu'ils aient vu le jour presque en même temps que les circuits synchrones, de tels circuits restent minoritaires. Par exemple, la plupart des processeurs fabriqués sont synchronisés par une ou plusieurs horloges, tant sur le marché embarqué que pour les processeurs les plus performants, bien que l'on commence à voir apparaître des microcontrôleurs asynchrones.

L'histoire des circuits asynchrones est jalonnée de nombreuses réalisations majeures, la création d'ordinateurs ou de processeurs complets constituant une étape marquante. Elles ne doivent pas faire oublier néanmoins les avancées théoriques et, récemment, le développement d'outils de synthèse et de vérification qu'elles ont permis.

Tout comme dans les autres branches de l'électronique numérique, la recherche continue encore bien que le concept ait été exprimé dès les années 1950. Certains chercheurs présagent l'utilisation généralisée de techniques asynchrones[1], mais de telles prédictions[2] n'ont pas été réalisées par le passé.

La théorie des circuits asynchrones débute avec les travaux de David A. Huffman sur l'implémentation d'automates finis en 1953[2]. Le concept de « circuit asynchrone » tel qu'il est aujourd'hui, construit de manière modulaire en utilisant un protocole de communication entre les éléments, remonte à la fin des années 1950, quand les circuits « indépendants de la vitesse » reposant sur un protocole double-rail trois états sont introduits par David Muller[3] : son équipe construit l'ILLIAC I en 1952 et l'ILLIAC II en 1962[4]. Cependant, l'utilisation de ce type de circuits est alors jugée complexe : il n'y a pas de méthode simple permettant de réaliser de tels circuits, alors que les automates finis fournissent un modèle adapté[2].

Durant les années 1960 et 1970, quelques circuits asynchrones voient le jour, dont les « macromodules », composants asynchrones qui sont assemblés pour créer des systèmes complexes[5] : l'interface asynchrone permet de ne se soucier que de problèmes logiques.

La fin des années 1980 et le début des années 1990 connaissent un regain d'intérêt pour les techniques asynchrones[6], attribuable sans doute aux travaux d'Ivan Sutherland[7] et d'Alain Martin[8].

En 1989, Ivan Sutherland introduit le concept de micropipeline[9], implémentation[10] du protocole deux-phases à données groupées[Quoi ?]. Celui-ci est ensuite sans cesse amélioré, grâce à d'autres implémentations ou à l'utilisation de protocoles à quatre phases.

Cette période voit également l'apparition du premier microprocesseur asynchrone[11], le Caltech Asynchronous Microprocessor conçu à Caltech par l'équipe d'Alain Martin en 1989. Il utilise des circuits quasi-insensibles aux délais (QDI) générés à partir de code CHP[note 1] et possède une architecture RISC[12].

Il est suivi par les différentes versions de l'AMULET, basées sur les micropipelines, qui reprennent l'architecture ARM. La deuxième version introduit les micropipelines à quatre phases[13]. Un autre microprocesseur QDI de Caltech, le MiniMIPS, considéré comme particulièrement performant[14],[15], est conçu et testé à la fin des années 1990. D'autres sont conçus dans des universités de par le monde comme le TITAC 1 en 1994, le TITAC 2 en 1997 (architecture RISC, modèle proche du modèle QDI)[16] ou l'Aspro (RISC et QDI), en 2001 à Grenoble[17].

En parallèle, de nouvelles méthodes apparaissent : le codage quatre-états, plus efficace que les autres codages double-rail deux-phases, est inventé indépendamment par deux équipes en 1991 et 1992[18] ; les différents pipelines QDI apparaissent et sont utilisés dans les microprocesseurs ; des pipelines potentiellement plus efficaces, faisant des hypothèses temporelles, sont proposés[19].

À la fin des années 1990, des applications commerciales recommencent à voir le jour : de nombreuses entreprises commencent à utiliser des circuits basés sur une approche asynchrone ou à faire des recherches en ce sens.

Parmi elles, Philips fait figure de précurseur en mettant en œuvre des outils de synthèse de circuits asynchrones utilisant le langage Tangram dès 1995, et ce grâce aux outils de l'entreprise Handshake Solutions[7] ; la société dispose de microcontrôleurs 80C51 asynchrones dès 1998[20], qui sont utilisés dans plusieurs systèmes, dont des pagers et des cartes à puces[21].

Des chercheurs de Sun Microsystems, Intel et IBM prennent aussi part à cet engouement[7] : de 1995 à 1999, Intel conduit des recherches pour créer un décodeur pour le jeu d'instruction x86, RAPPID[5], tandis que les laboratoires de Sun sont à l'origine de plusieurs techniques, dont les pipelines de type GasP et une architecture pour processeur asynchrone, le counterflow pipeline[5],[22], qui n'a jamais été implémentée.

Enfin, de nombreuses start-ups exploitent les avantages de ces circuits, comme Theseus Logic dès 1996[note 2], Fulcrum en 2000[7], ou plus tard Tiempo[23], ou encore GreenArrays.

Les méthodes de synthèse et d'optimisation se sont aussi beaucoup améliorées, en particulier la synthèse à partir d'une spécification sous forme de réseau de Petri, menant à des outils comme Petrify[24]. D'autres pistes sont explorées : outre la compilation à partir de langages comme CHP ou Tangram citée plus haut, des outils visent la synthèse pour des modèles de délais bornés, comme Minimalist[25].

La recherche autour des circuits asynchrones se poursuit durant les années 2000 : de nouvelles implémentations de pipelines sont proposées tant multi-rails, comme LP2/1 en 2000[26], qu'à données groupées, comme IPCMOS en 2000[27] ou MOUSETRAP en 2007[28] ; les protocoles dits « single-track », utilisant un même fil pour la requête et l'acquittement, apparaissent[29], avec des implémentations comme STFB[30] et GasP[31].

En 2004, Epson crée un microcontrôleur flexible, qui est le premier du genre à être asynchrone[32].

Les circuits asynchrones possèdent plusieurs propriétés potentiellement intéressantes[33] : ils sont particulièrement prometteurs dans des domaines où la fiabilité est requise et pour des circuits à basse consommation, voire pour leur vitesse, bien qu'aucune méthode de conception ne possède tous ces avantages simultanément : il existe de très nombreuses façons de les concevoir, chacune avec ses avantages et ses problèmes.

Un signal d'horloge change d'état en permanence[note 3] : il peut représenter une part importante de la consommation d'un circuit[34]. A contrario, les circuits asynchrones ne sont actifs que lorsque des données sont disponibles. Dans le cas contraire, aucun transistor ne commute et la seule puissance consommée est due à leurs courants de fuite[note 4], ce qui en fait des candidats crédibles pour des circuits à basse consommation, ou lorsque la charge de travail évolue rapidement[34]. Cependant, pour assurer la communication entre les éléments, ils utilisent aussi plus de transistors et plus de fils pour une même quantité de données que leurs équivalents synchrones, ce qui peut diminuer les gains énergétiques et augmenter la taille des puces.

Certains circuits ont néanmoins montré des gains substantiels, avec une efficacité énergétique quatre fois supérieure à un équivalent synchrone pour une implémentation de microcontrôleur 80C51[20], ou proche des autres processeurs ARM du moment pour les processeurs AMULET.

Selon la méthodologie de conception employée, il est possible de créer des circuits utilisant peu d'hypothèses temporelles (insensibles ou quasi-insensibles aux délais par exemple) : ces circuits ont un comportement correct même si les propriétés physiques du circuit évoluent (à cause de la température[35], de la tension d'alimentation[36] ou d'un changement de technologie de fabrication)[37].

Les circuits asynchrones sont sensibles à tous les changements d'états des fils, et non à des signaux stabilisés échantillonnés lors de commutations de l'horloge[38] : on parle d'« aléas » pour désigner les variations indésirables des signaux[note 5],[39]. De tels problèmes sont à prendre en compte à la conception[40]. Cela leur donne aussi des comportements différents des circuits synchrones en cas d'erreurs ou de parasites. De plus, les protocoles asynchrones font des suppositions sur le comportement des circuits (principalement sur les délais)[Passage contradictoire avec la section Fiabilité] qui peuvent être infirmées par exemple par des variations de taille et de performance des transistors[41].

La conception d'un circuit synchrone demande quant à elle une connaissance précise des délais des portes, mais un délai trop élevé peut être compensé par une diminution de la fréquence d'horloge[25], au prix d'une baisse de la vitesse globale du circuit toutefois. Un autre problème récurrent est le phénomène de gigue d'horloge, et en général le problème de la distribution du signal d'horloge dans les circuits, qui compliquent la montée en fréquence et dont la correction nécessite l'utilisation de techniques complexes, parfois énergivores[42].

En électronique numérique, la vitesse peut être caractérisée de deux manières différentes[43],[note 6],[44] : la latence, qui correspond au temps que met une donnée pour être traitée par le circuit, et le débit, qui est le nombre de données traitées par unité de temps.

Les circuits permettant de passer des données d'un élément à l'autre peuvent introduire une latence supplémentaire pour traiter les signaux de requête et d'acquittement, diminuant le débit et augmentant la latence.

Par contre, la latence comme le débit ne sont pas limités par un signal d'horloge global, et ne sont pas forcément constants selon les parties du circuit ou les données en entrée. Par exemple, pour des circuits logiques tels que les additionneurs[45],[46], certaines implémentations asynchrones peuvent renvoyer le résultat dès qu'il est calculé (ici, la retenue), alors qu'un circuit synchrone doit toujours attendre jusqu'au signal d'horloge suivant (qui doit être suffisamment tard pour que les calculs soient terminés même dans le pire des cas). Ils permettent donc de bonnes implémentations en temps moyen de calcul, bien que le pire des cas puisse être bien plus long[47].

Certains microprocesseurs asynchrones fabriqués exhibent ainsi de très bonnes performances, la vitesse du MiniMIPS étant environ égale à quatre fois celle de processeurs équivalents pour une efficacité énergétique proche[15].

Il est facile d'utiliser ensemble des circuits asynchrones différents (même utilisant des protocoles différents, en ajoutant un élément traduisant de l'un à l'autre), car aucun élément n'a besoin d'être commun, au contraire de l'horloge des circuits synchrones. Il est même possible de les interfacer avec des circuits synchrones, et d'interfacer des circuits synchrones entre eux par des liaisons asynchrones[48],[note 7]. Cette modularité est un avantage pour l'interfaçage avec d'autres éléments[49],[50], mais aussi pour la conception en général, qui s'en trouve facilitée[50] et peut être faite avec des langages de haut niveau.

L'absence d'une horloge unique et donc d'une base de temps globale simplifie grandement le processus, en évitant de devoir prendre en compte les délais et la distribution du signal d'horloge à toutes les échelles lors de la phase de conception[51], mais elle introduit d'autres problèmes qui doivent être pris en compte par les outils ou par le concepteur.

Du fait que les différents éléments ne sont pas synchronisés, les émissions électromagnétiques sont réduites tandis que la consommation électrique est lissée[52] : cela peut être exploité pour se prémunir de certaines attaques exploitant celles-ci[53], car il est alors plus difficile de déduire l'activité du circuit à partir de ses émissions ou de sa consommation. Cette propriété peut être exploitée dans tout environnement où les émissions électromagnétiques doivent être minimisées[52], par exemple au voisinage d'une antenne.

Un circuit synchrone, a contrario, a tendance à émettre des ondes harmoniques de sa fréquence d'horloge et à présenter des pics de puissance consommée à chaque front d'horloge[52].

Comme les synchronisations entre éléments se font au niveau local, les pipelines asynchrones sont naturellement élastiques[54], c'est-à-dire qu'ils peuvent contenir un nombre variable de données. C'est une conséquence du fait que celles-ci se propagent indépendamment de celles qui les suivent.

L'absence de base de temps globale permet de traiter facilement des événements extérieurs[55]. Un tel événement peut survenir au plus mauvais moment, par exemple en même temps qu'un signal d'horloge ou que l'arrivée de données, ce qui peut entraîner l'apparition d'un état métastable dont on s'accommode difficilement en électronique synchrone[55]. Pour des circuits asynchrones, en revanche, il existe des portes spécialisées permettant de réaliser un « arbitrage »[note 8],[56] : il est possible d'attendre jusqu'à ce que l'état métastable soit résolu[55].

Il existe de nombreux moyens de réaliser une interface asynchrone entre deux éléments[57]. Dans une communication à sens unique impliquant un émetteur et un destinataire, l'envoi des données est signalé par une requête, notée « Req », et leur réception par un acquittement, noté « Ack » : on parle d'une « poignée de main » pour désigner cet échange. Un envoi se déroule comme suit : lorsque ses données sont prêtes, l'émetteur les copie en sortie et en informe le destinataire via une requête ; quand celui-ci les a transmises, copiées ou utilisées, il renvoie un acquittement pour signifier qu'il n'en a plus besoin. L'émetteur peut alors envoyer de nouvelles données[58].

La requête et l'acquittement ne sont pas forcément des signaux à part ; ils peuvent être codés chacun sur un fil, mais ce n'est pas une nécessité : différents codages existent.

On distingue deux familles de protocoles[58] selon la façon dont les événements, tels que les requêtes et les acquittements, sont codés :

Les protocoles varient ensuite selon les signaux utilisés. Très fréquemment, la requête est codée sur les mêmes fils que les données, ce qui donne les codages sur plusieurs fils présentés dans la section suivante. Certains protocoles, moins répandus, n'ont pas de fil séparé pour l'acquittement et utilisent un ou des fils sur lesquels l'émetteur comme le destinataire peuvent agir[note 9],[30],[31] : de cette manière, il n'y a que deux phases (envoi, puis remise à zéro après réception), et moins de fils de communication. D'autres protocoles ont été proposés : basé sur des impulsions, c'est-à-dire une remise à zéro précoce des fils[59], ou supprimant les bascules[note 10],[60], voire utilisant des signaux non binaires, avec plus de deux tensions signifiantes[18].

Dans les circuits asynchrones, il existe de nombreux moyens de coder les données. Le codage le plus évident, similaire à celui des circuits synchrones, utilise un fil pour un bit[note 11] ; en asynchrone, on l'appelle « codage à données groupées »[61]. Cependant, comme toute transmission de données asynchrone s'accompagne d'une requête permettant de la signaler, une autre technique est de coder ensemble les données et la requête, comme dans les codages « double-rail », sur deux fils, qui sont très utilisés.

Dans ce protocole, un ou plusieurs fils transportent les données, avec un fil par bit. Un fil (Req) est destiné à la requête de l'émetteur indiquant que les données sont prêtes, et un autre (Ack) à la réponse du destinataire. De tels circuits sont conçus en utilisant un modèle où certains délais sont considérés comme bornés, car sinon les données pourraient ne pas être valides alors même que la requête serait arrivée[61].

On parle souvent de micropipelines pour désigner les circuits utilisant ce codage, avec soit deux soit quatre[13] phases. À l'origine, ce terme fait référence à un pipeline asynchrone utilisant un protocole deux-phases données-groupées[9].

Ici, il n'y a pas de fil séparé destiné à l'envoi de la requête, qui est implicite[note 12],[62]. De manière générale, il existe des codages complexes dits « m parmi n », dont on n'utilise surtout qu'un cas particulier dit « double rail », avec deux fils. Dans ces codages, une donnée est représentée par m transitions parmi n fils, et le destinataire peut considérer que les données sont valides dès lors que m transitions ont eu lieu, ce qui rend le codage lui-même insensible aux délais[63],[64],[note 13]. Un tel codage est approprié tant pour un protocole à quatre phases, où on remet tous les fils à leur état initial après chaque échange, que pour un protocole à deux phases.

Le type le plus simple de codage m parmi n est le codage 1 parmi n, dit aussi « one-hot » : dans ce cas, il y a n transitions possible, ce qui permet de représenter un chiffre en base n, le cas particulier du double-rail donnant une écriture binaire. Bien sûr, d'autres codages sont possibles[64], mais peu usités, comme les autres codages m parmi n.

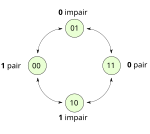

Les protocoles double-rail one-hot sont largement répandus[note 14],[63]. Le protocole à quatre phases, aussi dit « codage trois-états », est le plus populaire[61]. Il comporte une valeur invalide (typiquement 00), et deux valeurs signifiantes (01 codant 0 et 10 codant 1 par exemple), l'état 11 étant inutilisé. L'émetteur repasse par l'état invalide à chaque envoi de données. Pour signifier que le destinataire a remarqué le changement de valeur, une réponse est émise à chaque fois, y compris au passage par l'état invalide, ce qui permet au signal d'acquittement de revenir aussi à son état initial. Dans le protocole à deux phases, une seule transition a lieu à chaque envoi, et elle est acquittée par une seule transition également[65].

Enfin, un autre codage double rail existe, destiné à un protocole à deux phases : tous les états sont signifiants, mais deux codes correspondent à chaque valeur d'un bit, ce qui permet bien de changer d'état à chaque nouvelle donnée ; on parle de codage quatre-états[note 15],[18].

Les circuits asynchrones regroupent en fait plusieurs classes de circuits[66] ayant des propriétés différentes, selon les hypothèses faites à la conception. En effet, la communication locale des circuits asynchrones peut permettre de s'affranchir de certaines contraintes de temps, les éléments indiquant eux-mêmes la disponibilité des données. Ces propriétés s'échelonnent de l'insensibilité aux délais (on parle de circuits DI), où le circuit est correct quels que soient les délais des portes et des fils, au modèle des délais bornés, où les délais ont une limite connue. Deux classes de circuits intermédiaires sont utilisées : quasi-insensibles aux délais (QDI) et indépendants de la vitesse (SI).

Pour simplifier, ces modèles considèrent les signaux comme booléens[67], les portes et les fils apportant juste un retard de propagation. En réalité, les délais sont parfois plus complexes que de simples retards[note 16], les signaux sont en réalité des tensions et non des valeurs binaires[note 17], et les portes elles-mêmes sont souvent implémentées en utilisant un modèle de délais bornés.

De tels circuits fonctionnent correctement quels que soient les délais dans les fils et les portes. Ils ne sont cependant pas réalisables avec des portes logiques simples (les seules portes logiques à une sortie utilisables sont les portes C et l'inverseur)[68], et ne sont donc pas souvent utilisés en pratique. Ce modèle est cependant utilisable avec des portes plus complexes, elles-mêmes implémentées suivant d'autres hypothèses.

Les circuits quasi-insensibles aux délais (QDI) ajoutent l'hypothèse, pour la conception, qu'il est possible d'obtenir des « fourches isochrones », c'est-à-dire une séparation d'un fil en plusieurs possédant exactement le même délai, supposition qui est généralement considérée comme réalisable en pratique[note 18], mais présente certains risques, car les délais des fils peuvent être longs en comparaison de ceux des portes avec les techniques CMOS[note 19],[69], et car la propagation des signaux est plus complexe que de simples délais sur des signaux binaires. C'est pourtant un modèle de conception largement utilisé, car de tels circuits sont Turing-complets[67].

On peut aussi considérer les délais dans les fils comme étant négligeables. Cela se vérifie difficilement dans les systèmes actuels[70], c'est pourquoi on peut leur préférer des circuits conçus comme quasi-insensibles aux délais. Cependant, les deux hypothèses sont en fait très proches[70], le cas indépendant de la vitesse revenant à considérer toutes les fourches comme isochrones. Malgré ce défaut apparent, cette hypothèse de conception est donc très répandue[note 20].

Comme l'indique leur nom, les délais dans les portes et les fils sont supposés connus ou bornés par une durée connue. On les appelle parfois circuits de Huffman. C'est le principe de conception en électronique synchrone, où les impulsions d'horloge se font à intervalle suffisamment long pour que les signaux se soient propagés et stabilisés dans tout le circuit. En électronique asynchrone, ce modèle est aussi utilisé, tout d'abord pour concevoir la structure interne de nombreuses portes complexes vues comme des automates finis[71], mais également dans les micropipelines[note 21],[72], ou pour obtenir des circuits particulièrement performants[note 22].

On distingue parfois les micropipelines des autres circuits à délais bornés, en les définissant comme des circuits possédant une partie de contrôle insensible aux délais envoyant les signaux d'acquittement et de requêtes, et des bascules de mémorisation construites selon un modèle de délais bornés[73], ce qui en fait une méthode de conception à part entière. Selon cette définition, les micropipelines ne regroupent donc pas tous les circuits utilisant un protocole à données groupées, car les structures de contrôle peuvent être aussi à délais bornés.

Une différence majeure entre les conceptions synchrone et asynchrone est la prise en compte des aléas logiques. Un aléa est une transition non désirée sur un fil. Dans un circuit synchrone, les aléas sont sans conséquences puisqu'on ne considère que des signaux stabilisés au moment des fronts d'horloge ; ce n'est plus le cas en asynchrone, et un aléa peut conduire à un blocage du circuit ou une erreur.

Les aléas peuvent apparaitre à la suite d'une mauvaise décomposition du circuit en portes logiques : les portes et les fils ayant des délais, les différences de temps de propagation entre signaux peuvent conduire le circuit à osciller. C'est aussi possible pour certains changements simultanés des entrées. Enfin, la cause peut être physique, en particulier la diaphonie, qui devient plus critique avec les progrès de la miniaturisation.

On peut concevoir un circuit asynchrone soit par compilation de langages de haut niveau[74] soit par une description de son comportement, par exemple à partir de réseaux de Petri[75],[76].

Différentes méthodologies et outils de synthèse ont été développés[77], tant dans le milieu académique (Balsa[78], « Caltech »[79], Minimalist[80],[81], Petrify[82]) que dans l'industrie (Tangram[83], Null Convention Logic[84],[85]). Cependant, le manque d'outils de synthèse et de vérification aussi complets que ceux destinés à l'électronique synchrone reste un des freins majeurs à l'adoption de méthodologies asynchrones.

De nombreuses méthodologies de conception partent d'un langage de haut niveau qui est soit compilé, soit directement traduit en un circuit. De cette manière, la conception est relativement intuitive, et il est possible de construire un système complexe par assemblage de briques de base. Parmi ces langages, beaucoup sont dérivés de CSP, qui reflète bien la concurrence : Tangram a été développé dans ce but chez Philips, Balsa à l'université de Manchester, CHP à Caltech[86]. On peut aussi utiliser des langages de description matérielle plus classiques, comme Verilog ou VHDL, qui n'y sont pas spécifiquement destinés[87].

D'autres méthodes de synthèse existent, basées elles sur une description du comportement du circuit. Elles permettent d'obtenir des circuits efficaces[88], mais au prix d'une conception plus complexe, tant du point de vue du programmeur que de celui de la complexité algorithmique[89]. La spécification se fait sous forme de graphe : soit un réseau de Petri ou un réseau de Petri simplifié appelé graphe de transitions de signaux (STG), soit un automate fini (ASM)[88].

Selon les outils, le circuit généré sera indépendant de la vitesse ou à délais bornés[89]. En plus de ces contraintes temporelles, une limitation courante est une restriction du nombre d'entrées qui sont autorisées à changer simultanément. On dit que le circuit fonctionne en « mode fondamental » si les entrées ne changent que lorsque le circuit a atteint un état stable[90],[91], et en « mode entrée-sortie » si elles peuvent changer dès que le circuit a répondu par un changement d'état[91].

Il est nécessaire d'être capable de vérifier que le circuit se comporte comme prévu : cela passe par une série de vérifications avant et après la production : il s'agit d'éviter d'une part les problèmes dus à des erreurs lors de la phase de conception, ce qui peut être fait par des preuves formelles et des simulations, et d'autre part ceux dus à des défauts lors de la fabrication qui peuvent rendre certains circuits fabriqués incorrects[44]. Pour ces derniers, il faut élaborer de nouveaux protocoles de test applicables aux circuits produits, avec des algorithmes spécifiques aux circuits asynchrones.

L'optimisation des circuits asynchrones a donné lieu à de nombreuses recherches. Leurs propriétés sont très différentes des circuits synchrones : ils rendent impossibles certaines optimisations classiques, qui peuvent introduire des incertitudes temporelles[note 23] et des aléas, mais l'analyse des performances est aussi complètement différente[44],[92] du fait de l'absence d'un rythme commun : les éléments ont des délais variables et interagissent de manière complexe. L'optimisation, généralement apportée par l'outil de conception, utilise plusieurs transformations[92] à différents niveaux : au-delà du choix de la technologie, il est possible d'optimiser à un niveau « abstrait » (changement de codage des données, ajout d'étages de pipelines, etc.) aussi bien qu'à un niveau local (remplacement de groupes de portes par des groupes équivalents). Ce processus est automatisé, et peut recourir à des simulations pour évaluer les performances d'un circuit.

La conception de circuits asynchrones souffre d'un manque d'outils dédiés[93], les principaux langages de description de matériels ciblant la conception de circuits synchrones, bien qu'il soit possible de les utiliser en électronique asynchrone.

Une autre limitation tient à la formation, qui est généralement focalisée sur l'électronique synchrone, l'électronique asynchrone étant moins répandue[94] et souvent vue comme moins efficace ou plus complexe[12].

Enfin, les problèmes de fiabilités dus entre autres à des contraintes temporelles sont aussi présents dans les circuits asynchrones[69], et peuvent être particulièrement graves puisque les temps de propagation ne sont pas réglables comme avec une horloge[95]. Ils sont surtout présents dans des circuits faisant beaucoup d'hypothèses temporelles (comme le modèle de délais bornés), mais existent aussi avec des modèles introduisant une certaine insensibilité aux délais[69] ; du fait des imperfections des techniques de fabrication, ils ne peuvent être évités que par des simulations en premier lieu, puis des tests après production[44].

De nombreux critères entrent en ligne de compte pour évaluer les différents types de circuits asynchrones : leur vitesse en termes de latence et de débit, leur taille et leur consommation, mais aussi leur fiabilité. Ces caractéristiques varient beaucoup selon le protocole utilisé et l'implémentation choisie, mais aussi les techniques de fabrication et les optimisations appliquées au circuit. Cette section donne donc seulement un aperçu de l'impact de certains choix sur le circuit.

Les protocoles à deux et à quatre phases ont chacun leurs avantages. À priori, les protocoles à deux phases impliquent moins de transitions, et devraient donc être plus rapides et plus économes. En pratique, cependant, un passage par un protocole à quatre phases est réalisé à un moment ou à un autre : c'est entre autres le cas de l'implémentation d'origine des micropipelines. De plus, il est plus simple d'implémenter les protocoles à quatre phases et leur nombre restreint d'états possibles[65], particulièrement lorsqu'il faut effectuer des calculs en multi-rail.

De fait, les deux protocoles ont été utilisés pour le codage données-groupées. Par contre, les protocoles sur plusieurs rails utilisés sont plutôt de type retour à zéro[65], sauf lorsque la communication se fait sur de longs fils, donc avec des délais et une consommation plus importants, et qu'il devient intéressant de restreindre le nombre de transitions[65], comme dans le cas de liens série[96].

La première différence tient au nombre de fils utilisés : les protocoles à données groupées n'utilisent qu'un fil par bit, plus la requête et l'acquittement, alors que les protocoles multi-rails en utilisent plusieurs. Cela rend ces derniers moins adaptés à l'envoi de nombreux bits ; par contre, ils permettent de créer des circuits QDI, plus robustes ; ils ont aussi l'avantage d'inclure la requête dans les données, ce qui permet directement la création de portes à complétion anticipée, renvoyant les résultats sans attendre que toutes les données d'entrée soient disponibles[97],[46],[note 24] (par exemple une porte ou si une entrée vaut 1) ; de tels pipelines « à grains fins », avec une requête par bit, autorisent l'envoi séparé de chaque partie du résultat.

Les circuits à données groupées sont censés consommer moins et occuper moins de place[98] ; on peut y réutiliser[note 25] des portes issues de la logique combinatoire, comme pour les circuits synchrones ; il est alors nécessaire d'adapter le délai imposé au signal de requête aux délais des portes[note 26], soit par un choix de délai à partir des opérandes, soit par une détection de fin de calcul à partir de la consommation du circuit. En termes de fréquence pure, ils se comportent en général légèrement mieux[27], mais cela n'est pas forcément représentatif de la réalité, où des calculs complexes sont réalisés avec des pipelines non linéaires. On constate ainsi que les microprocesseurs asynchrones les plus performants, comme le MiniMIPS, ont utilisé des protocoles multi-rails, alors que le 80C51 de Philips[20] et les processeurs AMULET, qui visent une faible consommation, utilisent des protocoles données-groupées.

Parfois, on utilise ensemble les deux types de protocole pour exploiter le mieux possible les avantages de chacun, en choisissant par exemple du double-rail pour les calculs mais du données-groupées pour les interfaces[46].

Il existe de nombreuses implémentations de protocoles données-groupées : en deux-phases, outre l'implémentation d'origine[9], on en trouve basées sur des bascules D réagissant aux deux fronts d'horloge[99], ou de type MOUSETRAP[28].

Pour les protocoles à quatre phases données-groupées, on peut supprimer certaines dépendances entre les signaux de requête et d'acquittement émis par des étages contigus, lui permettant d'en renvoyer certains plus tôt[100]. On obtient ainsi des structures plus complexes, mais potentiellement plus performantes.

De même, en multi-rail quatre-phases, on distingue trois types de circuits courants, tous trois QDI : WCHB, PCHB et PCFB[101]. En WCHB, un étage attend la validité (respectivement la remise à zéro) de toutes ses entrées avant de renvoyer une donnée à sa sortie (respectivement de revenir à l'état intermédiaire). Par conséquent, au plus un étage sur deux contiendra réellement des données, d'où le nom de « half-buffer », et surtout la complétion anticipée est impossible[102]. Les protocoles PCHB et PCFB, en vérifiant explicitement la validité des entrées, peuvent renvoyer des données avant l'arrivée de toutes les entrées et permettent une remise à zéro rapide[note 27], sans attendre l'invalidité des entrées[103],[104]. Le protocole PCFB permet en plus à chaque étage de contenir des données en renvoyant un acquittement dès la remise à zéro des étages précédents : on parle de « full-buffer »[104]. Cependant, la simplicité des circuits de type WCHB les rend parfois plus rapides que les autres[102], tandis que les circuits de type PCFB requièrent plus de porte logiques[105] : le choix n'est donc pas évident.

D'autres types de pipelines sont possibles en utilisant un modèle de délais bornés : avec de la logique à précharge[note 28], comme PS0[19] ou LP2/1[26], ou avec des protocoles « single-track »[30]. Toutefois, bien que plus rapides, ils sont aussi moins fiables du fait de l'ajout d'hypothèses temporelles.

Une particularité des protocoles multi-rail est la possibilité d'utiliser plus de fils pour coder les données grâce à un codage 1 parmi n plutôt que double-rail, diminuant ainsi le nombre de fils qui commutent, ce qui peut diminuer la consommation électrique[106].

Parmi les propriétés des circuits, beaucoup dépendent des techniques de fabrication, que ce soient le processus de fabrication lui-même ou les bibliothèques de composants utilisées. L'amélioration des possibilités d'intégration due à celle des processus de fabrication, qui est quantifiée par la loi de Moore, permet d'obtenir des circuits électroniques plus compacts et performants. L'optimisation des circuits asynchrones peut aussi passer par le choix de composants adaptés, par l'optimisation du layout, c'est-à-dire de l'agencement des composants sur le circuit intégré, voire par le contrôle des tailles des transistors de manière à adapter au mieux chaque porte à son fan-out[107].

Les circuits électroniques consomment d'autant plus que leur tension d'alimentation est élevée. Par conséquent, on cherche à la minimiser pour des circuits à basse consommation. Pour réduire celle-ci sans sacrifier les performances, on peut adapter la tension à la charge de travail du circuit ou à la vitesse désirée[106]. Cette optimisation existe aussi pour des circuits synchrones, mais nécessite conjointement une adaptation de la fréquence d'horloge qui se fait lentement, là où le processus de mise en veille et de sortie de veille d'un circuit asynchrone est extrêmement rapide[106].

Seamless Wikipedia browsing. On steroids.