Arquitectura ARM

arquitectura de procesador basada en RISC De Wikipedia, la enciclopedia libre

ARM, anteriormente Advanced RISC Machine, originalmente Acorn RISC Machines, es una arquitectura RISC (Reduced Instruction Set Computer, «Ordenador con Conjunto Reducido de Instrucciones») de 32 bits y, con la llegada de su versión V8-A, también de 64 Bits, desarrollada por ARM Holdings. La arquitectura ARM es el conjunto de instrucciones de 32 y 64 bits más ampliamente utilizado en unidades producidas.[1][2] Concebida originalmente por Acorn Computers para su uso en ordenadores personales, los primeros productos basados en ARM eran los Acorn Archimedes, lanzados en 1987.

| Arquitectura ARM | ||

|---|---|---|

| ||

| Información | ||

| Tipo | Registro–Registro | |

| Desarrollador | Acorn Computers/Arm Ltd. | |

| Fecha de lanzamiento | 1985 | |

| Datos técnicos | ||

| Conjunto de instrucciones | RISC | |

| Ancho en bits | 32-bit • 64-bit | |

Un enfoque de diseño basado en RISC permite que los procesadores ARM requieran una cantidad menor de transistores que los procesadores x86 CISC, típicos en la mayoría de ordenadores personales. Este enfoque de diseño nos lleva, por tanto, a una reducción de los costes, calor y energía. Estas características son deseables para dispositivos que funcionan con baterías, como los teléfonos móviles, tabletas, etc.

La relativa simplicidad de los procesadores ARM los hace ideales para aplicaciones de baja potencia. Como resultado, se han convertido en los dominantes dentro del mercado de la electrónica móvil e integrada, encarnados en microprocesadores y microcontroladores pequeños, de bajo consumo y relativamente bajo costo. En 2005, alrededor del 98% de los más de mil millones de teléfonos móviles vendidos utilizaban al menos un procesador ARM.[3] Desde 2009, los procesadores ARM son aproximadamente el 90% de todos los procesadores RISC de 32 bits integrados. Cabe hacer mención que no existe una tabla de equivalencias de rendimiento entre las distintas tecnologías de procesadores[4] que se utilizan generalmente en la electrónica de consumo, incluyendo PDA, tabletas, teléfonos móviles, teléfonos inteligentes, relojes inteligentes, videoconsolas portátiles, calculadoras, reproductores digitales multimedia (fotos, vídeos, etc.) y periféricos de ordenador como discos duros y enrutadores.

La arquitectura ARM es licenciable. Esto significa que el negocio principal de ARM Holdings es la venta de núcleos IP (propiedad intelectual), estas licencias se utilizan para crear microcontroladores y CPUs basados en este núcleo. Las empresas que son titulares de licencias ARM actuales o anteriores incluyen a Alcatel-Lucent, Apple Inc., AppliedMicro, Atmel, Broadcom, Cirrus Logic, Digital Equipment Corporation, Ember, Energy Micro, Freescale, Intel (a través de DEC), LG, Marvell Technology Group, Microsemi, Microsoft, NEC, Nintendo, Nokia, Nuvoton, Nvidia, Sony, MediaTek, NXP (antes Philips Semiconductors), Oki, ON Semiconductor, Psion, Qualcomm, Samsung, Sharp, STMicroelectronics, Symbios Logic, Texas Instruments, VLSI Technology, Yamaha, y ZiiLABS.

Los procesadores ARM son desarrollados por ARM y los titulares de las licencias de ARM. Prominentes familias de procesadores ARM desarrollados por ARM Holdings incluyen el ARM7,V8-A ARM9, ARM11 y Cortex. Entre los procesadores ARM desarrollados por firmas licenciatarias se incluyen Applied Micro Circuits Corporation X-Gene, DEC StrongARM, Freescale i.MX, Marvell Technology Group XScale, NVIDIA Tegra, Qualcomm Snapdragon, Texas Instruments OMAP, Samsung Exynos, Apple Ax, ST-Ericsson NovaThor, Huawei K3V2 e Intel Medfield.

Historia

Resumir

Contexto

El diseño de la arquitectura ARM comenzó en 1983 como un proyecto de desarrollo por la empresa Acorn Computers. Sophie Wilson y Steve Furber lideraban el equipo, cuya meta era, originalmente, el desarrollo de un procesador avanzado, pero con una arquitectura similar a la del MOS 6502. La razón era que Acorn tenía una larga línea de ordenadores personales basados en dicho microprocesador, por lo que tenía sentido desarrollar uno con el que los desarrolladores se sintieran cómodos.

El equipo terminó el diseño preliminar y los primeros prototipos del procesador en el año 1985, al que llamaron ARM1. La primera versión utilizada comercialmente se bautizó como ARM2 y se lanzó en el año 1986.

La arquitectura del ARM2 posee un bus de datos de 32 bits y ofrece un espacio de direcciones de 26 bits, junto con 16 registros de 32 bits. Uno de estos registros se utiliza como contador de programa, aprovechándose sus 4 bits superiores y los 2 inferiores para contener los flags de estado del procesador.

El ARM2 es probablemente el procesador de 32 bits útil más simple del mundo, ya que posee solo 30 000 transistores. Su simplicidad se debe a que no está basado en microcódigo (sistema que suele ocupar en torno a la cuarta parte de la cantidad total de transistores usados en un procesador) y a que, como era común en aquella época, no incluye caché. Gracias a esto, su consumo en energía es bastante bajo, a la vez que ofrece un mejor rendimiento que un 286. Su sucesor, el ARM3, incluye una pequeña memoria caché de 4 KB, lo que mejora los accesos a memoria repetitivos.

A finales de los años 1980, Apple Computer comenzó a trabajar con Acorn en nuevas versiones del núcleo ARM. En Acorn se dieron cuenta de que el hecho de que el fabricante de un procesador fuese también un fabricante de ordenadores podría echar para atrás a los clientes, por lo que en 1990 se decidió crear una nueva compañía llamada Advanced RISC Machines, que sería la encargada del diseño y gestión de las nuevas generaciones de procesadores ARM.

Este trabajo derivó en el ARM6, presentado en 1991. Apple utilizó el ARM 610 (basado en el ARM6), como procesador básico para su innovador PDA, el Apple Newton. Por su parte, Acorn lo utilizó en 1994 como procesador principal en su RiscPC.

El núcleo mantuvo su simplicidad a pesar de los cambios: en efecto, el ARM2 tiene 30 000 transistores, mientras que el ARM6 solo cuenta con 35 000. La idea era que el usuario final combinara el núcleo del ARM con un número opcional de periféricos integrados y otros elementos, pudiendo crear un procesador completo a la medida de sus necesidades.

La mayor utilización de la tecnología ARM se alcanzó con el procesador ARM7TDMI, con millones de unidades en teléfonos móviles y sistemas de videojuegos portátiles.

DEC licenció el diseño, lo cual generó algo de confusión debido a que ya producía el DEC Alpha, y creó el StrongARM. Con una velocidad de reloj de 233 MHz, este procesador consumía solo 1 W de potencia (este consumo de energía se ha reducido en versiones más recientes). Esta tecnología pasó posteriormente a manos de Intel, como fruto de un acuerdo jurídico, que la integró en su línea de procesadores Intel i960 e hizo más ardua la competencia.

Freescale (una empresa que derivó de Motorola en el año 2004), IBM, Infineon Technologies, OKI, Texas Instruments, Nintendo, Philips, VLSI, Atmel, Sharp, Samsung y STMicroelectronics también licenciaron el diseño básico del ARM.

El diseño del ARM se ha convertido en uno de los más usados del mundo, desde discos duros hasta juguetes. Hoy en día, cerca del 75% de los procesadores de 32 bits poseen este chip en su núcleo.

Familias

Resumir

Contexto

| Familia | Versión de Arquitectura | Núcleo | Características | Caché (I/D)/MMU | MIPS efectivos @ MHz | Campos de Aplicación |

|---|---|---|---|---|---|---|

| ARM1 | ARMv1 (obsoleto) | ARM1 | Nulo | ARM Evaluation System segundo procesador para BBC Micro | ||

| ARM2 | ARMv2 (obsoleto) | ARM2 | Añadida instrucción MUL (multiplicar) | Nulo | 4 MIPS @ 8 MHz 0.33 DMIPS/MHz |

Acorn Archimedes, Chessmachine |

| ARMv2a (obsoleto) | ARM250 | Integrado MEMC (MMU), gráficos y un procesador de E / S. Añadidas instrucciones SWP y SWPB (swap). | Nulo, MEMC1a | 7 MIPS @ 12 MHz | Acorn Archimedes | |

| ARM3 | ARMv2a (obsoleto) | ARM2a | Primera integración de una memoria caché en un ARM. | 4K unificados | 12 MIPS @ 25 MHz 0.50 DMIPS/MHz |

Acorn Archimedes |

| ARM6 | ARMv3 (obsoleto) | ARM60 | Soporte de dirección de memoria de 32 bits (frente a los 26 bits) | Nulo | 10 MIPS @ 12 MHz | 3DO Interactive Multiplayer, Zarlink GPS Receiver |

| ARM600 | Como ARM60, caché y un bus cooprocesador (para la unidad de coma flotante FPA10). | 4K unificados | 28 MIPS @ 33 MHz | |||

| ARM610 | Como ARM60, caché, sin bus coprocesador. | 4K unificados | 17 MIPS @ 20 MHz 0.65 DMIPS/MHz |

Acorn Risc PC 600, Apple Newton Serie 100 | ||

| ARM7 | ARMv3 (obsoleto) | ARM700 | 8 KB unificados | 40 MHz | Acorn Risc PC prototipo de CPU card | |

| ARM710 | Como ARM700 | 8 KB unificados | 40 MHz | Acorn Risc PC 700 | ||

| ARM710a | Como ARM700 | 8 KB unificados | 40 MHz 0.68 DMIPS/MHz |

Acorn Risc PC 700, Apple eMate 300 | ||

| ARM7100 | Como ARM710a, SoC integrado. | 8 KB unificados | 18 MHz | Psion Series 5 | ||

| ARM7500 | Como ARM710a, SoC integrado. | 4 KB unificados | 40 MHz | Acorn A7000 | ||

| ARM7500FE | ARM7500, "FE" añadido un FPA y un controlador de memoria EDO. | 4 KB unificados | 56 MHz 0.73 DMIPS/MHz |

Acorn A7000+ Network Computer | ||

| ARM7TDMI | ARMv4T | ARM7TDMI(-S) | Segmentación de 3 etapas, Thumb | nulo | 15 MIPS @ 16.8 MHz 63 DMIPS @ 70 MHz |

Game Boy Advance, Nintendo DS, Apple iPod, Lego NXT, Atmel AT91SAM7, Juice Box, NXP Semiconductors LPC2000 and LH754xx, Actel's CoreMP7 Archivado el 18 de julio de 2011 en Wayback Machine. |

| ARM710T | ARM7TDMI, caché | 8 KB unificados, MMU | 36 MIPS @ 40 MHz | Psion Series 5mx, Psion Revo/Revo Plus/Diamond Mako | ||

| ARM720T | ARM7TDMI, caché | 8 KB unificados, MMU con FCSE | 60 MIPS @ 59.8 MHz | Zipit Wireless Messenger, NXP Semiconductors LH7952x | ||

| ARM740T | ARM7TDMI, caché | MPU | ||||

| ARMv5TEJ | ARM7EJ-S | Segmentación de 5 etapas, Thumb, Jazelle DBX, mejora de instrucciones DSP | nulo | |||

| StrongARM | ARMv4 | SA-110 | 16 KB/16 KB, MMU | 203 MHz 1.0 DMIPS/MHz |

Apple Newton serie 2x00, Acorn Risc PC, Rebel/Corel Netwinder, Chalice CATS | |

| SA-1100 | SA-110, SoC integrado | 16 KB/8 KB, MMU | 203 MHz | Psion netBook | ||

| SA-1110 | SA-110, SoC integrado | 16 KB/8 KB, MMU | 206 MHz | LART (computer), Intel Assabet, Ipaq H36x0, Balloon2, Zaurus SL-5x00, HP Jornada 7xx, Jornada 560 series, Palm Zire 31 | ||

| ARM8 | ARMv4 | ARM810[5] | Segmentación de 5 fases, predilección de salto estático, memoria de doble ancho de banda | 8 KB unificados, MMU | 84 MIPS @ 72 MHz 1.16 DMIPS/MHz |

Acorn Risc PC prototipo de CPU card |

| ARM9TDMI | ARMv4T | ARM9TDMI | Segmentación de 5 fases, Thumb | nulo | ||

| ARM920T | ARM9TDMI, caché | 16 KB/16 KB, MMU con FCSE (Fast Context Switch Extension)[6] | 200 MIPS @ 180 MHz | Armadillo, Atmel AT91SAM9, GP32, GP2X (primer núcleo), Tapwave Zodiac (Motorola i. MX1), Hewlett-Packard Calculadoras HP-49/50, Sun SPOT, Cirrus Logic EP9302, EP9307, EP9312, EP9315, Samsung S3C2442 (HTC TyTN, FIC Neo FreeRunner[7]), Samsung S3C2410 (Dispositivos de navegación TomTom)[8] | ||

| ARM922T | ARM9TDMI, cachés | 8 KB/8 KB, MMU | NXP Semiconductors LH7A40x | |||

| ARM940T | ARM9TDMI, cachés | 4 KB/4 KB, MPU | GP2X (segundo núcleo), Meizu M6 Mini Player[9][10] | |||

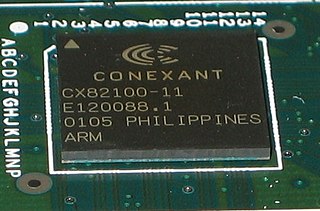

| ARM9E | ARMv5TE | ARM946E-S | Thumb, mejora de instrucciones DSP, caché | variables, memoria estrechamente acoplada, MPU | Nintendo DS, Nokia N-Gage, Canon PowerShot A470, Canon EOS 5D Mark II,[11] Conexant 802.11 chips, Samsung S5L2010 | |

| ARM966E-S | Thumb, Mejora de instrucciones DSP | sin caché, TCMs | ST Micro STR91xF, integra Ethernet[12] | |||

| ARM968E-S | ARM966E-S | sin caché, TCMs | NXP Semiconductors LPC2900 | |||

| ARMv5TEJ | ARM926EJ-S | Thumb, Jazelle DBX, Mejora de instrucciones DSP | variables, TCMs, MMU | 220 MIPS @ 200 MHz, | Teléfonos móviles: Sony Ericsson (K, W series); Siemens y Benq (serie x65 y posterior); LG Arena; Texas Instruments OMAP1710, OMAP1610, OMAP1611, OMAP1612, OMAP-L137, OMAP-L138; Qualcomm MSM6100, MSM6125, MSM6225, MSM6245, MSM6250, MSM6255A, MSM6260, MSM6275, MSM6280, MSM6300, MSM6500, MSM6800; Freescale i.MX21, i.MX27, Atmel AT91SAM9, NXP Semiconductors LPC3000, GPH Wiz, NEC C10046F5-211-PN2-A SoC – núcleo en la ATi Hollywood GPU usada en la Wii,[13] Samsung S3C2412 usado en Squeezebox Duet's Controller. Squeezebox Radio; NeoMagic MiMagic Family MM6, MM6+, MM8, MTV; Buffalo TeraStation Live (NAS); Telechips TCC7801, TCC7901;ZiiLABS' ZMS-05 SoC; Western Digital MyBook "I World Edition"; Rockchip RK2806 y RK2808. | |

| ARMv5TE | ARM996HS | Procesador sin reloj, como ARM966E-S | sin cachés, TCMs, MPU | |||

| ARM10E | ARMv5TE | ARM1020E | Segmentación de 6 fases, Thumb, Mejora de instrucciones DSP, (VFP) | 32 KB/32 KB, MMU | ||

| ARM1022E | ARM1020E | 16 KB/16 KB, MMU | ||||

| ARMv5TEJ | ARM1026EJ-S | Thumb, Jazelle DBX, Mejora de instrucciones DSP, (VFP) | variable, MMU o MPU | Western Digital MyBook "II World Edition";Conexant so4610 y so4615 ADSL SoC | ||

| XScale | ARMv5TE | 80200/IOP310/IOP315 | Procesador E/S, Thumb, Mejora de instrucciones DSP | |||

| 80219 | 400/600 MHz | Thecus N2100 | ||||

| IOP321 | 600 BogoMips @ 600 MHz | Iyonix | ||||

| IOP33x | ||||||

| IOP34x | 1–2 núcleos, Acelerador de RAID | 32K/32K L1, 512K L2, MMU | ||||

| PXA210/PXA250 | Procesador de aplicaciones, Segmentación de 7 fases | PXA210: 133 y 200 MHz, PXA250: 200, 300, and 400 MHz | Zaurus SL-5600, iPAQ H3900, Sony CLIÉ NX60, NX70V, NZ90 | |||

| PXA255 | 32KB/32KB, MMU | 400 BogoMips @ 400 MHz; 371–533 MIPS @ 400 MHz[14] | Gumstix basix & connex, Palm Tungsten E2, Zaurus SL-C860, Mentor Ranger & Stryder, iRex ILiad | |||

| PXA263 | 200, 300 y 400 MHz | Sony CLIÉ NX73V, NX80V | ||||

| PXA26x | default 400 MHz, más de 624 MHz | Palm Tungsten T3 | ||||

| PXA27x | Procesador de Aplicaciones | 32 KB/32 KB, MMU | 800 MIPS @ 624 MHz | Gumstix verdex,"Trizeps-Modules" PXA270 COM, HTC Universal, HP hx4700, Zaurus SL-C1000, 3000, 3100, 3200, Dell Axim x30, x50, and x51 series, Motorola Q, Balloon3, Trolltech Greenphone, Palm TX(312MHz), Motorola Ezx Platform A728, A780, A910, A1200, E680, E680i, E680g, E690, E895, Rokr E2, Rokr E6, Fujitsu Palm Zire 72 (PXA270), Siemens LOOX N560, Toshiba Portégé G500, Trēo 650-755p, Zipit Z2, HP iPaq 614c Business Navigator. | ||

| PXA800(E)F | ||||||

| PXA3XX (nombre en clave "Monahans") | 32KB/32KB L1, TCM, MMU | 1000 MIPS @ 1.25 GHz | Samsung Omnia | |||

| PXA900 | Blackberry 8700, Blackberry Pearl (8100) | |||||

| IXC1100 | Procesador de control de vuelo | |||||

| IXP2400/IXP2800 | ||||||

| IXP2850 | ||||||

| IXP2325/IXP2350 | ||||||

| IXP42x | NSLU2 IXP460/IXP465 | |||||

| ARM11 | ARMv6 | ARM1136J(F)-S[15] | Segmentación de 8 etapas, SIMD, Thumb, Jazelle DBX, (VFP), Mejora de instrucciones DSP | variable, MMU | 740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz | Texas Instruments OMAP2420 (Nokia E90, Nokia N93, Nokia N95, Nokia N82), Zune, BUGbase, Nokia N800, Nokia 500, Nokia N810, Qualcomm MSM7200 (con coprocesador ARM926EJ-S@274 MHz, usado en Eten Glofiish, HTC TyTN II, HTC Nike), Freescale i.MX31 (del Zune original de 30 GB, Toshiba Gigabeat S y Kindle DX), Freescale MXC300-30 (Nokia E63, Nokia E71, Nokia 5800, Nokia E51, Nokia 6700 Classic, Nokia 6120 Classic, Nokia 6210 Navigator, Nokia 6220 Classic, Nokia 6290, Nokia 6710 Navigator, Nokia 6720 Classic, Nokia E75, Nokia N97, Nokia N81), Qualcomm MSM7201A visto en los HTC Dream, HTC Magic, Motorola Z6, HTC Hero, & Samsung SGH-i627 (Propel Pro), Qualcomm MSM7227 usado en ZTE Link,[16][17] |

| ARMv6T2 | ARM1156T2(F)-S | Segmentación de 9 etapas, SIMD, Thumb-2, (VFP), Mejora de instrucciones DSP | variable, MPU | |||

| ARMv6KZ | ARM1176JZ(F)-S | ARM1136EJ(F)-S | variable, MMU+TrustZone | Apple iPhone (EDGE y 3G), Apple iPod touch (1.ª y 2.ª generación), Conexant CX2427X, Motorola RIZR Z8, Motorola RIZR Z10, NVIDIA GoForce 6100;[18] Telechips TCC9101, TCC9201, TCC8900, Fujitsu MB86H60, Samsung S3C6410 (ej. Samsung Omnia II, Samsung Moment, SmartQ 5), S3C6430,[19] Raspberry Pi | ||

| ARMv6K | ARM11 MPCore | As ARM1136EJ(F)-S, 1–4 core SMP | variable, MMU | Nvidia APX 2500, Familia Nintendo 3DS | ||

| Familia | Versión de arquitectura | Núcleo | Características | Caché (I/D)/MMU | MIPS efectivos @ MHz | Campo de aplicación |

| Cortex | ARMv7-A | Cortex-A5 | VFP, NEON, Jazelle RCT and DBX, Thumb-2, Segmentación de 8 fases, 1–4 núcleos SMP | variable (L1), MMU+TrustZone | Más de 1500 (1.5 DMIPS/MHz) | "Sparrow" (nombre en clave)[20][21][22] |

| Cortex-A8 | VFP, NEON, Jazelle RCT, Thumb-2, Segmentación Superscalar de 13 etapas | variable (L1+L2), MMU+TrustZone | Más de 2000 (2.0 DMIPS/MHz de reloj desde 600 MHz hasta más de 1 GHz) | Texas Instruments serie OMAP3xxx, SBM7000, Oregon State University OSWALD, Gumstix Overo Earth, Pandora, Apple iPhone 3GS, Apple iPod touch (3rd Generation), Apple iPad (SoCApple A4), Apple iPhone 4 (Soc Apple A4, fabricado por Samsung e Intrensity), Archos 5, FreeScale i.MX51-SOC, BeagleBoard, Motorola Milestone, Motorola Milestone X, Palm Pre, Samsung Omnia HD, Samsung Wave S8500 (Hummingbird), Samsung i9000 Galaxy S (Hummingbird), Sony Ericsson Satio, Touch Book, Nokia N900, Meizu M9, ZiiLABS ZMS-08 SoC. | ||

| Qualcomm Scorpion | GPU Adreno 200, VFPv3, NEON, Jazelle RCT, Thumb-2, Segmentación Superscalar de 13 etapas, | variable (L1+L2), MMU+TrustZone | Más de 2000 (2.0 DMIPS/MHz de reloj desde 1 GHz hasta más de 1,5 GHz dual core) | Toshiba TG01, HTC Desire, Google Nexus One, HTC EVO 4G, HTC Incredible, HTC Scorpion, HTC HD2, HTC HD7 Sony Ericsson Xperia ARC/ARC S | ||

| Cortex-A9 | Perfil de aplicaciones, (VFP), (NEON), Jazelle RCT y DBX, Thumb-2, Out-of-order speculative issue superscalar | MMU+TrustZone | 2.5 DMIPS/MHz | Acer Iconia A200, Galaxy Nexus, Motorola RAZR | ||

| Cortex-A9 MPCore | Cortex-A9, 1–4 núcleos SMP | MMU+TrustZone | 10,000 DMIPS @ 2 GHz optimizados en TSMC 40G (Doble núcleo) (2.5 DMIPS/MHz por núcleo) | Texas Instruments OMAP4430/4440, ST-Ericsson U8500, Nvidia Tegra2, Qualcomm Snapdragon 8X72 PlayStation Vita, Samsung Galaxy S II (Exynos 4210), Samsung Galaxy S III (Exynos 4212) | ||

| ARMv7-R | Cortex-R4(F) | Perfil Embebido, Thumb-2, (FPU) | variable caché, MPU opcional | 600 DMIPS @ 475 MHz | Broadcom, TMS570 from Texas Instruments | |

| ARMv7-ME | Cortex-M4 (nombre en clave "Merlin")[23] | Perfil microcontrolador, Thumb y Thumb-2, FPU. MAC, SIMD e instrucciones divididas. | MPU opcional. | 1.25 DMIPS/MHz | ||

| ARMv7-M | Cortex-M3 | Perfil microcontrolador, Thumb-2 únicamente. Reparto de instrucciones por Hardware. | sin caché, MPU opcional. | 125 DMIPS @ 100 MHz | Texas Instruments Stellaris microcontroller family, ST Microelectronics STM32, NXP Semiconductors LPC1700, Toshiba TMPM330FDFG Archivado el 14 de junio de 2011 en Wayback Machine., Ember's EM3xx Series, Atmel AT91SAM3, Europe Technologies EasyBCU, Energy Micro's EFM32, Actel's SmartFusion Archivado el 18 de junio de 2013 en Wayback Machine. | |

| ARMv6-M | Cortex-M0 (nombre en clave "Swift")[24] | Perfil microcontrolador, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | Sin caché. | 0.9 DMIPS/MHz | NXP Semiconductors NXP LPC1100,[25] Triad Semiconductor,[26] Melfas,[27] Chungbuk Technopark,[28] Nuvoton,[29] austriamicrosystems,[30] Rohm[31] | |

| Cortex-M1 | FPGA targeted, Microcontroller profile, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | Sin | Más de 136 DMIPS @ 170 MHz[32] (0.8 DMIPS/MHz,[33] MHz achievable FPGA-dependent) | Actel ProASIC3, ProASIC3L, IGLOO and Fusion PSC devices Archivado el 7 de julio de 2011 en Wayback Machine., Altera Cyclone III, otros productos FPGA están soportados, por ejemplo: Synplicity | ||

| Familia | Versión de Arquitectura | Núcleo | Características | Caché (I/D)/MMU | MIPS efectivos @ MHz | Campo de Aplicación |

Diseño

Resumir

Contexto

El juego de instrucciones del ARM es similar al del MOS 6502, pero incluye características adicionales que le permiten conseguir un mejor rendimiento en su ejecución. Para mantener el concepto tradicional de RISC, se estableció la ejecución de una orden a la vez, por lo general, de un ciclo. La característica más interesante es el uso de los 4 bits superiores como código de condición, haciendo que cualquier instrucción pueda ser condicional. Este corte reduce el espacio para algunos desplazamientos en el acceso a la memoria, pero permite evitar perder ciclos de reloj en el pipeline al ejecutar pequeños trozos de código con ejecución condicional. El ejemplo típico es el Máximo común divisor, según el algoritmo de Euclides.

Ejemplo en C:

while (i != j) // Ingresa en el ciclo cuando i<j o i>j, no cuando i==j

{

if (i > j) // Cuando i>j realiza lo siguiente

i -= j;

else // en otro caso, realiza lo siguiente

j -= i;

}

En cambio con código ensamblador ARM, el ciclo puede hacerse más eficiente haciendo:

loop:

// Compara i y j

GT = i > j;

LT = i < j;

NE = i != j;

// Operaciones mejoradas usando resultados de flags

if(GT) i -= j; // Sustrae *solo* si es mayor

if(LT) j -= i; // Sustrae *solo* si es menor

if(NE) goto loop; // Ciclo *solo* si los valores comparados no son iguales

y esto se codifica como:

loop: CMP Ri, Rj ; establece la condicion "NE" if (i != j),

; "GT" si (i > j),

; o "LT" si (i < j)

SUBGT Ri, Ri, Rj ; si "GT" (Mayor que), i = i-j;

SUBLT Rj, Rj, Ri ; si "LT" (Menor que), j = j-i;

BNE loop ; si "NE" (No igual), entonces realiza el ciclo

Otra característica única del juego de instrucciones es la posibilidad de añadir shifts y rotar en el procesamiento de datos (aritmético, lógico y movimiento de registros), por ejemplo, la instrucción en C "a += (j << 2);" puede ser mejorada como una única instrucción en el ARM, permitiendo la reubicación del registro.

Todo esto ocasiona que se necesiten menos operaciones de carga y almacenamiento, mejorando el rendimiento.

El procesador ARM también tiene algunas características poco comunes en otras arquitecturas también consideradas RISC, como el direccionamiento relativo, y el pre y post incremento en el modo de direccionamiento.

Tiene dos modos de funcionamiento: el ARMI con instrucciones que ocupan 4 bytes, más rápidas y potentes (hay instrucciones que sólo están en este modo) pero con mayor consumo de memoria y de electricidad. Y el modo THUMB, más limitado, con instrucciones que ocupan 2 bytes y con menor consumo de corriente.

Registros

La familia ARM dispone de 16 registros (utilizables por el programador) de 32 bits, que se designan desde R0 a R15. En principio son todos idénticos y sólo 3 tienen funciones específicas que son el R15 (se emplea como contador de programa o PC), y el R14 (utilizado para almacenar la dirección de retorno cuando se llama a una subrutina o se genera una excepción) y el R13 (stack Pointer).

Ventajas

- Amplio abanico de fabricantes: Como se ha comentado antes, ARM permite la compra a terceros de su licencia, dando lugar a un gran número de marcas productoras de esta arquitectura, cada cual, ofreciendo nuevas mejoras, avances, y, en general, un mayor abanico de opciones para el consumidor.

- Simpleza de instrucciones: Nos encontramos con un set de instrucciones mucho más pequeño, pero mucho más atómico; esto quiere decir que las instrucciones se pueden cambiar prácticamente por instrucciones de tipo máquina, ahorrando tanto tiempo como energía en su traducción.

- Bajo uso energético: Nos encontramos con RISC, y su "simpleza". Estos buscan la mayor eficiencia por ciclo; además, dan lugar a chips más pequeños y simples y, por tanto, a una mejora considerable en cuanto a eficiencia energética.

- Rendimiento aceptable y en mejora: Como se ha dicho anteriormente, la compra de terceros ofrece nuevas mejoras y avances en el rendimiento.

Tecnologías

Resumir

Contexto

Thumb

Los procesadores más recientes traen un conjunto de instrucciones adicional llamado Thumb, de 16 bits (2 bytes) de longitud por instrucción, en lugar de 32 bits (4 bytes) como el juego estándar de ARM. Thumb es un subconjunto formado por las instrucciones que se usan con más frecuencia. Al tener la mitad de longitud, se consigue disminuir la cantidad de código y mejorar su densidad. El rendimiento puede ser superior a un código de 32 bits en donde el puerto de memoria o ancho del bus de comunicaciones son menores a 32 bits. Por lo general, en las aplicaciones se inserta un pequeño rango de direcciones de memoria con un datapath de 32 bits (por ejemplo: Game Boy Advance), y el resto son 16 bits en modo wide o narrower.

El primer procesador con la tecnología Thumb fue el ARM7TDMI. Toda la familia posterior al ARM9, incluyendo el procesador Intel XScale, tienen incorporada la tecnología en su núcleo.

Jazelle

ARM tiene implementada una tecnología que permite que ciertos tipos de arquitecturas ejecuten Java bytecode nativamente en el hardware. El primer procesador en usar Jazelle fue el ARM926EJ-S, siendo denominados con una J a todos los procesadores que soportaran esta tecnología.

Sistemas operativos

Resumir

Contexto

Acorn systems

El primer ordenador personal basado en ARM es el Acorn Archimedes que ejecutaba un sistema operativo provisional llamado Arthur, que se convirtió en RISC OS, utilizado en posteriores modelos de Acorn y otros vendedores.

Sistemas operativos integrados

La arquitectura ARM está soportada por un gran número de sistemas operativos integrados y de tiempo real, incluyendo Android, Windows 11, Windows 10, macOS, iOS, Windows CE, Windows 8 RT, .NET Micro Framework, Symbian, ChibiOS/RT, FreeRTOS, eCos, Integrity, Nucleus PLUS, MicroC/OS-II, QNX, RTEMS, BRTOS, RTXC Quadros, ThreadX, Unison Operating System, uTasker, VxWorks, MQX y OSE.[37]

UNIX

Los sistemas que acreditan la especificación estándar UNIX y que soportan la arquitectura ARM son:

Tipo UNIX

Las variantes de UNIX soportadas son:

Linux

Las siguientes distribuciones Linux soportan los procesadores ARM:

BSD

Los siguientes sistemas BSD soportan los procesadores ARM:

Windows

Microsoft anunció el 5 de enero de 2011 que la próxima gran versión de la familia Windows NT (hoy Windows 8)[41] incluye soporte para procesadores ARM. Microsoft mostró una versión preliminar de Windows (versión 6.2.7867) que se ejecuta en un equipo basado en ARM en el Consumer Electronics Show 2011.[42] La arquitectura ARM también es soportada por los sistemas operativos móviles de Microsoft, Windows Phone y Windows Mobile. ARM también es compatible con Windows Embedded CE que ahora se llama Windows Embedded Compact. Esta última versión soporta ARM 5,6 y 7. Windows CE 5 es el sistema operativo subyacente para Windows Mobile y Windows Embedded Compact 7 es el sistema operativo subyacente para Windows Phone 7. El pequeño Microsoft OS.NET Microframework utiliza exclusivamente ARM.

El 29 de octubre de 2012 salió a la venta la tableta Surface de Microsoft la cual tiene un procesador ARM y utiliza como sistema operativo Windows 8 RT, versión que no se puede descargar ni comprar ya que viene instalada en tabletas con arquitectura ARM. Hay otra versión de Windows 8 distinta a esta que es el Windows 8 PRO para computadoras x86.

Las últimas versiones de Windows, 10 y 11, ya disponen de soporte para arquitectura ARM, pero no se dispone de ninguna herramienta para el uso de programas x86 en arquitectura ARM, por lo que el soporte de ARM no es completo.[43]

iOS y macOS

Desde el desarrollo del iPhone en 2007, Apple ha utilizado procesadores ARM para sus plataformas de telefonía móvil (iPhone), relojes inteligentes (Apple Watch), tabletas (iPad), reproductores en streaming(Apple Tv) y más recientemente en todos sus ordenadores(iMac, MacBook, Mac Mini y Mac Pro). Apple optó por procesadores ARM para estas plataformas debido a la ventaja que ofrecen por su bajo consumo de energía y poca refrigeración necesaria.

También el ARM acabó con los famosos Hackintosh , ganando la batalla contra la piratería por el momento.

Véase también

Referencias

Enlaces externos

Wikiwand - on

Seamless Wikipedia browsing. On steroids.