Top Qs

Timeline

Chat

Perspective

Random-access memory

Form of computer data storage From Wikipedia, the free encyclopedia

Remove ads

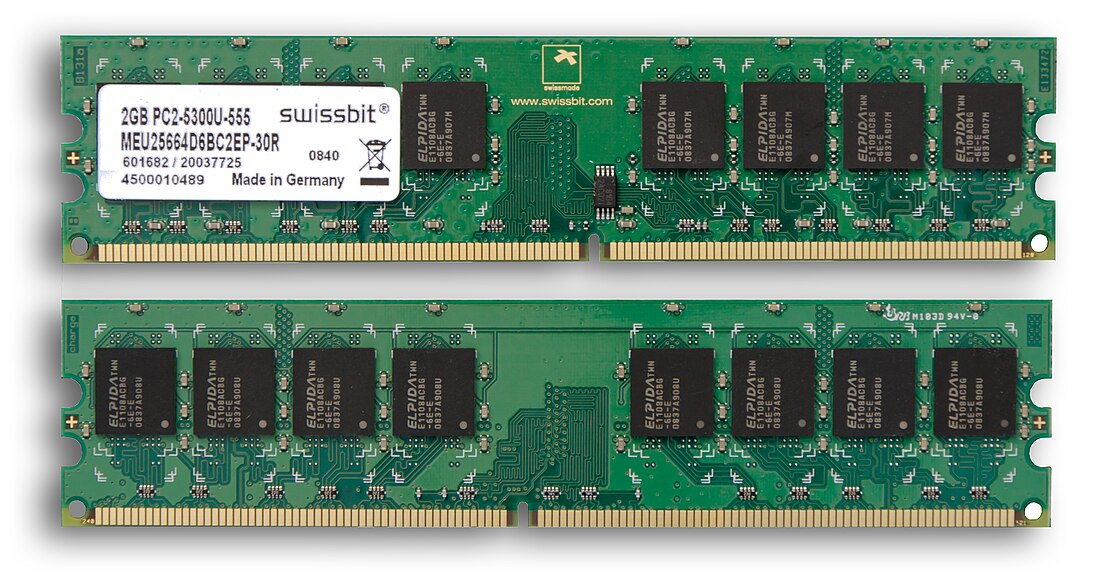

Random-access memory (RAM; /ræm/) is a form of electronic computer memory that can be read and changed in any order, typically used to store working data and machine code.[1][2] A random-access memory device allows data items to be read or written in almost the same amount of time irrespective of the physical location of data inside the memory, in contrast with other direct-access data storage media (such as hard disks and magnetic tape), where the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement.

In modern technology, random-access memory takes the form of integrated circuit (IC) chips with MOS (metal–oxide–semiconductor) memory cells. RAM is normally associated with volatile types of memory where stored information is lost if power is removed. The two main types of volatile random-access semiconductor memory are static random-access memory (SRAM) and dynamic random-access memory (DRAM).

Non-volatile RAM has also been developed[3] and other types of non-volatile memories allow random access for read operations, but either do not allow write operations or have other kinds of limitations. These include most types of ROM and NOR flash memory.

The use of semiconductor RAM dates back to 1965 when IBM introduced the monolithic (single-chip) 16-bit SP95 SRAM chip for their System/360 Model 95 computer, and Toshiba used bipolar DRAM memory cells for its 180-bit Toscal BC-1411 electronic calculator, both based on bipolar transistors. While it offered higher speeds than magnetic-core memory, bipolar DRAM could not compete with the lower price of the then-dominant magnetic-core memory.[4] In 1966, Dr. Robert Dennard invented modern DRAM architecture in which there's a single MOS transistor per capacitor.[5] The first commercial DRAM IC chip, the 1K Intel 1103, was introduced in October 1970. Synchronous dynamic random-access memory (SDRAM) was reintroduced with the Samsung KM48SL2000 chip in 1992.

Remove ads

History

Summarize

Perspective

Early computers used relays, mechanical counters[6] or delay lines for main memory functions. Ultrasonic delay lines were serial devices which could only reproduce data in the order it was written. Drum memory could be expanded at relatively low cost but efficient retrieval of memory items requires knowledge of the physical layout of the drum to optimize speed. Latches built out of triode vacuum tubes, and later, out of discrete transistors, were used for smaller and faster memories such as registers. Such registers were relatively large and too costly to use for large amounts of data; generally, only a few dozen or few hundred bits of such memory could be provided.

The first practical form of random-access memory was the Williams tube. It stored data as electrically charged spots on the face of a cathode-ray tube. Since the electron beam of the CRT could read and write the spots on the tube in any order, memory was random access. The capacity of the Williams tube was a few hundred to around a thousand bits, but it was much smaller, faster, and more power-efficient than using individual vacuum tube latches. Developed at the University of Manchester in England, the Williams tube provided the medium on which the first electronically stored program was implemented in the Manchester Baby computer, which first successfully ran a program on 21 June, 1948.[7] In fact, rather than the Williams tube memory being designed for the Baby, the Baby was a testbed to demonstrate the reliability of the memory.[8][9]

Magnetic-core memory was invented in 1947 and developed up until the mid-1970s. It became a widespread form of random-access memory, relying on an array of magnetized rings. By changing the sense of each ring's magnetization, data could be stored with one bit stored per ring. Since every ring had a combination of address wires to select and read or write it, access to any memory location in any sequence was possible. Magnetic core memory was the standard form of computer memory until displaced by semiconductor memory in integrated circuits (ICs) during the early 1970s.[10]

Prior to the development of integrated read-only memory (ROM) circuits, permanent (or read-only) random-access memory was often constructed using diode matrices driven by address decoders, or specially wound core rope memory planes.[citation needed]

Semiconductor memory appeared in the 1960s with bipolar memory, which used bipolar transistors. Although it was faster, it could not compete with the lower price of magnetic core memory.[11]

MOS RAM

In 1957, Frosch and Derick manufactured the first silicon dioxide field-effect transistors at Bell Labs, the first transistors in which drain and source were adjacent at the surface.[12] Subsequently, in 1960, a team demonstrated a working MOSFET at Bell Labs.[13][14] This led to the development of metal–oxide–semiconductor (MOS) memory by John Schmidt at Fairchild Semiconductor in 1964.[10][15] In addition to higher speeds, MOS semiconductor memory was cheaper and consumed less power than magnetic core memory.[10] The development of silicon-gate MOS integrated circuit (MOS IC) technology by Federico Faggin at Fairchild in 1968 enabled the production of MOS memory chips.[16] MOS memory overtook magnetic core memory as the dominant memory technology in the early 1970s.[10]

Integrated bipolar static random-access memory (SRAM) was invented by Robert H. Norman at Fairchild Semiconductor in 1963.[17] It was followed by the development of MOS SRAM by John Schmidt at Fairchild in 1964.[10] SRAM became an alternative to magnetic-core memory, but required six MOS transistors for each bit of data.[18] Commercial use of SRAM began in 1965, when IBM introduced the SP95 memory chip for the System/360 Model 95.[11]

Dynamic random-access memory (DRAM) allowed replacement of a 4- or 6-transistor latch circuit by a single transistor for each memory bit, greatly increasing memory density at the cost of volatility. Data was stored in the tiny capacitance of each transistor and had to be periodically refreshed every few milliseconds before the charge could leak away.

Toshiba's Toscal BC-1411 electronic calculator, which was introduced in 1965,[19][20][21] used a form of capacitor bipolar DRAM, storing 180-bit data on discrete memory cells, consisting of germanium bipolar transistors and capacitors.[20][21] Capacitors had also been used for earlier memory schemes, such as the drum of the Atanasoff–Berry Computer, the Williams tube and the Selectron tube. While it offered higher speeds than magnetic-core memory, bipolar DRAM could not compete with the lower price of the then-dominant magnetic-core memory.[22]

In 1966, Robert Dennard, while examining the characteristics of MOS technology, found it was capable of building capacitors, and that storing a charge or no charge on the MOS capacitor could represent the 1 and 0 of a bit, and the MOS transistor could control writing the charge to the capacitor. This led to his development of modern DRAM architecture for which there is a single MOS transistor per capacitor.[18] In 1967, Dennard filed a patent under IBM for a single-transistor DRAM memory cell, based on MOS technology.[18][23] The first commercial DRAM IC chip was the Intel 1103, which was manufactured on an 8 μm MOS process with a capacity of 1 kbit, and was released in 1970.[10][24][25]

The earliest DRAMs were often synchronized with the CPU clock and were used with early microprocessors. In the mid-1970s, DRAMs moved to the asynchronous design, but in the 1990s returned to synchronous operation.[26][27] In 1992 Samsung released KM48SL2000, which had a capacity of 16 Mbit.[28][29] The first commercial double data rate SDRAM was Samsung's 64 Mbit DDR SDRAM, released in June 1998.[30] GDDR (graphics DDR) is a form of SGRAM (synchronous graphics RAM), which was first released by Samsung as a 16 Mbit memory chip in 1998.[31]

Remove ads

Types

Summarize

Perspective

In general, the term RAM refers solely to solid-state memory devices, and more specifically the main memory in most computers. The two widely used forms of modern RAM are static RAM (SRAM) and dynamic RAM (DRAM). In SRAM, a bit of data is stored using the state of a memory cell, typically using six MOSFETs. This form of RAM is more expensive to produce, but is generally faster and requires less static power than DRAM. In modern computers, SRAM is often used as cache memory for the CPU. DRAM stores a bit of data using a transistor and capacitor pair (typically a MOSFET and MOS capacitor, respectively),[32] which together comprise a DRAM cell. The capacitor holds a high or low charge (1 or 0, respectively), and the transistor acts as a switch that lets the control circuitry on the chip read the capacitor's state of charge or change it. As this form of memory is less expensive to produce than static RAM, it is the predominant form of computer memory used in modern computers.

Both static and dynamic RAM are considered volatile, as their state is lost when power is removed from the system. By contrast, read-only memory (ROM) stores data by permanently enabling or disabling selected transistors, such that the memory cannot be altered. Writable variants of ROM (such as EEPROM and NOR flash) share properties of both ROM and RAM, enabling data to persist without power and to be updated without requiring special equipment.

ECC memory (which can be either SRAM or DRAM) includes special circuitry to detect and/or correct random faults (memory errors) in the stored data, using parity bits or error correction codes.

Remove ads

Memory cell

The memory cell is the fundamental building block of computer memory. The memory cell is an electronic circuit that stores one bit of binary information. The cell can be set to store a logic 1 (high voltage level) and reset to store a logic 0 (low voltage level). Its value is maintained until it is changed by the set/reset process. The value in the memory cell can be accessed by reading it.

In SRAM, the memory cell is a type of flip-flop circuit, usually implemented using FETs. This means that SRAM requires very low power when not being accessed, but it is complex, expensive and has low storage density.

A second type, DRAM, is based around a capacitor. Charging and discharging this capacitor can store a 1 or a 0 in the cell. However, the charge in this capacitor slowly leaks away and must be refreshed periodically. Because of this refresh process, DRAM uses more power, but it can achieve greater storage densities and lower unit costs compared to SRAM.

|  |

Addressing

Summarize

Perspective

To be useful, memory cells must be readable and writable. Within the RAM device, multiplexing and demultiplexing circuitry is used to select memory cells. Typically, a RAM device has a set of address lines , and for each combination of bits that may be applied to these lines, a set of memory cells are selected. Due to this addressing, RAM devices virtually always have a memory capacity that is a power of two.

Usually, several memory cells share the same address. For example, a 4-bit-wide RAM chip has four memory cells for each address. Often the width of the memory and that of the microprocessor are different; For a 32-bit microprocessor, eight 4-bit RAM chips would be needed.

Often, more addresses are needed than can be provided by a single device. In that case, multiple devices are used, with external multiplexors used to select the device assigned to a specific address range. RAM is often byte addressable, although word-addressable RAM also exists.[33][34]

Remove ads

Memory hierarchy

Many computer systems have a memory hierarchy consisting of processor registers, on-die SRAM caches, external caches, DRAM, memory paging systems and virtual memory or swap space on a hard drive. This entire pool of memory may be referred to as RAM from a programming perspective. The overall goal of using a memory hierarchy is to obtain the fastest possible average access time while minimizing the total cost of the entire memory system.

Remove ads

Other uses of RAM

Summarize

Perspective

In addition to serving as temporary storage and working space for the operating system and applications, RAM is used in numerous other ways.

Virtual memory

Most modern operating systems employ a method of extending RAM capacity, known as "virtual memory". A portion of the computer's hard drive is set aside for a paging file or a scratch partition, and the combination of physical RAM and the paging file form the system's total memory. (For example, if a computer has 2 GB (10243 B) of RAM and a 1 GB page file, the operating system has 3 GB total memory available to it.) When the system runs low on physical memory, it can "swap" portions of RAM to the paging file to make room for new data, as well as to read previously swapped information back into RAM. Excessive use of this mechanism results in thrashing and generally hampers overall system performance, mainly because hard drives are far slower than RAM.

RAM disk

Software can "partition" a portion of a computer's RAM, allowing it to act as a much faster hard drive that is called a RAM disk. A RAM disk loses the stored data when the computer is shut down, unless memory is arranged to have a standby battery source, or changes to the RAM disk are written out to a nonvolatile disk. The RAM disk is reloaded from the physical disk upon RAM disk initialization.

Shadow RAM

Sometimes, the contents of a relatively slow ROM chip are copied to read/write memory to allow for shorter access times. The ROM chip is then disabled while the initialized memory locations are switched in on the same block of addresses (often write-protected). This process, sometimes called shadowing, is fairly common in both computers and embedded systems.

As a common example, the BIOS in typical personal computers often has an option called "use shadow BIOS" or similar. When enabled, functions that rely on data from the BIOS's ROM instead use DRAM locations (most can also toggle shadowing of video card ROM or other ROM sections). Depending on the system, this may not result in increased performance, and may cause incompatibilities. For example, some hardware may be inaccessible to the operating system if shadow RAM is used. On some systems the benefit may be hypothetical because the BIOS is not used after booting in favor of direct hardware access. Free memory is reduced by the size of the shadowed ROMs.[35]

Virtual private networks

Some virtual private network services utilize RAM servers to keep all runtime state including session metadata and cryptographic material in volatile memory so that a power cycle or reboot clears it, reducing persistent forensic artifacts relative to disk-backed designs.[36][37] In such a design, no data is written to hard drives; all information resides in volatile memory and is erased whenever the server is powered off or rebooted.[38]

Remove ads

Memory wall

Summarize

Perspective

The memory wall is the growing disparity of speed between CPU and the response time of memory (known as memory latency) outside the CPU chip. An important reason for this disparity is the limited communication bandwidth beyond chip boundaries. From 1986 to 2000, CPU speed improved at an annual rate of 55% while off-chip memory response time only improved at 10%. Given these trends, it was expected that memory latency would become an overwhelming bottleneck in computer performance.[39]

Another reason for the disparity is the enormous increase in the size of memory since the start of the PC revolution in the 1980s. Originally, PCs contained less than 1 mebibyte of RAM, which often had a response time of 1 CPU clock cycle, meaning that it required 0 wait states. Larger memory units are inherently slower than smaller ones of the same type, simply because it takes longer for signals to traverse a larger circuit. Constructing a memory unit of many gibibytes with a response time of one clock cycle is difficult or impossible. Modern CPUs often still have a mebibyte of 0 wait state cache memory, but it resides on the same chip as the CPU cores due to the bandwidth limitations of chip-to-chip communication. It must also be constructed from static RAM, which is far more expensive than the dynamic RAM used for larger memories. Static RAM also consumes far more power.

CPU speed improvements slowed significantly partly due to major physical barriers and partly because CPU designs have already hit the memory wall in some sense. Intel summarized these causes in a 2005 document.[40]

First of all, as chip geometries shrink and clock frequencies rise, the transistor leakage current increases, leading to excess power consumption and heat... Secondly, the advantages of higher clock speeds are in part negated by memory latency, since memory access times have not been able to keep pace with increasing clock frequencies. Third, for certain applications, traditional serial architectures are becoming less efficient as processors get faster (due to the so-called von Neumann bottleneck), further undercutting any gains that frequency increases might otherwise buy. In addition, partly due to limitations in the means of producing inductance within solid state devices, resistance-capacitance (RC) delays in signal transmission are growing as feature sizes shrink, imposing an additional bottleneck that frequency increases don't address.

The RC delays in signal transmission were also noted in "Clock Rate versus IPC: The End of the Road for Conventional Microarchitectures"[41] which projected a maximum of 12.5% average annual CPU performance improvement between 2000 and 2014.

A different concept is the processor-memory performance gap, which can be addressed by 3D integrated circuits that reduce the distance between the logic and memory aspects that are further apart in a 2D chip.[42] Memory subsystem design requires a focus on the gap, which is widening over time.[43] The main method of bridging the gap is the use of caches; small amounts of high-speed memory that houses recent operations and instructions nearby the processor, speeding up the execution of those operations or instructions in cases where they are called upon frequently. Multiple levels of caching have been developed to deal with the widening gap, and the performance of high-speed modern computers relies on evolving caching techniques.[44] There can be up to a 53% difference between the growth in speed of processor and the lagging speed of main memory access.[45]

Solid-state hard drives have continued to increase in speed, from ~400 Mbit/s via SATA3 in 2012 up to ~7 GB/s via NVMe/PCIe in 2024, closing the gap between RAM and hard disk speeds, although RAM continues to be an order of magnitude faster, with single-lane DDR5 8000MHz capable of 128 GB/s, and modern GDDR even faster. Fast, cheap, non-volatile solid state drives have replaced some functions formerly performed by RAM, such as holding certain data for immediate availability in server farms - 1 terabyte of SSD storage can be had for $200, while 1 TB of RAM would cost thousands of dollars.[46][47]

Remove ads

Timeline

SRAM

DRAM

SDRAM

SGRAM

Remove ads

See also

References

External links

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads