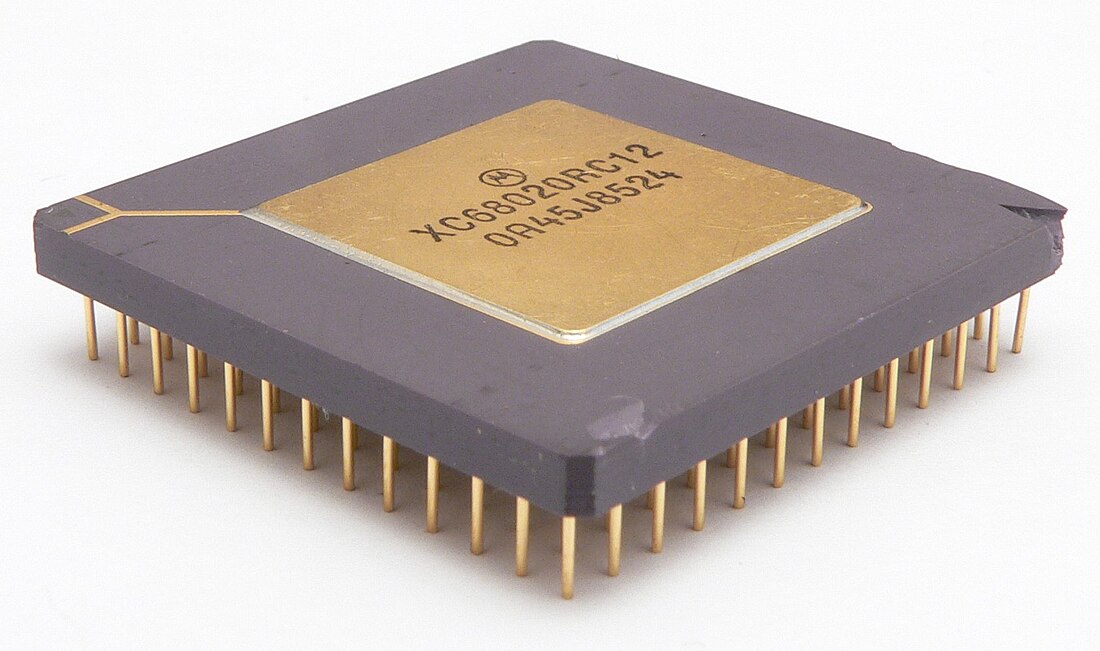

Motorola 68020

32-bit microprocessor by Motorola From Wikipedia, the free encyclopedia

The Motorola 68020 is a 32-bit microprocessor from Motorola, released in 1984. A lower-cost version was also made available, known as the 68EC020. In keeping with naming practices common to Motorola designs, the 68020 is usually referred to as the "020", pronounced "oh-two-oh" or "oh-twenty".

| General information | |

|---|---|

| Launched | 1984 |

| Designed by | Motorola |

| Performance | |

| Max. CPU clock rate | 12.5 MHz to 33 MHz |

| Data width | 32 bits |

| Address width | 32 bits |

| Cache | |

| L1 cache | 256 byte instruction cache[1]: 578 [2] |

| Architecture and classification | |

| Instruction set | Motorola 68000 series |

| Physical specifications | |

| Transistors |

|

| Package | |

| Products, models, variants | |

| Variant |

|

| History | |

| Predecessor | Motorola 68010 |

| Successor | Motorola 68030 |

The 020 was in the market for a relatively short time. The Motorola 68030 was announced in September 1986 and began deliveries in the summer of 1987. Priced about the same as the 020 of the time, the 030 was significantly faster and quickly replaced in 020 in almost every use.

History

Summarize

Perspective

68000 and 68010

At the time the Motorola 68000 was designed, Motorola's design and fabrication services were outdated. Although even small companies like MOS Technology and Zilog had moved on to silicon gate depletion mode NMOS logic on ever-larger wafers, Motorola was still using metal gates and enhancement mode and their largest fab worked on 4-inch wafers long after most lines had moved to 5-inch. Although the 68000 met the goal of being the fastest CPU available when it was introduced, it was not nearly as powerful as it could be if it had been designed with more modern techniques.[3]

During the period of the 68000 design, the company was working with Hitachi on their process technology and as part of this they opened a new fab, MOS-8, using 5-inch wafers and the latest HMOS process licensed from Intel. This line was capable of building all of the new techniques, but the 68000 went ahead with the older design as they were sure it would work. Moving to new design techniques would wait until the design was in the market.[4] The conversion to the new design techniques took place during the Motorola 68010 effort, a relatively minor upgrade to the original design that added basic virtual memory support for the emerging Unix workstation market.[5]

020 concept emerges

As this effort was ongoing, Motorola was canvassing their customers for their desires for future developments in the line. These all pointed to a fully 32-bit implementation. Those using the 68k in Unix systems also stated they would purchase a floating-point unit for every one of the machines if one was available.[6]

The original 68000 had been designed as a hybrid 16/32-bit system largely because the maximum number of pins available on dual inline packages (DIPs) was 64, and even at that size, packaging of this size was highly problematic.[7] By reducing the number of address pins to 24, and the data pins to only 16, there were enough free pins to implement all the other needed lines, like interrupts and power supplies. The 24-pin address bus meant that the memory could only be 16 MB in total, which was at this point becoming a limitation. The 16-bit data bus meant reading a 32-bit word from that memory required two bus cycles.

A design that had 32 pins for both the address and data busses would access data twice as fast, making the machine that much faster even with no other changes. Moving to 32-bit addressing would also make the implementation of virtual memory easier, and allow for more than 16 MB of random access memory. But doing so would also demand a much higher total pin count. By the early 1980s, similar limitations on all modern CPU designs led to the introduction of the pin grid array that replaced the DIP. For the new project, Motorola selected a 169-pin layout, giving them plenty of room to work with. The design ultimately used only 114 of them.

A great debate broke out about how to refer to the underlying design of the new chip in marketing materials. Technically, the 020 was moving from the long-established NMOS logic design to a CMOS layout, which requires two transistors per gate. Common knowledge of the era suggested that CMOS cost four times as much as NMOS, and there was a significant amount of the market that believed "CMOS equals bad."[8]

Launch, fabrication problems

The design was completed in the summer of 1983 and announced in June 1984.[9] This "super chip" was significant news at the time, with the New York Times making it a lead story in their business section. The launch price was quoted at $487 each, about the same as the 68000 when it was launched in 1980, but the 68000 was now available for about $15. However, it was understood that it would be some time before computers using the new chip would be available, as existing designs would have to be heavily modified to take advantage of its performance.[10]

The announcement led to Motorola's customers clamouring for supply. At this point, serious supply problems became evident. The design had been laid out to be built in the same MOS-8 factory as the 68000, although several new pieces of equipment were introduced to support it. By the time of the public release, the yield for the new chip was zero. That is, for every wafer sent through the multi-step process, zero working chips would be produced.[11]

Gary Johnson concluded the problem was the floor manager of MOS-8, Tom Felesi, and decided to replace him with Bill Walker, who was at that time running the older MOS-2 factory. Walker arrived at the plant on 5 July 1985 to find Johnson had not bothered to tell Felesi of the change, and arguments followed. Johnson eventually told Felesi this was indeed happening. Walker then toured the plant and found it had been turned into what was essentially a research and development lab, not a production line, with numerous bits of machinery in use nowhere else.[11]

One significant issue was a new piece of equipment from a new vendor, Genus, which produced tungsten silicide. The machine simply didn't work. Walker flew to California to meet with the CEO of Genus, who offered up nothing but excuses. Walker eventually slammed his hand down on the desk, breaking his watch band, and stated "No more excuses! I want this thing fixed now, today!" Genus took the demand seriously and fixed the machine. The CEO later sent Walker a new watch band to commemorate the event.[11]

Meanwhile, Walker instituted a new policy at MOS-8 to improve the plant itself. He normally called meetings at 6:30 AM. If things were not going well, he would move that up to 5:30, and even 4:30. This provided a strong incentive to get the plant running. The production problems were soon ironed out, and volume deliveries began late that year. By this point, their workstation customers had already developed complete systems ready to use the 020 and the new floating point unit, the Motorola 68881. Systems were in the market only five or six months after the 020 had been announced.[12]

Replacement

Design of the 020's follow-on began almost immediately. As part of their ongoing work with Hitachi, Motorola's fabrication system was finally catching up with the competition, as was their internal design workflow. This gave them considerably more room to work with, allowing the addition of larger processor caches, a built-in memory management unit (MMU) and other features. The Motorola 68030 was announced in September 1986,[13] with deliveries to begin the next summer. Due to the changes in the production lines, the new 030 would have a lower launch price than the 020.

There were significant differences between the 68000 and 020, especially the 32-bit memory interface. This required computer designs using it to be considerably different from earlier models. In contrast, there were few changes between the 020 and 030, the latter of which could be used as a drop-in replacement in many roles. For this reason, designs using the 030 appeared much more quickly after its release than the 020. The first Macintosh with the 020 was the Macintosh II released in March 1987, two years after the 020 had become widely available,[14] with low-volume initial shipments starting two months later.[15] Only eighteen months later, the Macintosh IIx replaced it, using the 030. Although it ran at the same 16 MHz clock speed, the IIx offered 3.9 MIPS compared to the II's 2.6.[16]

Description

Summarize

Perspective

The 68020 has 32-bit internal and external data and address buses, compared to the early 680x0 models with 16-bit data and 24-bit address buses. The 68020's ALU is also natively 32-bit, so can perform 32-bit operations in one clock cycle, whereas the 68000 took a minimum of two clock cycles due to its 16-bit ALU. Newer packaging methods allowed the '020 to feature more external pins without the large size that the earlier dual in-line package method required. The 68EC020 lowered cost through a 24-bit address bus. The 68020 was produced at speeds ranging from 12 MHz to 33 MHz.

Improvements over the 68010

The 68020 has a 32-bit arithmetic logic unit (ALU), 32-bit external data and address buses.[17] It adds extra instructions and additional addressing modes. The 68020 (and 68030) has a proper three-stage pipeline. Though the 68010 had a "loop mode", which sped loops through what was effectively a tiny instruction cache, it held only two short instructions and was thus little used. The 68020 replaced this with a proper instruction cache of 256 bytes, the first 68k series processor to feature true on-chip cache memory.

The previous 68000 and 68010 processors could only access word (16-bit) and long word (32-bit) data in memory if it were word-aligned (located at an even address). The 68020 has no alignment restrictions on data access. Naturally, unaligned accesses are slower than aligned accesses because they required an extra memory access.

The 68020 has a small 256-byte direct-mapped instruction cache, arranged as 64 four-byte entries. Although small, it still made a significant difference in the performance of many applications. The resulting decrease in bus traffic was particularly important in systems relying heavily on DMA.

Coprocessor support

The 68020 has a coprocessor interface supporting up to eight coprocessors. The main CPU recognizes "F-line" instructions (with the four most significant opcode bits all one), and uses special bus cycles to interact with a coprocessor to execute these instructions. Two types of coprocessors were defined: floating point units (MC68881 or MC68882 FPUs) and the paged memory management unit (MC68851 PMMU). Only one PMMU can be used with a CPU. In principle, multiple FPUs could be used with a CPU, but it was not commonly done. The coprocessor interface is asynchronous, so it is possible to run the coprocessors at a different clock rate than the CPU.

Multiprocessing features

Multiprocessing support is implemented externally by the use of an RMC pin[18] to indicate an indivisible read-modify-write cycle in progress. All other processors have to hold off memory accesses until the cycle is complete.[19] Software support for multiprocessing includes the TAS, CAS and CAS2 instructions.

In a multiprocessor system, coprocessors could not be shared between CPUs. To avoid problems with returns from coprocessor, bus error, and address error exceptions, it was generally necessary in a multiprocessor system for all CPUs to be the same model, and for all FPUs to be the same model as well.

Instruction set

The new instructions include some minor improvements and extensions to the supervisor state, several instructions for software management of a multiprocessing system (which were removed in the 68060), some support for high-level languages which did not get used much (and was removed from future 680x0 processors), bigger multiply (32×32→64 bits) and divide (64÷32→32 bits quotient and 32 bits remainder) instructions, and bit field manipulations.[20]

The new addressing modes add scaled indexing and another level of indirection to many of the pre-existing modes.

Architecture

Summarize

Perspective

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

With full 32-bit internal and external address buses, the address registers (A0 through A7) could utilize their full 32-bit width, and were capable of addressing the entire 4 GB address space.

The larger effective widths of the address registers presented some problem for earlier software that was not considered "32-bit clean". Some programs used the high 8 bits (bits 24-31) of addresses to contain various flag bits, with the understanding that the earlier 680x0 CPUs would safely ignore these high bits. Such software had to be rewritten to adjust to the larger physical address space available to the 68020 and later CPUs.

Usage

Summarize

Perspective

The 68020 was used in the Apple Macintosh II and Macintosh LC personal computers, Sun-3 workstations, Amiga 1200 (68EC020 variant), the Hewlett-Packard 8711 Series Network Analyzers, HP 9000/320, HP 9000/330, Apollo Computer's DN3000 and DN4000 workstations,[21] and the Alpha Microsystems AM-2000. The 68020 was an alternative upgrade to the Sinclair QL's 68008 in the Super Gold Card interface by Miracle Systems.

The Amiga 2500 and A2500UX optionally shipped with the A2620 Accelerator using a 68020, 68881 FPU and 68851 MMU. The 2500UX shipped with Amiga Unix, requiring an '020 or '030 processor.

A number of digital oscilloscopes from the mid-80s to the late-90s used the 68020, including the LeCroy 9300 Series[22] (higher end models including "C" suffix models used the more powerful 68EC030;[23] the 9300 models with a 68020 processor can be upgraded to the 68EC030 with a change of the CPU board[24]) and the earlier LeCroy 9400 series (all models[25][26][27][28] excluding the 9400/9400A which used the 68000[29]), along with certain Tektronix TDS Series models.[30] The HP 54520, 54522, 54540 and 54542 also use the 68020, together with a 68882 FPU.[31]

It is also the processor used on TGV trains to decode signalling information sent to the trains through the rails. It is used in the flight control and radar systems of the Eurofighter Typhoon combat aircraft.

The Nortel Networks DMS-100 telephone central office switch also used the 68020 as the first microprocessor of the SuperNode computing core.

Variant

The 68EC020 is a lower cost version of the Motorola 68020. The main difference is that the 68EC020 only has a 24-bit address bus, rather than the 32-bit address bus of the full 68020, and thus is only able to address 16 MB of memory.

The Amiga 1200 computer and the Amiga CD32 game console use the cost-reduced 68EC020; the Namco System 22, Taito F3 and Konami GX arcade boards also used this processor. The Atari Jaguar II prototype featured this to replace the 68000 of the original Atari Jaguar console.

It also found use in laser printers. Apple used it in the LaserWriter IIɴᴛx. Kodak used it in the Ektaplus 7016PS, and Dataproducts used it in the LZR 1260.

In 2014, Rochester Electronics re-established manufacturing capability for the 68020 microprocessor and it is still available today.

Technical data

| Formal name | MC68020[1]: 577 |

| CPU clock rate | 12.5, 16.67, 20, 25, 33 MHz (minimum 8 MHz, no on-chip clock generation)[1]: 577 |

| Voltage supply | 5 V |

| Maximum power | 1.75 W[1]: 577 |

| Production process | HCMOS, 3/8" silicon piece[1]: 577 |

| Chip carrier | PGA 169 (114 pins used) 34.16 mm × 34.16 mm[1]: 577 (53 °C/W without heatsink)[2] |

| Address bus | 32-bit (4 GB directly linear addressable)[1]: 578 [68EC020] 24-bit (16 MB addressable) |

| Data bus | 32-bit |

| Instruction set | 101 CISC instructions |

| Cache | 256 byte instruction cache[1]: 578 [2] |

| Register | |

| Branch handling | Branch prediction:

|

| Transistors | ~200,000[1]: 577 |

| Performance | 10 MIPS @ 33 MHz[33] |

References

External links

Wikiwand - on

Seamless Wikipedia browsing. On steroids.