Advanced RISC Machines

arquitectura de processador basada en RISC From Wikipedia, the free encyclopedia

Remove ads

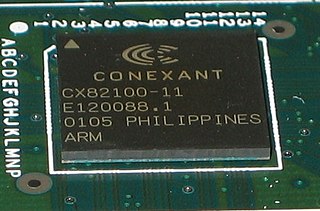

Advanced RISC Machines (ARM) és una família de microprocessadors RISC dissenyats per l'empresa Acorn Computers i desenvolupats per Advanced RISC Machines Ltd., una empresa derivada de l'anterior.

Remove ads

Un enfocament de disseny basat en RISC vol dir que els processadors ARM requereixen una quantitat menor de transistors que els procreadors x86 CISC típics en la majoria d'ordinadors personals. Aquest enfocament de disseny per tant ens porta a una reducció dels costos, calor i energia. Aquestes característiques són desitjables per a dispositius que funcionen amb bateries, com els telèfons mòbils, tauletes, etc.

ARM Holdings s'encarrega del desenvolupament del set d'instruccions i de l'arquitectura ARM per productes basats en aquesta tecnología, però no manufactura els productes encastats finals. La companyia periòdicament publica actualitzacions dels seus nuclis. Els nuclis actuals d'ARM Holdings suporten 64 bits d'adreces i 64 bits aritmètics.

Globalment ARM conté el conjunt d'instruccions d'arquitectura més utilitzat, en termes de quantitat de producció. Això ha estat gràcies al seu baix consum. S'arribà a produir 50 000 milions de processadors ARM l'any 2014.[1]

Remove ads

Història

El disseny de l'ARM va començar el 1983 com un projecte de desenvolupament en l'empresa Acorn Computers Ltd Roger Wilson i Steve Furber lideraven l'equip, l'objectiu era, originalment, el desenvolupament d'un processador avançat, però amb una arquitectura similar a la del MOS 6502. La raó era que Acorn tenia una llarga línia d'ordinadors personals basats en aquest micro, per la qual cosa tenia sentit desenvolupar-ne un amb el qual els desenvolupadors se sentissin còmodes.

L'equip va acabar el disseny preliminar i els primers prototips del processador l'any 1985, al que van anomenar ARM1. La primera versió utilitzada comercialment es va batejar com ARM2 i es va llançar l'any 1986.

L'arquitectura del ARM2 té un bus de dades de 32 bits si ofereix un espai d'adreces de 26 bits, juntament amb 16 registres de 32 bits. Un d'aquests registres s'utilitza com a comptador de programa, aprofitant els seus 4 bits superiors i els 2 inferiors per contenir el flag d'estat del processador.

El ARM2 és probablement el processador de 32 bits útil més simple del món, ja que té només 30.000 transistors. La seva simplicitat es deu al fet que no està basat en microcodi (sistema que sol ocupar al voltant de la quarta part de la quantitat total de transistors utilitzats en un processador), ja que, com era comú en aquella època, no inclou memòria cau. Gràcies a això, el seu consum en energia és bastant baix, alhora que ofereix un millor rendiment que un 286. El seu successor, el ARM3, inclou una petita memòria cau de 4 KiB, el que millora els accessos a memòria repetitius.

A finals dels anys 80, Apple Computer va començar a treballar amb Acorn en noves versions del nucli ARM. En Acorn es van adonar que el fet que el fabricant d'un processador fos també un fabricant d'ordinadors podria fer enrere als clients, per la qual cosa es va decidir crear una nova companyia anomenada ARM Holdings, que seria l'encarregada del disseny i gestió de les noves generacions de processadors ARM. Passava això en l'any 1990.

Aquest treball va derivar en l'ARM6, presentat en 1991. Apple va utilitzar l'ARM 610 (basat en el ARM6), com processador bàsic pel seu innovador PDA, l'Apple Newton. Per la seva banda, Acorn el va utilitzar a 1994 com a processador principal a la RiscPC.

El nucli va mantenir la seva simplicitat tot i els canvis: en efecte, el ARM2 té 30.000 transistors, mentre que el ARM6 només compta amb 35.000. La idea era que l'usuari final combinés el nucli de l'ARM amb un nombre opcional de perifèrics integrats i altres elements, podent crear un processador complet a la mesura de les seves necessitats.

La major utilització de la tecnologia ARM es va assolir amb el processador ARM7TDMI, amb milions d'unitats en telèfons mòbils i sistemes de videojocs portàtils.

DEC llicenciar el disseny, la qual cosa va generar una mica de confusió perquè ja produïa el DEC Alpha, i va crear el StrongARM. Amb una velocitat de rellotge de 233 MHz, aquest processador consumia només 1 W de potència (aquest consum d'energia s'ha reduït en els models més recents). Aquesta tecnologia va passar posteriorment a mans de Intel, com a fruit d'un acord jurídic, que la va integrar en la seva línia de processadors Intel i960 i va fer més àrdua la competència.

Freescale (una empresa que va derivar de Motorola l'any 2004), IBM, Infineon Technologies, OKI, Texas Instruments, Nintendo, Philips,fvh Atmel, Sharp, Samsung i STMicroelectronics també llicenciar el disseny bàsic de l'ARM .

El disseny de l'ARM s'ha convertit en un dels més usats del món, des de discs durs fins joguines. Avui en dia, prop del 75% dels processadors de 32 bits tenen aquest xip en el seu nucli.

Remove ads

Llicències

Llicència de nucli

El negoci principal d'ARM Holdings és la venda de nuclis IP, aquestes llicències s'utilitzen per crear microcontroladors i CPUs basats en aquests nucles. El productor del disseny original combina el nucli ARM amb altres parts per produir una CPU completa, normalment s'escull un nucli que pugui ser manipulat per fàbriques de semiconductors a un preu baix i que doni un rendiment substancial.

La implementació amb més èxit ha estat l'ARM7TDMI amb centenars de milions de còpies venudes. Atmel ha estat precursor del centre de disseny en sistemes encastats basats en ARM7TDMI.

Les arquitectures ARM utilitzades a smartphones, PDAs i altres dispositius van des de l'ARMv5, que s'utilitza en dispositius de gamma baixa fins a l'ARMv6 o l'ARMv7 utilitzats en dispositius de gamma alta. L'ARMv7 inclou una unitat de punt flotant amb una millora en la velocitat en comparació amb el software basat en punt flotant.

L'any 2009 diversos productors de dispositius electrònics van introduir netbooks basats en les CPUs de l'arquitectura ARM, com a competició directa als netbooks basats en intel Atom.

ARM Holdings ofereix una varietat en termes de llicències, que varien en cost i prestacions. ARM Holdings ofereix a tots els llicenciataris una descripció de maquinari integrable del nucli ARM, així com el conjunt d'eines de desenvolupament de programari (compilador, depurador, kit de desenvolupament de programari) i el dret de vendre el silici fabricat que conté la CPU ARM.

Els paquets SoC que integren els dissenys dels nuclis ARM inclouen les tres primeres generacios de Nvidia Tegra, la família de CSR plc Quatro, ST-Ericsson Nova i NovaThor, el MCU Precision32 dels laboratoris Silicon, els productes OMAP de Texas Instruments, els productes Hummingbird i Exynos de Samsung, Apple A4, A5 i A5X, i i.MX. De Freescale.

Els llicenciataris Fabless que desitgen integrar un nucli ARM en el seu propi disseny de xips, estan normalment interessats en l'adquisició d'un nucli IP llest per manufacturar. Per aquest clients, ARM Holdings ofereix una descripció de portes netlist del nucli ARM triat, juntament amb una simulació abstracta del model i tests dels programes per donar una ajuda en la integració del disseny i verificació.

Els clients més ambiciosos inclosos els fabricants de dispositius integrats opten per adquirir el processador IP en forma RTL sintetitzables (Verilog). Amb els RTL sintetitzables, el client té la capacitat de realitzar optimitzacions a nivell d'arquitectura i extensions. Això permet al dissenyador aconseguir objectius de dissenys exòtics, impossibles d'aconseguir si la netlist no fos modificable (alta velocitat de rellotge, baix consum d'energia, set d'instruccions d'extensions, etc.).

ARM Holdings no atorga al llincenciatari el dret a revendre la mateixa arquitectura ARM, però aquests sí que poden vendre lliurement el producte manufacturat, com els dispositius de xips, plaques d'avaluació i sistemes complets.

Els preus d'IP d'ARM Holdings es basa en el seu valor percebut. Els nuclis amb un baix rendiment solen tenir un preu menor que nuclis amb un alt rendiment. En termes d'implementació, un nucli sintetitzable costa més que un nucli hard macro (caixa negra).

Llicència de l'arquitectura

Les empreses també poden obtenir una llicència d'arquitectura ARM per al disseny dels seus propis nuclis de CPU utilitzant els conjunts d'instruccions ARM. Aquests nuclis han de complir plenament amb l'arquitectura ARM.

Remove ads

Famílies d'ARMs

Actualment hi ha diferents tipus de processadors ARM creats per ARM Holdings que estan dividits en diferents famílies segons els dispositius a què van dirigits. Tot i que els més coneguts són els de la sèrie A perquè són els que s'utilitzen en telèfons intel·ligents o tauletes tàctils per diverses empreses, és bo saber que existeix diversitat de processadors amb arquitectura ARM. Són aquests:

Sèrie A:

És la sèrie més coneguda dels processadors ARM, està dedicada als dispositius que tenen un sistema operatiu que gestiona la interacció entre el hardware i software. Aquests processadors són els més utilitzats en telèfons intel·ligents i tauletes independentment de si funcionen sota Android, IOs o Windows. També s'empren en televisions i en dispositius com GPS.

Sèrie R:

Aquesta sèrie és la que està encarada cap a dispositius que treballen a temps real. Normalment aquests dispositius treballen amb sistemes operatius a temps real. Se solen instal·lar en sistemes de control dels automòbils, infraestructures sense fils, impressores, dispositius de xarxa,... dispositius que en definitiva necessiten rapidesa entre l'entrada i sortida d'un sistema.

Sèrie M:

Aquesta sèrie va dirigida a sistemes encastats (embedded Systems). Els sistemes encastats normalment sempre desenvolupen la mateixa tasca i necessiten fer-la a molt baix consum. Alguns exemples on s'instal·len aquests dispositius són: sistemes de control de motors, electrodomèstics, sensors,...

Sèrie securecore:

Aquests xips van adreçats a instal·lar-se en dispositius d'ús quotidià en què es necessita una certa robustesa. De fet s'instal·len en les SIM’s dels telèfons mòbils, targetes de crèdit, al DNI espanyol, sistemes avançats de pagament,...

Els nuclis

Remove ads

Nuclis Cortex-M

Els nuclis ARM Cortex-M són un grup de nuclis per a processadors RISC de 32-bits basats en l'arquitectura ARM. Aquests nuclis estan dissenyats per a ser utilitzats en microcontroladors, dit grup consisteix en el nuclis M0, M0+, M1, M3, M4 i M7.

Cortex-M0

El processador Cortex-M0 és un processador amb un nombre petit de portes però presenta una alta eficiència energètica. Aquest processador està destinat a microprocessadors i aplicacions altament encastades que requereixen un processador optimitzat per a l'àrea. El consum d'aquest processador és de 12.5μW/MHz (90LP process, configuració mínima) en una àrea menor de 12k portes.

Característiques

- Arquitectura ARMv6-M de 32 bits.

- Pipeline de 3-fases.

- Execució de les instruccions del tipus in-order.

- Set d'instruccions:

- Thumb (principalment), desproveït de CBZ, CBNZ, IT .

- Thumb-2 (petita part), només BL, DMB, DSB, ISB, MRS, MSR.

- Multiplicador hardware de 32-bits amb un resultat de 32-bits.

- Forwards compatibles amb altres processadors de perfil-M.

- Totes les instruccions són tractades com a reiniciables.

- LDM/STM incloses.

- D'1 a 32 interrupcions, més NMI.

Complements de silici:

- Multiplicador de velocitat del Hardware: 1-cicle o 32-cicles.

Xips

Microcontralodrs basats en el nucli Cortex-M0:

- Cypress Semiconductor PSoC 4

- Infineon Technologies XMC1000

- Nordic Semiconductor nRF51

- NXP LPC1100, LPC1200

- nuvoTon NuMicro

- Sonix SN32F700

- STMicroelectronics STM32 F0

- Toshiba TX00

Xips que incorporen el nucli Cortex-M0 com a secundari:

- NXP LPC4300 (1 Cortex-M4F + 1 Cortex-M0)

Cortex-M0+

El processador Cortex M0+ és una versió millorada del Cortex-M0, el qual presenta una arquitectura optimitzada i una reducció del nombre de fases del pipeline, aquest últim, passa de ser de 3 a 2 fases. Amb tot això, s'aconsegueix una reducció del consum d'energia que passa a ser de 9.8µW/MHz (90LP process, configuració mínima) i s'incrementa el rendiment a 2.42 CoreMark/MHz. Com que cada aplicació té unes necessitats específiques Cortex-M0+ ofereix una gran selecció de complements per a solucionar aquestes necessitats. Alguns d'aquests complements són una Memory protection unity (MPU) i una re-locatable vector-table són les aplicacions més comunes rebudes dels processadors Cortex-M3 i Cortex-M4. Altres complements de silici que es poden incorporar són single-cycle I/O interface per a tenir un control més ràpid i Micro trace buffer(MTB) per a millorar la depuració.

Característiques

- Arquitectura ARMv6-M

- Pipeline de 2-fases.

- Set d'instruccions(igual que amb Cortex-M0):

- Thumb (principalment), desproveït de CBZ, CBNZ, IT .

- Thumb-2 (petita part), només BL, DMB, DSB, ISB, MRS, MSR.

- Multiplicador hardware de 32-bits amb un resultat de 32-bits.

- D'1 a 32 interrupcions, més NMI.

Complements de silici:

- Multiplicador de velocitat del Hardware: 1-cicle o 32-cicles.

- 8 regions d'unitats de protecció de memoria (MPU) (el mateix que amb Cortex-M3 i Cortex-M4).

- Re-locatable vector-table (el mateix que amb Cortex-M3 i Cortex-M4).

- Single-cycle I/O interface (únic per a Cortex-M0+).

- Micro trace buffer (MTB) (únic per a Cortex-M0+).

Xips

Microcontroladors basats en el nucli Cortex-M0+:

- Atmel SAMD, SAMR

- Freescale Kinetis E, EA, L, M, V1, W0

- NXP LPC800, LPC11E6x, LPC11U6x

- Silicon Labs/Energy Micro EFM32 Zero

- Spansion FM0+

- STMicroelectronics STM32 L0

Cortex-M3

Cortex-M3 presenta un alt rendiment i un baix consum dinàmic d'energia, ja que, incorpora modes de somni (sleep modes) i complementariament incorpora capacitats per a retenir l'estat. Amb això ens podem assegurar que podem tenir aplicacions amb un baix consum i un bon rendiment. La combinació d'aquestes característiques i el rendiment ens permet manejar múltiples canals d'I/O i estàndards de protocols com USB OTG.

Característiques

- Arquitectura ARMv7-M

- Pipeline de 3-fases amb predicció de salts.

- Set d'instruccions:

- Thumb (tot).

- Thumb-2 (tot).

- Multiplicador hardware de 32-bits amb un resultat de 32-bits o 64-bits, del tipus signed o unsigned, suma o resta després de la multiplicació.

- 32-bit hardware divide (2-12 cycles).

- Saturated math support.

- Extensió DSP: Single cycle 16/32-bit MAC, single cycle dual 16-bit MAC, 8/16-bit SIMD arithmetic.

- D'1 a 240 interrupcions, més NMI.

- 12 cicles de latència d'interrupcions.

- Incorpora sleep modes.

Complements de silici:

- Opcional Memory Protection Unit (MPU): 0 o 8 regions.

Xips

Microcontroladors basats en el nucli Cortex-M3:

- Actel SmartFusion, SmartFusion 2

- Analog Devices ADuCM3xx

- Atmel SAM3A, SAM3N, SAM3S, SAM3U, SAM3X

- Cypress Semiconductor PSoC 5

- Spansion FM3

- Holtek HT32F

- Luminary Micro LM3S1968

- NXP LPC1300, LPC1700, LPC1800

- ON Semiconductor Q32M210

- Silicon Labs Precision32

- Silicon Labs/Energy Micro EFM32 Tiny, Gecko, Leopard, Giant

- STMicroelectronics STM32 F1, F2, L1, W

- Toshiba TX03

Xips que incorporen el nucli Cortex-M3 com a secundari:

- CSR Quatro 5300 series (Cortex-M3 com a co-processador)

- Texas Instruments F28, LM3, TMS470, OMAP 4470 (1 Cortex-A9 + 2 Cortex-M3)

- XMOS XS1-XA family (7 xCORE + 1 Cortex-M3)

Cortex-M4

Cortex-M4 és una versió millorada del Cortex-M3 afegint instruccions DSP i un complement d'unitat de punt flotant (FPU). Si conté el complement anomenat anteriorment es diu Cortex-M4F.

Característiques

- Arquitectura ARMv7E-M

- Pipeline de 3-fases amb predicció de salts.

- Set d'instruccions:

- Thumb (tot).

- Thumb-2 (tot).

- Multiplicador hardware de 32-bits amb un resultat de 32-bits o 64-bits, del tipus signed o unsigned, suma o resta després de la multiplicació.

- Divisor hardware de 32-bits (2-12 cicles).

- Saturated math support.

- Extensió DSP: Single cycle 16/32-bit MAC, single cycle dual 16-bit MAC, 8/16-bit SIMD arithmetic.

- D'1 a 240 interrupcions, més NMI.

- 12 cicles de latència d'interrupcions.

- Incorpora sleep modes.

Complements de silici:

- Unitat de punt flotant (FPU): single-precision only IEEE-754 compliant. Anomenat FPv4-SP extension.

- Unitat de protecció de memòria (MPU): 0 o 8 regions.

Xips

Microcontrolador basats en el nucli Cortex-M4:

- Atmel SAM4L, SAM4N, SAM4S

- Freescale Kinetis K, W2

Microcontrollers basats en el nucli Cortex-M4F (M4 + FPU):

- Atmel SAM4C (dual core), SAM4E, SAMG

- Freescale Kinetis K, V3, V4

- Infineon XMC4000

- NXP LPC4000, LPC4300 (1 Cortex-M4F + 1 Cortex-M0)

- Silicon Labs/Energy Micro EFM32 Wonder

- Spansion FM4F

- STMicroelectronics STM32 F3, F4

- Texas Instruments LM4F, TM4C, MSP432

- Toshiba TX04

Xips que incorponern tant el nucli Cortex-M4 com el nucli M4F :

- Freescale Vybrid VF6 (1 Cortex-A5 + 1 Cortex-M4F)

- Texas Instruments OMAP 5 (1 dual-core Cortex-A15 + 2 Cortex-M4)

Remove ads

Disseny

El joc d'instruccions de l'ARM és similar al del MOS 6502, però inclou característiques addicionals que li permeten aconseguir un millor rendiment en la seva execució. Per mantenir el concepte tradicional de RISC, es va incloure l'ordre d'execució en un temps bastant bo, i en general, en un cicle. La característica més interessant és l'ús dels 4 bits de codi condicional a la part superior de cada instrucció, fent que cada instrucció pugui ser una condició.

Aquest tall permet augmentar l'espai per a alguns desplaçaments en l'accés a la memòria, però també permet evitar caure en cicles fora de control quan l'aplicació sigui per a petites instruccions condicionades. L'exemple estàndard és el màxim comú divisor, segons l'algorisme d'Euclides.

Exemple a C

int GCD (int i, int j)

{

while (i ! = j) if (i> j) i -= j; else j -= i; return i;

}

Expressat en codi assemblador ARM, el cicle, amb una petita rotació, permet veure una cosa similar a això

b test loop subgt Ri, Ri, Rj sublevat, que tenien Rj, Rj, Ri test cmp Ri, Rj BNE loop

el qual permet girar al voltant de la condició.

Una altra característica única del joc d'instruccions és la possibilitat d'afegir shifts i rotar en el processament de dades (aritmètic, lògic i moviment de registres), per exemple, la instrucció en C "a+= (j <<2);" pot ser millorada com una instrucció simple en l'ARM, permetent la reubicació del registre.

Tot això fa que es necessitin menys operacions de càrrega i emmagatzematge, millorant el rendiment.

El processador ARM també té algunes característiques que són rares en altres arquitectures també considerades RISC, com l'adreçament relatiu, i el pre i post increment en el mode d'adreçament.

Té dos modes de funcionament: l'Armi amb instruccions que ocupen 4 bytes, més ràpides i potents (hi ha instruccions que només estan en aquesta manera) però amb major consum de memòria i d'electricitat. I la manera THUMB, més limitat, amb instruccions que ocupen 2 bytes i amb menor consum de corrent

Remove ads

ARMv8

És l'última versió de l'arquitectura ARM. Aquesta arquitectura es veurà implementada directament amb els processadors ARM Cortex-A57 i Cortex-A53 que l'empresa ARM Holdings ha tret el 2014 al mercat.

L'arquitectura dels ARMv8 (darrera versió), ofereix compatibilitat entre l'arquitectura de 32 i 64 bits. Per fer-ho permet 2 estats diferents d'execució.

En l'execució de 64 bits utilitza els registres de 64 bits i suporta el conjunt d'instruccions anomenat A64. En canvi, l'execució de 32 bits utilitza els registres de 32 bits i suporta el conjunt d'instruccions de A32. El conjunt d'instruccions A32 també inclou un conjunt més petit d'instruccions de mida més petita anomenat Thumb.

ARMv8 té 3 tipus d'arquitectures:

- Una que permet la virtualització de memòria a través de la MMU i pot utilitzar tant les instruccions A64, A32 i T32 (convencional i més freqüent).

- Perfil de temps real: basa l'arquitectura en la protecció de la memòria amb una Memory Protection Unit (MPU).

- Perfil de Microcontrolador: implementa el model d'interrupcions de baixa latència i suporta les instruccions T32.

L'execució AArch64 ofereix 31 registres de propòsit general que s'anomenen Xn en què n és el nombre de registre. El registre X30 s'utilitza com a link register. En aquests 31 registres també hi tenim el PC, SP (stack pointer) i ELRs (exception link registers). També tenim en l'execució A64 on 3 registres de l'EL0 – EL3 per implementar els privilegis d'execució. Les instruccions A64 són instruccions de mida fixa que utilitzen codificacions de 32 bits.

L'execució AArch32 ofereix 32 registres de propòsit general de 32 bits entre els quals es troben el PC, SP i LR (link register) que fa la funció de registre ELR i PLR (Procedure link register). L'execució també compta amb 32 registres de 64 bits per instruccions SIMD avançades de coma flotant. L'execució AArch32 suporta les instruccions A32 i T32. La diferència és que les A32 tenen mida fixa i es codifiquen en 32 bits, en canvi les T32 tenen mida variable i utilitzen tant 32 bits com 16 bits. Les instruccions de 16 bits són les anomenades Thumb.

No ha sigut fins a aquesta versió que han aparegut també registres de 64 bits que en assemblar es diferencien amb la lletra X, ja que els de 32 bits són W.[2]

L'arquitectura ARMv8 suporta dades de tipus:

- Byte -> 8 bits

- Halfword -> 16 bits

- Word -> 64 bits

- Doubleword -> 64 bits

- Quadword -> 128 bits

També suporta dades en coma flotant de diferents tipus i diferents opcions en els registres per executar operacions SIMD amb elements de mida variable en el vector de 128 bits. Els elements dels vectors SIMD poden ser de 8, 16, 32 i 64 bits.

Remove ads

Tecnologies

Thumb

Les instruccions Thumb s'han utilitzat en els condicionals. Aquest conjunt d'instruccions pretén disminuir la quantitat de codi escrit, millorar la densitat del codi i aconseguir un rendiment superior a un codi de 32 bits on el port de memòria o amplada del bus de comunicacions són menors a 32 bits. En general en aplicacions s'insereix un petit rang d'adreces de memòria amb un datapath de 32 bits (per exemple: Game Boy Advance), i la resta són 16 bits en mode wide o narrower.

La primera CPU amb la tecnologia Thumb va ser el ARM7TDMI. Tota la família posterior a l'ARM9, incloent-hi el processador Intel XScale, tenen incorporada la tecnologia en el seu nucli.

El 2003 conincidint amb la sortida de ARMv7 va sortir també el conjunt d'instruccions Thumb-2 que estenia el conjunt d'instruccions en versions prèvies però que segueix tenint la mateixa missió.

TrustZone

Part del hardware que proporcionen seguretat en aquest. En alguns dispositius com tauletes o telèfons intel·ligents s'executen instruccions d'aplicacions baixades d'Internet que a vegades inclouen software maliciós. Pretén reduir l'accés a certes parts del hardware per evitar errors, accés a dades de memòria,...

Jazelle

ARM té implantada una tecnologia que permet que certs tipus d'arquitectures executin Java bytecode nativament al maquinari. La primera CPU a utilitzar Jazelle va ser el ARM926EJ-S, sent anomenats amb una J a tots els processadors que suportessin aquesta tecnologia.

VFP

Conjunt d'instruccions per millorar les possibilitats d'operar amb coma flotant en diferents precisions. Normalment s'utilitza en aplicacions en automobilisme (ABS, control de tracció i suspensió), gràfics 3D, tractament d'imatges (impressores i càmeres digitals) o per controlar sistemes industrials a temps real. Les arquitectures ARM ja porten VFPv2 de la versió ARMv5.

SIMD

Instruccions (Single Instruction Multiple Data) que millora l'speedup en operacions lògiques o aritmètiques. La millora NEON SIMD és una extensió de 128 bits en els ARM de la sèrie A. Estan pensats per accelerar els càlculs en els jocs, reproducció de vídeo, so,... Com en totes les instruccions ARM permet l'execució d'operacions aritmeticològiques en diferents elements d'un vector de manera paral·lela.

Remove ads

Vegeu també

Enllaços externs

Referències

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads