Circuit integrat tridimensional

és un circuit integrat en tecnologia 3D. / From Wikipedia, the free encyclopedia

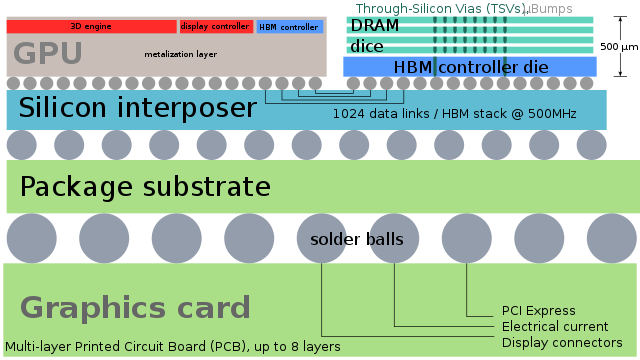

Un circuit integrat tridimensional (amb acrònim anglès IC 3D) és un circuit integrat (IC) MOS (semiconductor d'òxid metàl·lic) fabricat apilant fins a 16 o més circuits integrats i interconnectant-los verticalment utilitzant, per exemple, vies de silici (TSV). o connexions Cu-Cu, de manera que es comporten com un únic dispositiu per aconseguir millores de rendiment amb una potència reduïda i una empremta més petita que els processos bidimensionals convencionals. El 3D IC és un dels diversos esquemes d'integració 3D que exploten la direcció z per aconseguir beneficis de rendiment elèctric en microelectrònica i nanoelectrònica.[1]

Els circuits integrats 3D es poden classificar pel seu nivell de jerarquia d'interconnexió a nivell global (encapsulat), intermedi (coixinet d'enllaç) i local (transistor).[2] En general, la integració 3D és un terme ampli que inclou tecnologies com l'embalatge a nivell d'hòsties 3D (3DWLP); Integració basada en interposadors 2.5D i 3D; CI apilats en 3D (SICs 3D); Integració heterogènia 3D; i integració de sistemes 3D.;[3] així com el veritable 3D monolític IC

Organitzacions internacionals com el Comitè de full de ruta tecnològic de Jisso (JIC) i el full de ruta tecnològic internacional per a semiconductors (ITRS) han treballat per classificar les diferents tecnologies d'integració 3D per afavorir l'establiment d'estàndards i fulls de ruta d'integració 3D.[4] A partir de la dècada de 2010, 3D Els circuits integrats s'utilitzen àmpliament per a la memòria flash NAND i en dispositius mòbils.L'embalatge 3D es refereix a esquemes d'integració 3D que es basen en mètodes d'interconnexió tradicionals, com ara fils d'interconnexió i flip xip per aconseguir l'apilament vertical. L'embalatge 3D es pot dividir en sistema 3D en paquet (3D SiP) i paquet de nivell d'oblies 3D (3D WLP). Els SiP 3D que fa temps que estan en la fabricació convencional i tenen una infraestructura ben establerta inclouen matrius de memòria apilades interconnectades amb enllaços de filferro i configuracions de paquet en paquet (PoP) interconnectades amb enllaços de filferro o tecnologia de xip flip. PoP s'utilitza per integrar verticalment tecnologies dispars. 3D WLP utilitza processos a nivell d'hòsties com ara les capes de redistribució (RDL) i processos de bumping d'hòsties per formar interconnexions.