正反器 (英語:Flip-flop, FF 雙穩態多諧振盪器 (bistable multivibrator 序向邏輯電路 以及各種複雜數位系統的基本邏輯單元。正反器和閂鎖是在電腦 、通訊 和許多其他類型的系統中使用的數位電子系統 的基本組成部分。

R1, R2 = 1 kΩ, R3, R4 = 10 kΩ正反器電路圖,取自Eccles與Jordan在1918年時申請專利的檔案。 正反器的線路圖由邏輯閘 組合而成,其結構均由SR閂鎖 衍生而來(廣義的正反器包括閂鎖)。正反器可以處理輸入、輸出訊號和時序脈波(CK)之間的相互影響。這裡的正反器特指flip-flop,flip-flop一詞主要是指具有兩個狀態相互翻轉,例如程式語言 中使用flip-flop buffer(翻譯作雙緩衝) [來源請求]

正反器可以分成幾種常見的類型: SR (設定-重設,"set-reset"), D (數據或延遲,"data" or "delay"[ 1] T (反轉,"toggle"),和JK 。 以上類型的正反器皆可用特徵方程,以現有的輸入、輸出訊號(Q ),導出下個(即下個時鐘脈衝的)輸出(Q next

由或非 門 所組成的RS正反器 基本RS正反器又稱SR閂鎖,是正反器中最簡單的一種,也是各種其他類型正反器的基本組成部分。兩個反及閘 或反或閘 的輸入端輸出端進行交叉耦合或首尾相接,即可構成一個基本RS正反器。

當R與S皆為低電位,回授 會讓Q與Q (Q的反相)保持於一個固定的狀態。當S(Set)為高電位,R(Reset)為低電位時,輸出Q會被強制設定為高電位;相反的,當S為低電位,R為高電位時,輸出Q會被強制設定為低電位。

More information SR閂鎖運算[2], 狀態轉移表 ...

SR閂鎖運算[ 2]

狀態轉移表 激發表

S R Qnext 動作 Q Qnext S R

0

0

Q

保持

0

0

0

X

0

1

0

重設

0

1

1

0

1

0

1

設定

1

0

0

1

1

1

X

不允許的輸入

1

1

X

0

Close

特徵方程為

Q

n

e

x

t

=

S

+

R

¯

Q

{\displaystyle Q_{next}=S+{\overline {R}}Q}

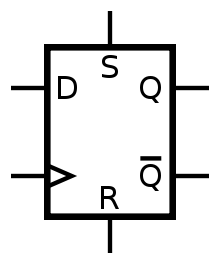

D正反器符號。> 是時脈輸入,D是數據輸入,Q是暫存數據輸出,Q'則是Q的反相值,S為1時強迫Q值為1,R為1時強迫Q值為0,以下圖例同 D正反器有一個輸入、一個輸出和一個時脈輸入,當時脈由0轉為1時,輸出的值會和輸入的值相等。此類正反器可用於防止因為雜訊 所帶來的錯誤,以及通過管線 增加處理數據的數量。

Q

n

e

x

t

=

D

{\displaystyle Q_{next}=D}

真值表 如下:

D

CK

Q

Qnext

0

↑

X

0

1

↑

X

1

X

0(1)

0

0

X

0(1)

1

1

JK正反器符號。J、K是數據輸入 JK正反器的時序圖 JK正反器的名稱來源不明。

JK正反器設有兩個輸入,其輸出的值由以下的算式來決定。

Q

n

e

x

t

=

J

Q

¯

+

K

¯

Q

{\displaystyle Q_{next}=J{\overline {Q}}+{\overline {K}}Q}

[ 3]

JK正反器和正反器中最基本的RS正反器結構相似,其區別在於,RS正反器不允許R與S同時為1,而JK正反器允許J與K同時為1。當J與K同時變為1的同時,輸出的值狀態會反轉。也就是說,原來是0的話,變成1;原來是1的話,變成0。

對應表如下:

More information JK正反器運算[4], 狀態轉移表 ...

JK正反器運算[ 4]

狀態轉移表 激發表

J K CK 動作 Qnext Q Qnext

動作 J K

0

0

↑

保持

Q

0

0

不變

0

X

0

1

↑

重設

0

0

1

設定

1

X

1

0

↑

設定

1

1

0

重設

X

1

1

1

↑

反轉

Q 1

1

不變

X

0

X

X

0(1)

保持

Q

Close

T正反器符號。T是數據輸入 T正反器(Toggle Flip-Flop,or Trigger Flip-Flop)設有一個輸入和輸出,當時脈由0轉為1時:如果輸入端T為1,則輸出端的狀態Q發生反轉;如果輸入端T為0,則輸出端的狀態Q保持不變。把JK正反器的J和K輸入點連接在一起,即構成一個T正反器。

因此T觸發器的算式為:

Q

n

e

x

t

=

T

¯

Q

+

T

Q

¯

=

Q

⊕

T

{\displaystyle Q_{next}={\overline {T}}Q+T{\overline {Q}}=Q\oplus T}

在一個較為複雜的數位系統 中,需要多個正反器翻轉時間同步,這時候需要附加門控電路 而構成同步正反器。

為了防止空翻現象 對正反器實際工作的影響,主從結構正反器被研製出來。

由於主從RS正反器對輸入訊號有所約束(R跟S不能同時為1),又開發出了主從JK正反器。

建立時間 (setup time)是指數據在被採樣時鐘邊沿採樣到之前 ,需保持穩定的最小時間。維持時間 (hold time)是指數據在被採樣時鐘邊沿採樣到之後 ,需保持穩定的最小時間。在正反器的數據手冊一般會標示元件的建立時間(tsu )及維持時間(th ),一般會是以奈秒 (ns)為單位,有些先進的正反器可以到數百皮秒 (ps)。若數據及控制輸入從採樣時鐘邊沿之前就維持定值,且時間超過建立時間,在採樣時鐘邊沿之後就維持定值,且時間也超過維持時間,可以避免正反器的亞穩態

Roth, Charles H. Jr. "Latches and Flip-Flops." Fundamentals of Logic Design. Boston: PWS, 1995. Print.

M Morris Mano, Michael D Ciletti. Digital design: With an Introduction to the Verilog HDL 培生教育 . 2013: 第216頁. ISBN 9780273764526 Mano, M. Morris; Kime, Charles R. Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. 2004: pg283. ISBN 0-13-191165-1 Hwang, Enoch. Digital Logic and Microprocessor Design with VHDL . Thomson. 2006 [2010-02-22 ] . ISBN 0-534-46593-5原始內容 存檔於2008-10-12). Salman, E., Dasdan, A., Taraporevala, F., Kucukcakar, K., Friedman, E. Pessimism Reduction in Static Timing Analysis Using Interdependent Setup and Hold Times. Proc. of Int. Symp. on Quality Electronic Design (ISQED): 159–164. 2006. (This paper explains the interdependence of setup time, hold time, and clock-to-q delay and shows how to use it for pessimism reduction in static timing analysis.)Schulz, Klaus-E. Ideal pulse circuit without RC-combination and non-clocked JK flip-flops (look discussion) (PDF) . 2007. [永久失效連結 Michael Keating, Pierre Breacaud. 片上系统——可重用设计方法学(第二版)(英文名:Reuse Methodology Manual for System-on-a-Chip Designs, Third Edition). 北京: 電子工業出版社. 2004. ISBN 7-5053-9338-3