MIPS架构

指令集架構 来自维基百科,自由的百科全书

MIPS(Microprocessor without Interlocked Pipeline Stages)[1],是一种采取精简指令集(RISC)的指令集架构(ISA)[2]:A-1[3]:19,由美国MIPS电脑系统公司开发,现为美普思科技。MIPS广泛被使用在许多电子产品、网络装置、个人娱乐装置与商业装置上。最早的MIPS架构是32位,最新的版本已经变成64位。商业市场主要竞争对手为ARM与RISC-V。

MIPS架构有多个版本,包括MIPS I、II、III、IV,以及MIPS V,它们各是MIPS32/64( 32位、64位的实现)发布的五个版本。早期的MIPS架构只有32位的版本,随后才开发64位的版本。截至2017年4月,MIPS32/64的当前版本是MIPS32/64 Release 6[4][5]。MIPS32/64与MIPS I-V的主要区别不仅在于它除了用户态架构外,还定义了特权内核模式的系统控制协处理器。

MIPS架构有几个可选的拓展,比如MIPS-3D,它是一个专用于常见3D计算任务的浮点SIMD指令集的简单集合[6];MDMX(MaDMaX)是一个应用更加广泛的整数SIMD指令集,它使用了64位浮点数寄存器;MIPS16e则为提供了指令流压缩的功能,这可以减小程序的体积[7];MIPS MT则提供了多线程的能力[8]。

在一些大学和技术学校中电脑架构的课程上,学生们通常会学习MIPS架构[9]。这个架构极大地影响了后来的精简指令集架构,如Alpha。2021年3月,MIPS宣布MIPS架构的开发已经结束,因为该公司正在向RISC-V过渡[10]。

历史

此章节需要扩充。 (2020年2月) |

MIPS架构的第一个版本是由MIPS电脑系统公司为其R2000微处理器设计的,这是第一个MIPS的实现。MIPS和R2000都是在1985年一起推出的[来源请求]。当MIPS II推出时,MIPS更名为MIPS I,以区别于新版本[3]:32。

MIPS电脑系统公司的R6000微处理器(1989年)是第一个MIPS II实现[3]:8,专为伺服器设计,由Bipolar Integrated Technology制造和销售,但在商业上失败了。在1990年代中期,许多用于嵌入式系统的新32位MIPS处理器都是MIPS II实现,因为1991年引入64位MIPS III架构,使得直到1999年MIPS 32推出前,MIPS II都是最新的32位MIPS架构[3]:19。

MIPS电脑系统公司的R4000微处理器(1991年)是第一个MIPS III实现。它设计用于个人、工作站和伺服器电脑。MIPS电脑系统积极推广MIPS架构和R4000,建立高级计算环境(ACE)联盟以推进其高级RISC计算(ARC)标准,旨在将MIPS建立为主导的个人计算平台。ARC在个人电脑上几乎没有成功,但R4000(和R4400派生产品)广泛用于工作站和伺服器电脑,尤其是其最大的用户硅谷图形公司(SGI)。R4000的其他用途包括高端嵌入式系统和超级计算机。MIPS III最终由许多嵌入式微处理器实现。Quantum Effect Design的R4600(1993年)及其派生产品广泛应用于高端嵌入式系统和低端工作站和伺服器。MIPS科技的R4200(1994年)专为嵌入式系统、手提电脑和个人电脑而设计。NEC制造的派生产品R4300i用于N64游戏机。N64和PlayStation是1990年代中期MIPS架构处理器的最大用户之一。

第一个MIPS IV实现是MIPS科技R8000微处理器晶片组(1994年)。R8000的设计始于硅谷图形公司,它仅用于高端工作站和伺服器,用于高性能浮点工作负载关键的科学和技术应用。后来的实现是MIPS科技的R10000(1996年),Quantum Effect Devices的R5000(1996年)和RM7000(1998年)。NEC和东芝制造和销售的R10000及其派生产品被NEC、Pyramid Technology、SGI和Tandem Computers(以及其他公司)用于工作站、伺服器和超级计算机。R5000和R7000可用于高端嵌入式系统、个人电脑以及低端工作站和伺服器。东芝R5000的派生产品R5900用于索尼的Emotion Engine,该引擎为其PlayStation 2游戏机提供动力。

MIPS V于1996年10月21日在微处理器论坛上与MIPS数码媒体扩展(MDMX)扩展一起发布,旨在提高3D图形变换的性能[11]。在1990年代中期,非嵌入式MIPS微处理器的主要用途是SGI的图形工作站。MIPS V使用仅整数的MDMX扩展,以此提高3D图形应用程式的性能[12]。MIPS V从未真正实现。1997年5月12日,SGI发布了“H1”(“野兽”)和“H2”(“船长”)微处理器。前者计划是第一个MIPS V实现,预计于1999年上半年推出[13]。“H1”和“H2”项目后来合并,最终在1998年取消。虽然没有任何MIPS V实现,但MIPS64 Release 1(1999年)基于MIPS V并保留其所有功能作为可选的协处理器1(FPU)功能,称为配对单精度(Paired-Single)。

当MIPS科技公司于1998年从SGI分拆出来时,它重新专注于嵌入式市场。直到MIPS V,每个后续版本都是前一个版本的严格超集,但是发现这是一个问题[来源请求],随后架构更改为分别定义32位和64位:MIPS32和MIPS64。两者都于1999年推出[14]。MIPS32基于MIPS II,,并带有MIPS III、MIPS IV和MIPS V的一些附加特性;MIPS64基于MIPS V[14]。NEC、东芝和SiByte(后来被博通收购)在MIPS64发布后都获得了许可证。飞利浦、LSI Logic、IDT、Raza Microelectronics, Inc.、凯为、龙芯和君正已加入其中。MIPS32/MIPS64 Release 5于2012年12月6日发布[15]。第4版被跳过,因为在许多亚洲文化中,数字4被认为是不吉利的[16]。

2018年6月—美国硅谷新创AI晶片公司Wave Computing宣布完成收购MIPS公司股权,MIPS公司维持独立运作,并预计开源MIPS架构[17]。

2018年12月,MIPS架构的新所有者Wave Computing宣布MIPS ISA将在一个名为MIPS开放计划的项目中开源[18]。该计划旨在开放对32位和64位设计的最新版本的访问,使其无需任何许可或版税即可使用,并授予参与者现有MIPS专利的许可[19][20][21]。

2019年3月,该架构的一个版本在免版税许可下可用[22],但该年晚些时候该程序再次关闭[23]。

2021年3月,WaveComputing宣布停止MIPS架构的开发。该公司已加入RISC-V基金会,未来的处理器设计将基于RISC-V架构[24][25]。

设计

此章节需要扩充。 (2020年2月) |

MIPS是一种模块化架构,最多支持四个协处理器(CP0/1/2/3)。在MIPS术语中,CP0是系统控制协处理器(MIPS I-V中处理器的重要部分,与实现相关),CP1是可选的浮点运算器(FPU),CP2/3是可选的由实现定义的协处理器(MIPS III删除了CP3并将其操作码重新用于其他目的)。例如,在PlayStation视频游戏机中,CP2是几何变换引擎(GTE),它可以加速3D电脑图形中的几何处理。

版本

MIPS是一种加载-存储架构(也称为寄存器-寄存器架构);除了用于访问电脑存储器的加载/存储指令外,所有指令都对寄存器进行操作。

MIPS I有32个32位通用寄存器(GPR)。寄存器$0硬编码为零,写入的内容将被丢弃。寄存器$31是链接寄存器。对于与其他指令异步运行的整数乘法和除法指令,提供了一对32位寄存器HI和LO。有一小组指令用于在通用寄存器和HI/LO寄存器之间复制数据。

程序计数器(PC)有32位。低二位总是为零,因为MIPS I指令有32位长,并且与它们的自然字边界对齐。

指令分为三种类型:R型(Register)、I型(Immediate)和J型(Jump)。三种类型的指令的最高6位均为6位的opcode码。从25位往下,

- R型指令用连续三个5位二进制码来表示三个寄存器的地址,然后用一个5位二进制码来表示移位的位数(如果未使用移位操作,则全为0),最后为6位的function码(它与opcode码共同决定R型指令的具体操作方式);

- I型指令则用连续两个5位二进制码来表示两个寄存器的地址,然后是一个16位二进制码来表示的一个立即数二进制码;

- J型指令用26位二进制码来表示跳转目标的指令地址(实际的指令地址应为32位,其中最低两位为00)。[26][27][28]:82—83, 113

三种用于核心指令集的指令图示如下:

| 类型 | 位 | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| R | opcode (6) | rs (5) | rt (5) | rd (5) | shamt (5) | funct (6) | ||||||||||||||||||||||||||

| I | opcode (6) | rs (5) | rt (5) | immediate (16) | ||||||||||||||||||||||||||||

| J | opcode (6) | address (26) | ||||||||||||||||||||||||||||||

MIPS I有加载和存储8位的字节、16位的半字和32位的字的指令。仅支持一种寻址模式:基址+位移。由于MIPS I是32位架构,因此加载少于32位的值需要将数据有符号或无符号扩展到32位。以“unsigned”为后缀的加载指令执行无符号扩展;否则执行有符号扩展。加载指令从GPR(rs)的内容中获取基址,并将结果写入另一个GPR(rt)。存储指令从GPR(rs)的内容中获取基址,从另一个GPR(rt)获取存储数据。所有加载和存储指令都通过将基址与符号扩展的16位立即数相加来计算内存地址。MIPS I要求所有内存访问都与其自然字边界对齐,否则会发出异常信号。“左”或“右”为后缀的加载/存储字指令用以支持高效的未对齐内存访问。所有加载指令后都有一条指令的加载延迟槽。加载延迟槽中的指令不能使用加载指令加载的数据。加载延迟槽可以填充一条不依赖于加载的指令;如果找不到这样的指令,则用nop代替。

MIPS I有执行加法和减法的指令。这些指令从两个GPR(rs和rt)获取它们的操作数,并将结果写入第三个GPR(rd)。此外,加法可以从16位立即数(有符号扩展为32位)中获取操作数之一。加减法指令有两种变体:默认情况下,如果结果溢出则发出异常信号;带有“unsigned”后缀的指令不会发出异常信号。溢出检查将结果解释为32位二进制补码整数。MIPS I有执行按位逻辑AND、OR、XOR和NOR的指令。这些指令从两个GPR获取其操作数并将结果写入第三个GPR。AND、OR和XOR指令也可以从16位立即数(无符号扩展到32位)中获取操作数之一。如果指定的关系为真或假,则Seton关系指令将1或0写入目标寄存器。这些指令的操作数来自两个GPR或一个GPR和一个16位立即数(符号扩展为32位),并将结果写入第三个GPR。默认情况下,操作数被解释为有符号整数。以“unsigned”为后缀的指令的变体将操作数解释为无符号整数(即使是对于来自有符号扩展16位立即数的操作数)。

Load Immediate Upper指令将16位立即数复制到GPR的高16位。它与Or Immediate指令结合使用以将32位立即数加载到寄存器中。

MIPS I有执行左右逻辑移位和右算术移位的指令。操作数从一个GPR(rt)中获得,并将结果写入另一个GPR(rd)。位移距离是从GPR(rs)或5位“位移量”(“sa”字段)中获得的。

MIPS I有有符号和无符号整数乘法和除法的指令。这些指令从两个GPR获取其操作数,并将其结果写入一对称为HI和LO的32位寄存器,因为它们可能与其他CPU指令分开(并同时)执行。对于乘法,64位乘积的高位和低位分别写入HI和LO。对于除法,商写入LO,余数写入HI。为了访问结果,提供了一对指令(从HI移动和从LO移动)将HI或LO的内容复制到GPR。这些指令是互锁的:对HI和LO的读取不会越过未完成的要写入HI和LO的算术指令。另一对指令(Move to HI或Move to LO)将GPR的内容复制到HI和LO。这些指令用于在异常处理后将HI和LO恢复到其原始状态。读取HI或LO的指令必须由不写入HI或LO的两条指令分隔。

所有MIPS I控制流指令后需要接一个分支延迟槽。除非分支延迟槽用执行有用工作的指令填充,否则要使用nop。MIPS I分支指令将GPR(rs)的内容与零或另一个GPR(rt)的内容作为有符号整数进行比较,如果指定的条件为真,则跳转分支。执行位置将转移到通过将16位偏移量左移两位、对18位结果进行有符号扩展,并将32位符号扩展结果与程序计数器(指令地址)和810作和得到。跳转有两个版本:绝对跳转和寄存器间接跳转。绝对跳转(“Jump”和“Jump and Link”)通过将26位instr_index左移两位,并将28位结果与分支延迟槽指令的指令地址高四位连接来计算跳转的地址。寄存器间接跳转将控制转移到来自GPR(rs)的地址处的指令。来自GPR的地址必须是字对齐的,否则在执行分支延迟槽中的指令后会发出异常信号。链接的分支和跳转指令(“Jump and Link Register”除外)将返回地址保存到GPR 31。“Jump and Link Register”指令允许将返回地址保存到任何可写的GPR。

MIPS I有两条软件用于发出异常信号的指令:System Call和Breakpoint。System Call被用户态软件用来进行内核调用;Breakpoint用于内核异常处理程序转移控制到调试器。两条指令都有一个20位的代码(Code)字段,可存储给异常处理程序的操作环境特定资讯。

MIPS有32个浮点寄存器。两两寄存器配对用于双精度数。奇数号寄存器不能用于算术或分支,只是作为双精度寄存器对的一部分,导致大多数指令只有16个可用寄存器(移动/复制和加载/存储不受影响)。

单精度指令由.s后缀表示,而双精度由.d后缀表示。

MIPS II移除了加载延迟槽[3]:41并添加了几组指令。对于共享内存多处理,添加了“Synchronize Shared Memory”、“Load Linked Word”和“Store Conditional Word”指令。添加了一组Trap-on-Condition指令。如果求值为真,这些指令将导致异常。所有现有的分支指令都有了“可能”分支的版本,仅在分支跳转要执行时才执行分支延迟槽中执行指令[3]:40。在某些情况下,这些指令允许用有用的指令填充分支延迟槽,以此提高性能[3]:212。为COP1-3添加了双字加载和存储指令。与其他内存访问指令一致,这些加载和存储要求双字自然对齐。

浮点协处理器指令集也添加了几条指令。添加了符合IEEE 754的浮点平方根指令。它支持单精度和双精度操作数。添加了一组将单精度和双精度浮点数转换为32位字的指令。它们补充了现有的转换指令,允许用指令控制IEEE舍入模式,而不是通过浮点控制和状态(Floating Point Control and Status)寄存器。

MIPS III是向后兼容MIPS II的扩展,增加了对64位内存寻址和整数运算的支持。64位数据类型称为双字,MIPS III将通用寄存器、HI/LO寄存器和程序计数器扩展到64位以支持。添加了新指令来加载和存储双字,对它们执行整数加、减、乘、除和移位运算,以及在GPR和HI/LO寄存器之间移动双字。必要时,现有最初定义为对32位字进行操作的指令被重新定义,以对32位结果进行符号扩展,使得大多数指令对字和双字进行的处理行为相同。在这些重新定义的指令中包括“Load Word”。在MIPS III中,它将字有符号扩展到64位。为了补充“Load Word”,添加了一个无符号扩展版本。

R指令格式无法指定完整的64位位移距离(其5位位移量字段太窄,无法指定双字的位移距离),MIPS III对于每个MIPS I的位移指令,提供了三个64位的版本。第一个版本是原始移位指令的64位版本,用于指定介于0-31位之间的常量位移距离。第二个版本与第一个版本类似,但将位移量字段的值加上3210,以便可以指定32-64位之间的常量位移距离。第三个版本从GPR的六个低位获取位移距离。

MIPS III在现有内核和用户权限级别之间添加了一个“管理员”权限级别。此功能仅影响由实现定义的系统控制处理器(协处理器0)。

MIPS III移除了协处理器3(CP3)相关支持指令,并为新的双字指令重新使用了其操作码。其余的协处理器获得了在协处理器寄存器和GPR之间移动双字的指令。浮点通用寄存器(FGR)扩展到64位,并且取消了指令仅使用偶数寄存器的要求。这与早期版本的架构不兼容;浮点控制/状态寄存器中的一位用于在MIPS I和II兼容模式下操作MIPS III浮点单元(FPU)。浮点控制寄存器没有为兼容性进行扩展。添加的唯一新浮点指令是在CPU和FPU之间复制双字的指令,将单精度和双精度浮点数转换为双字整数,反之亦然。

MIPS IV是该架构的第四个版本。它是MIPS III的超集,与MIPS的所有现有版本兼容。MIPS IV主要旨在提高浮点(FP)性能。为了改进对操作数的访问,添加了用于FP加载和存储的索引寻址模式(基址+索引,均来自GPR),以及用于执行内存预取和指定缓存提示的预取指令(这些指令同时支持基址+偏移量和基址+索引寻址模式)。

MIPS IV添加了几个特性来改进指令级并行性。为了缓解由单个条件位引起的瓶颈,在浮点控制和状态寄存器中添加了七个条件代码位,使总数达到八个。重新定义了FP比较和分支指令,以便它们可(分别)指定写入或读取哪个条件位;并且删除了FP比较与读取由比较指令写入条件位的FP分支之间的延迟槽。通过GPR和FPR条件移动指令的形式部分添加了对分支预测的支持;并且实现可以选择为IEEE 754陷阱提供精确或不精确的例外。

MIPS IV为单精度和双精度浮点数添加了几个新的浮点算术指令:融合乘加减、倒数和倒数平方根。FP融合乘加减指令执行一次或两次舍入(由实现定义),(分别)超过或达到IEEE 754精度要求。FP倒数和倒数平方根指令不符合IEEE 754精度要求,并且产生的结果与所需精度相差一到两个单位(它是实现定义的)。这些指令服务于指令延迟比准确性更重要的应用程式。

MIPS V添加了一种新的数据类型,配对单精度(PS),它由两个单精度(32位)浮点数组成,存储在现有的64位浮点寄存器中。添加了现有算术、比较和条件移动浮点指令的变体,以便以SIMD方式对这种数据类型进行操作。添加了用于加载、重排和转换PS数据的新指令[3]:426–429。这是第一个利用现有资源实现的浮点SIMD指令集[12]。

MIPS32的第一个版本基于MIPS II,添加了来自R4000和R5000系列64位处理器的条件移动、预取指令和其他特性[14]。MIPS64的第一个版本增加了一个MIPS32模式来运行32位代码[14]。向MIPS32和MIPS64规范添加了以前在某些实现中可用的MUL和MADD(乘加)指令,同样的还有缓存控制指令[14]。

2014年的MIPS32/MIPS64 Release 6添加了以下内容:[29]

- 一个没有延迟槽的新分支家族:

- 具有26位偏移量的无条件分支(BC)和分支链接(BALC),

- 具有21位偏移量的零/非零条件分支,

- 全套有符号和无符号条件分支,可比较两个寄存器(例如BGTUC)或一个寄存器与零(例如BGTZC),

- 全套分支和链接,将寄存器与零进行比较(例如BGTZALC)。

- 无延迟槽的索引跳转指令,旨在支持大绝对地址。

- 在第16、32或48位处加载16位立即数的指令,允许轻松生成大常量。

- PC相关加载指令,以及大(PC相关)偏移量的地址生成。

- 位反转和字节对齐指令(以前仅适用于DSP扩展)。

- 乘法和除法指令重新定义,向单个寄存器输出结果。

- 生成真值的指令现在生成全零或全一,而不仅仅是清除/设置0位,

- 使用真值的指令现在只将全零解释为假,而不是只看0位。

删除了不常用的指令:

- 一些条件移动

- “可能”分支指令(在以前的版本中已弃用)。

- 具有16位立即数的整数溢出捕获指令

- 整数累加器指令(连同HI/LO寄存器,移至DSP特定应用扩展)

- 未对齐的加载指令(LWL和LWR)(现要求大多数一般加载和存储指令支持未对齐的访问,通过陷阱或添加新指令(BALIGN)等形式)

重新组织指令编码,为未来的扩展腾出空间。

microMIPS32/64架构(分别)是MIPS32和MIPS64架构的超集,旨在取代MIPS16e ASE。MIPS16e的一个缺点是在处理任何16位指令之前需要切换模式。microMIPS将最常用的32位指令编码为16位指令版本。允许程序混合16位和32位指令而无需切换模式。microMIPS与MIPS32/64 Release 3一起推出,MIPS32/64的每个后续版本都有相应的microMIPS32/64版本。处理器可以单独实现microMIPS32/64,或同时实现microMIPS32/64及其相应的MIPS32/64子集。从MIPS32/64 Release 6开始,对MIPS16e的支持结束,microMIPS是MIPS中唯一的代码压缩形式。

应用程式特定扩展

基本的MIPS32和MIPS64架构可以补充一些可选的架构扩展,这些扩展统称为“应用程式特定扩展”(ASE)。这些ASE提供的功能可以提高某些工作负载的效率和性能,例如数码信号处理。

- MIPS单片机

- 微控制器应用的增强功能。MCU ASE(特定应用扩展)用于扩展中断控制器支持、减少中断延迟并增强微控制器系统设计中通常需要的I/O外设控制功能。

- 单独的优先级和矢量生成

- 在EIC(外部中断控制器)模式下支持多达256个中断和8个硬件中断引脚

- 提供16位向量偏移地址

- 中断异常向量预取

- 自动中断序言——添加硬件以在中断处理例程之前保存和更新系统状态

- 自动中断尾声——恢复先前存储在堆栈中的系统状态,以便从中断返回。

- 中断链——支持挂起中断的服务,无需退出初始中断例程,节省存储和恢复多个活动中断所需的周期

- 支持推测性预取中断向量地址。通过将内存访问与管道刷新和异常优先级重叠来减少中断服务周期数

- 原子性位设置/清除指令,通常可在不中断的情况下修改I/O寄存器中用于监视或控制外部外围功能的位,确保安全地执行操作。

- MIPS16

- MIPS16是从MIPS I到V的特定应用扩展,由LSI Logic和MIPS科技设计,于1996年10月21日与其第一个实现LSI Logic TinyRISC处理器一起发布[30]。随后NEC电子、飞利浦半导体、东芝以及其他公司获得了MIPS16的许可,并作为MIPS I、II、III架构的扩展实现。MIPS16使用16位指令而不是32位指令,减少应用程式的大小多达40%,并且还提高了电源效率、指令缓存命中率,并且在性能方面与其基础架构相当[31]。它由MIPS科技和其他供应商的硬件和软件开发工具提供支持。MIPS16e是MIPS16的改进版本,首先由MIPS32和MIPS64 Release 1支持。MIPS16e2是MIPS16的改进版本,由MIPS32和MIPS64(直到Release 5)支持。Release 6将其替换为microMIPS。

- MIPS数码信号处理(DSP)

- DSP ASE是MIPS32/MIPS64 Release 2及更新指令集版本的可选扩展,可用于加速大量“媒体”计算——尤其是音视频。DSP模块包含整数流水线中的一组指令和状态,并且在MIPS处理器内核中实现所需的附加逻辑最少。ASE修订版2于2006年下半年推出。该修订版向原始ASE添加了额外的指令,但在其他方面与它向后兼容[32]。与MIPS架构的大部分不同,它是一组相当不规则的操作,其中许多是为了某些关键算法特别选择的。其主要新颖特点(对比原始MIPS32)[33]:

- 饱和算术(当计算溢出时,提供最接近非溢出答案的可表示数字)。

- 有符号32位和16位定点小数的定点运算,范围为-1到+1(广泛称为“Q31”和“Q15”)。

- 现有的整数乘法与乘法累加指令,将结果传送到双倍大小的累加器(在MIPS32 CPU上称为“hi/lo”和64位)。DSP ASE增加了三个累加器,以及一些不同风格的乘法累加。

- SIMD指令在4x无符号字节或2x16位值上运行,这些值打包到一个32位寄存器(DSP ASE的64位变体也支持更大的向量)。

- SIMD操作是基本算术、移位和一些乘法累加类型的操作。

- MIPS SIMD架构(MSA)

- 旨在加速多媒体的指令集扩展。

- 32个16x8位、8x16位、4x32位和2x64位向量元素的向量寄存器

- 高效的整数、定点和浮点数向量并行算术运算

- 对绝对值操作数的操作

- 可用的舍入和饱和选项

- 全精度乘法和乘加

- 整数、浮点和定点数据之间的转换

- 完整的向量级比较和分支指令集,无条件标志

- 向量(1D)和数组(2D)打散操作

- 字节序无关的有类型加载和存储指令

- 符合IEEE 754-2008浮点运算标准

- 基本精确浮点异常信号

- 用于有更多门/晶体管的晶片的预定义可扩展扩展

- 结合通用编译器加速计算密集型应用程式

- 用于消费电子应用或专用硬件未涵盖的功能的软件可编程解决方案

- 新兴的数据挖掘、特征提取、图像和视频处理以及人机交互应用

- 高性能科学计算

- MIPS虚拟化

- 硬件支持的虚拟化技术。

- MIPS多线程

- 每个多线程MIPS内核最多可以支持两个VPE(虚拟处理元素),它们共享单个管道以及其他硬件资源。但是,由于每个VPE都包含软件系统所看到的处理器状态的完整副本,因此每个VPE对于SMP Linux操作系统来说都是一个完整的独立处理器。对于更细粒度的线程处理应用程式,每个VPE能够支持多达9个跨两个VPE分配的TC。TC共享一个公共执行单元,但每个都有自己的程序计数器和核心寄存器文件,因此每个都可以处理来自软件的线程。MIPS MT架构还允许将处理器周期分配给线程,并使用可选的服务质量(QoS)管理块设置相关线程的优先级。这样有两个决定跨总线资讯流的优先级机制。第一种机制允许用户优先一个线程于另一个线程。第二种机制用于随时间将指定比例的周期分配给特定线程。两种机制的结合使用允许向线程集有效分配带宽,并更好地控制延迟。在实时系统中,系统级确定性非常重要,而QoS块有助于提高系统的可预测性。高级系统的硬件设计人员可以用专门针对其应用进行调整的模块来替换MIPS科技提供的标准QoS模块。

- SmartMIPS

- SmartMIPS是由Gemplus International和MIPS科技设计的特定于应用程式的扩展(ASE),旨在提高智慧卡软件的性能并减少内存消耗。它仅受MIPS32支持,因为智慧卡不需要MIPS64处理器的功能。很少有智慧卡使用SmartMIPS。

- MIPS数码媒体扩展(MDMX)

- 1990年代常见于RISC和CISC系统上的多媒体应用程式加速。

- MIPS-3D

- 提高3D图形应用程式性能的附加指令

调用约定

MIPS有几个调用约定,尤其是在32位平台上。

O32 ABI是最常用的ABI,因为它是MIPS的原始System V ABI[34][35]。它严格基于堆栈,只有四个寄存器$a0-$a3可用于传递参数。堆栈上的空间是保留的,以防被调用者需要保存其参数,但调用者不会将寄存器存储在那里。返回值存储在寄存器$v0中;第二个返回值可以存储在$v1中。ABI形成于1990年,最后一次更新是在1994年。这种肉眼可见的缓慢,以及只有16个寄存器的老式浮点模型,促进了许多其他调用约定的扩散。它仅针对32位MIPS定义,但GCC创建了一个名为O64的64位变体[36]。

对64位,最常用的是SGI的N64 ABI。最重要的改进是现有八个寄存器可用于参数传递;它还将浮点寄存器的数量增加到32个。还有一个称为N32的ILP32版本,它使用32位指针来处理较小的代码,类似于x32 ABI。两者都在CPU的64位模式下运行[36]。N32和N64 ABI将前八个参数传递给寄存器$a0-$a7中的函数;后续参数在堆栈上传递。返回值(或指向它的指针)存储在寄存器$v0中;第二个返回值可以存储在$v1中。在N32和N64 ABI中,所有寄存器都被认为是64位宽。

已有一些尝试,使用更类似于N32的32位ABI替换O32。1995年的一次会议提出了MIPS EABI,其32位版本非常相似[37]。EABI启发MIPS科技提出更激进的“NUBI”ABI,重用参数寄存器作为返回值[38]。GCC支持MIPS EABI,但LLVM不支持,两者也不支持NUBI。

对于O32及N32/N64,返回地址存储在$ra寄存器中。这是使用JAL(跳转和链接)或JALR(跳转和链接寄存器)指令自动设置的。(非叶子)MIPS子例程的函数序言将返回地址(在$ra中)推入堆栈[39][40]。

在O32和N32/N64上,堆栈向下增长,但N32/N64 ABI需要所有堆栈条目64位对齐。帧指针($30)是可选的,实际上很少使用,除非需要在运行时确定函数中的堆栈分配,例如调用了alloca()。

对于N32和N64,返回地址通常存储在栈指针之前的8个字节,尽管这可能是可选的。

对于N32和N64 ABI,函数必须保留$S0-$s7寄存器、全局指针($gp或$28)、栈指针($sp或$29)和帧指针($30)。O32 ABI相同,只是$gp寄存器需要由调用函数保存而不是被调用函数。

对于多线程代码,线程本地存储指针通常存储在特殊硬件寄存器$29中,并通过使用mfhw(从硬件移动)指令访问。已知至少有一个供应商将此资讯存储在$k0寄存器中,该寄存器通常保留供内核使用,但这不是标准的。

$k0和$k1寄存器($26-$27)保留供内核使用,不应由应用程式使用,因为内核可以随时由于中断、上下文切换或其他事件而更改这些寄存器。

| 名称 | 编号 | 用途 | 被调保留? |

|---|---|---|---|

| $zero | $0 | 常量0 | 不适用 |

| $at | $1 | 汇编临时用 | 否 |

| $v0–$v1 | $2–$3 | 函数返回值和表达式求值 | 否 |

| $a0–$a3 | $4–$7 | 函数参数 | 否 |

| $t0–$t7 | $8–$15 | 临时 | 否 |

| $s0–$s7 | $16–$23 | 临时保存值 | 是 |

| $t8–$t9 | $24–$25 | 临时 | 否 |

| $k0–$k1 | $26–$27 | 保留内核用 | 不适用 |

| $gp | $28 | 全局指针 | 是(除PIC代码) |

| $sp | $29 | 栈指针 | 是 |

| $fp | $30 | 帧指针 | 是 |

| $ra | $31 | 返回地址 | 不适用 |

跨调用保留的寄存器是(按照约定)不会被系统调用或过程(函数)调用更改的寄存器。例如,$s-寄存器必须由需要使用它们的过程保存到堆栈中,而$sp和$fp总是按常量递增,并在过程完成后递减(以及它们指向的内存)。相比之下,$ra由任何普通函数调用(使用jal的函数调用)自动更改,并且$t-寄存器必须在任何过程调用之前由程序保存(如果程序在调用后需要其中的值)。

Linux上位置无关代码的用户空间调用约定还要求,当调用函数时,$t9寄存器必须包含该函数的地址[42]。这个约定可以追溯到MIPS的System V ABI补充规定[43]。

用途

此章节需要扩充。 (2020年2月) |

MIPS处理器用于嵌入式系统,例如住宅网关和路由器。最初,MIPS是为通用计算而设计的。在1980年代和1990年代,许多公司在个人、工作站和伺服器电脑上使用MIPS处理器,例如DEC、MIPS Computer Systems、NEC、Pyramid Technology、SiCortex、Siemens Nixdorf、SGI和Tandem Computers。

从历史上看,任天堂64、PlayStation、PlayStation 2和PlayStation Portable等电子游戏机都使用MIPS处理器。MIPS处理器在1990年代也曾在超级计算机中流行,但所有此类系统都从TOP500名单中掉了下来。这些用途最初由嵌入式应用程式补充,但在1990年代,MIPS成为嵌入式处理器市场的主流选择,到2000年代,大多数MIPS处理器都用于这类应用。

在1990年代中后期,据估计生产的RISC微处理器中有三分之一是MIPS处理器[44]。

到2010年代后期,MIPS机器仍然普遍用于嵌入式市场,包括汽车、无线路由器、LTE调制解调器(主要为联发科)和微控制器(例如PIC32M)。它们大多已淡出个人、伺服器和应用领域。

模拟器

开放虚拟平台(OVP)[45]包括可免费用于非商业用途的模拟器OVPsim、处理器模型库、外围装置和平台,以及使用户能够开发自己的模型的API。库中的模型是用C语言编写的开源模型,包括MIPS4K、24K、34K、74K、1004K、1074K、M14K、microAptiv、interAptiv、proAptiv 32位内核和MIPS64位5K系列内核.这些模型由Imperas[46]创建和维护,并与MIPS技术公司合作进行了测试,并得到了MIPS验证标记。基于MIPS的示例平台包括裸机环境和用于引导未修改的Linux二进制映像的平台。这些平台模拟器可作为原始码或二进制文件使用,速度快,非商业用途免费,并且易于使用。OVPsim由Imperas开发和维护,速度非常快(每秒数亿条指令),旨在处理多核同构和异构架构和系统。

有一个免费的MIPS32模拟器(早期版本仅模拟R2000/R3000)称为SPIM,用于教育。EduMIPS64[47]是一个GPL图形跨平台MIPS64CPU模拟器,用Java/Swing编写。它支持MIPS64 ISA的较大子集,并允许用户以图形方式查看CPU运行汇编程序时流水线中发生的情况。

MARS[48]是另一个基于GUI的MIPS仿真器,设计用于教育,特别是与Hennessy的《电脑组织和设计》一起使用。

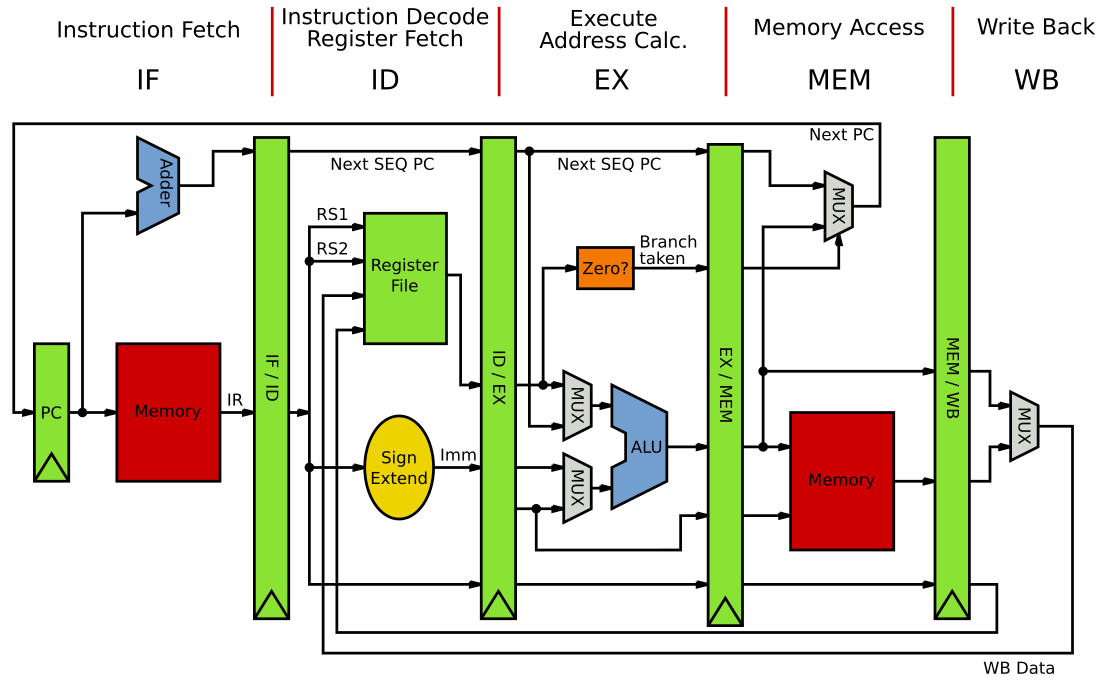

WebMIPS[49]是一个基于浏览器的MIPS模拟器,具有通用流水线处理器的可视化表示。该模拟器对于逐步执行期间的寄存器跟踪非常有用。

QtMips[50][51][52]为基础电脑架构课程提供简单的5阶段管道可视化以及缓存原理可视化。提供Windows、Linux、macOS和在线版本。

GXemul(以前称为mips64emul项目)和QEMU项目提供了更高级的免费模拟器。除了使用它们的整个电脑系统之外,它们还模拟各种MIPS III和IV微处理器。

商业模拟器特别适用于MIPS处理器的嵌入式使用,例如Wind River Simics(MIPS 4Kc和5Kc、PMC RM9000、QED RM7000、Broadcom/Netlogic ec4400、Cavium Octeon I)、Imperas(所有MIPS32和MIPS64内核)、VaST系统(R3000、R4000)和CoWare(MIPS4KE、MIPS24K、MIPS25Kf和MIPS34K)。

WepSIM[53]是一个基于浏览器的模拟器,其中MIPS指令的子集是微编程的。该模拟器对于学习CPU的工作方式(微编程、MIPS例程、陷阱、中断、系统调用等)非常有用。

参见

参考文献

扩展阅读

外部链接

Wikiwand - on

Seamless Wikipedia browsing. On steroids.