IBM POWER指令集架构

维基百科,自由的 encyclopedia

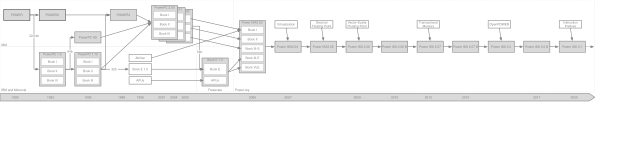

IBM POWER指令集架构是由IBM公司开发的一种精简指令集电脑(RISC)指令集架构(ISA)。该名称是“增强RISC性能优化”(Performance Optimization With Enhanced RISC)的首字母缩略字[1]。

参考资料

- Bakoglu, H. B.; Grohoski, G. F.; Montoye, R. K. The IBM RISC System/6000 processor: Hardware overview. IBM Journal of Research and Development. January 1990, 34 (1): 12–22. doi:10.1147/rd.341.0012.

延伸阅读

- Weiss, Shlomo; Smith, James Edward. POWER and PowerPC. Morgan Kaufmann. 1994. ISBN 978-1558602793. — Relevant parts: Chapter 1 (the POWER architecture), Chapter 2 (how the architecture should be implemented), Chapter 6 (the additions introduced by the POWER2 architecture), Appendixes A and C (describes all POWER instructions), Appendix F (describes the differences between the POWER and PowerPC architectures)

- Dewar, Robert B.K.; Smosna, Matthew. Microprocessors: A Programmer's View

. McGraw-Hill. 1990. 含有内容需登录查看的页面 (link) — Chapter 12 describes the POWER architecture (referred to as RIOS, its earlier name) and its origins

. McGraw-Hill. 1990. 含有内容需登录查看的页面 (link) — Chapter 12 describes the POWER architecture (referred to as RIOS, its earlier name) and its origins

| 这是一篇与计算机相关的小作品。您可以通过编辑或修订扩充其内容。 |