ARM Cortex-M是ARM架構處理器核心中,低階系列的統稱,由安謀控股所授權。這組核心的特點為低成本以及高能源效率的微處理器而最佳化設計,已有上千萬個消費性裝置中有此系列的微處理器[1]。此系列核心包括Cortex-M0、Cortex-M0+、Cortex-M1、Cortex-M3、Cortex-M4、Cortex-M7、Cortex-M23、Cortex-M33、Cortex-M35P和Cortex-M55。其中Cortex-M4 / M7 / M33 / M35P / M55 核心有浮點運算器的選項,若有浮點運算器的選項,會在型號後面說明,例如Cortex-Mx with FPU或Cortex-MxF,其中x是核心編號。

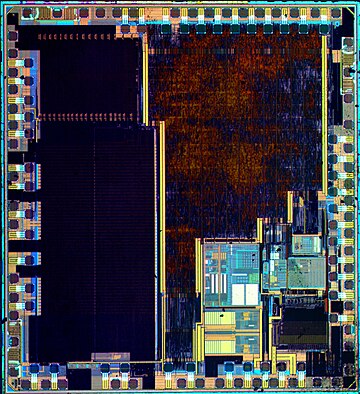

24 MHz ARM Cortex-M3 單晶片,有16千位元組快閃記憶體,4 KB RAM。由意法半導體生產

簡介

| 32-bit | |

|---|---|

| 年份 | 核心 |

| 2004年 | Cortex-M3 |

| 2007年 | Cortex-M1 |

| 2009年 | Cortex-M0 |

| 2010年 | Cortex-M4 |

| 2012年 | Cortex-M0+ |

| 2014年 | Cortex-M7 |

| 2016年 | Cortex-M23 |

| 2016年 | Cortex-M33 |

| 2018年 | Cortex-M35P |

| 2020年 | Cortex-M55 |

ARM Cortex-M系列是為了單晶片、特殊應用集成電路(ASIC)、應用專門標準產品(ASSP)、現場可程式化邏輯門陣列(FPGA)及單晶片系統(SoC)設計的ARM微處理器核心。Cortex-M核心常用在 專用微控制器晶片中,但也會藏在SoC晶片中,例如電源管理制器、輸入/輸出控制器、系統控制器、觸碰螢幕控制器、智能電池控制器以及感測器控制器。

以往8位元的微控制器相當流行,但低階的Cortex-M晶片已經降價,佔據了一些8位元微控制器的市場。在取代8位元微控制器時,Cortex-M是常出現的選項,因為有32位元數學運算上的優勢,也會用來替換一些較舊的ARM核心 ,例如ARM7及ARM9。

安謀控股不會以其自身的技術生產CPU或販售CPU,而是其將處理器的架構授權給其他有意願開發的公司。安謀有許多不同的授權條款,差異在成本以及可交付成果。對於所有的授權,安謀都會提出一份可整合的ARM核心硬件描述,也包括完整的軟件開發工具組,以及販售包括ARM CPU在內的集成電路的權利。

整合元件製造廠(IDM)收到的ARM處理器知識產權,是可邏輯綜合的暫存器傳輸級(用Verilog所寫)。以此型式,整合元件製造商可以進行架構層級的最佳化以及延伸,可以讓製造商達成其客戶的設計目的,例如高時脈速度、非常低的能耗、指令集延伸(包括浮點數)、針對大小的最佳化、除錯器的支援等。若要確認特定的ARM CPU晶片中已有那些功能,則需確認製造商的資料表以及相關檔案。

Cortex-M核心的部份選配機能如下:

- SysTick計時器:24位元的系統計時器,延伸了處理器以及巢狀向量中斷控制器(Nested Vectored Interrupt Controller、NVIC)的機能。若有此計時器,也可以提供額外的SysTick中斷,可以組態其優先權[2][3][4]。雖然SysTick計時器不是必備的,不過幾乎沒有不支援SysTick的Cortex-M微處理器。若Cortex-M33控制器有安全擴展(Security Extension)選項,會有二個SysTicks,一個是安全的,另一個是一般的。

- 位元帶(Bit-Band):位元帶區域內記憶體中的每一個位元,可以個別對映到一個字元組。例如,寫入特定的假名字元組,就代表設置或是清除位元帶區域內特定的位元。因此位元帶區域內的每一個位元都可以透過字元組對齊的地址來直接讀寫。而且,每一個位元都可以用C/C++進行設置、清除、反相等功能,不需要透過一連串畗讀取-修改-寫入的指令順序[2][3][4]。位元帶也不是Cortex-M一定會有的功能,不過不支援位元帶的Cortex-M3或Cortex-M4微處理器較不常見。有些Cortex-M0及Cortex-M0+微處理器也會有位元帶。

- 記憶體保護單元(MPU):透過強制的權限以及存取規則,可以保護特定區域的記憶體。最多可以支援八個不同的記憶體區域,每個還可以分成八個等大小的子區域[2][3][4]。

- 緊密耦合記憶體(Tightly-Coupled Memory、TCM):是低延遲的RAM,可以儲存關鍵性的程式、資料及堆疊。緊密耦合記憶體一般會是微處理器中最快的RAM,僅次於快取記憶體。

| ARM Core | Cortex M0[5] |

Cortex M0+[6] |

Cortex M1[7] |

Cortex M3[8] |

Cortex M4[9] |

Cortex M7[10] |

Cortex M23[11] |

Cortex M33[12] |

Cortex M35P |

|---|---|---|---|---|---|---|---|---|---|

| SysTick 24位元計時器 | 選配 (0,1) |

選配 (0,1) |

選配 (0,1) |

是 (1) |

是 (1) |

是 (1) |

選配 (0,1,2) |

是 (1,2) |

是 (1,2) |

| 單週期I/O埠 | 否 | 選配 | 否 | 否 | 否 | 否 | 選配 | 否 | 否 |

| 位元帶記憶體 | 否[13] | 否[13] | 否* | 選配 | 選配 | 選配 | 否 | 否 | 否 |

| 記憶體保護單元 (MPU) |

否 | 選配 (0,8) |

否 | 選配 (0,8) |

選配 (0,8) |

選配 (0,8,16) |

選配 (0,4,8,12,16) |

選配 (0,4,8,12,16) |

選配 * |

| 安全屬性單元(SAU) 及堆疊限制 |

否 | 否 | 否 | 否 | 否 | 否 | 選配 (0,4,8) |

選配 (0,4,8) |

選配 * |

| 指令TCM | 否 | 否 | 選配 | 否 | 否 | 選配 | 否 | 否 | 否 |

| 資料TCM | 否 | 否 | 選配 | 否 | 否 | 選配 | 否 | 否 | 否 |

| 指令快取 | 否[14] | 否[14] | 否[14] | 否[14] | 否[14] | 選配 | 否 | 否 | 選配 |

| 資料快取 | 否[14] | 否[14] | 否[14] | 否[14] | 否[14] | 選配 | 否 | 否 | 否 |

| 向量表位移暫存器 (VTOR) |

否 | 選配 (0,1) |

選配 (0,1) |

選配 (0,1) |

選配 (0,1) |

選配 (0,1) |

選配 (0,1,2) |

是 (1,2) |

是 (1,2) |

- 註:大部份Cortex-M3及M4的微處理器有位元帶及記憶體保護單元。M0/M0+可以用Cortex-M系統開發工具加入位元帶選項[13]

- 註:軟件在試圖使用特定機能時,需要先確認該機能是否有效[4]

- 註:Cortex-M35P的公開資料不多,一直到其技術參考手冊發行後才有改善。

- 位元組序:小端序(Little-endian)或大端序(big-endian)。Cortex-M和其他早期的ARM核心不同,在製作晶片時就要選用小端序或大端序。

- 中斷:1至32個(M0/M0+/M1)、1至240個(M3/M4/M7/M23)、1至480個(M33/M35P)

- 喚醒中斷控制器:選配

- 向量表位移暫存器:選配(M0沒有此選項)

- 指令存取寬度:只有16位元,或幾乎是32位元

- 支援用戶/特取模式:選配

- 重設所有的暫存器:選配

- 單一週期的I/O埠:選配(M0+/M23)

- 除錯存取埠(DAP):無、SWD、JTAG及SWD(所有Cortex-M核心都有此選項)

- 支援Halting除錯:選配

- 監視點比較器數量:0至2個(M0/M0+/M1),0至4個(M3/M4/M7/M23/M33/M35P)

- 中斷點比較器數量:0至4個 (M0/M0+/M1/M23),0至8個(M3/M4/M7/M33/M35P)

Cortex-M0 / M0+ / M1實現的是ARMv6-M架構[2],Cortex-M3實現的是ARMv7-M架構[3],Cortex-M4 / Cortex-M7實現的是ARMv7E-M架構[3]。Cortex-M23 / M33 / M35P實現的是ARMv8-M架構[15],Cortex-M55實現的是ARMv8.1-M架構[16]。這些架構是二進制的指令碼,可以和ARMv6-M、 ARMv7-M、ARMv7E-M向上相容。Cortex-M0 / Cortex-M0+ / Cortex-M1的指令碼不用修改就可以在Cortex-M3 / Cortex-M4 / Cortex-M7上執行。Cortex-M3上可以執行的二進制程式碼不需修改就可以在Cortex-M4 / Cortex-M7 / Cortex-M33 / Cortex-M35P上執行[2][3]。Cortex-M架構中支援Thumb-1和Thumb-2的指令集,不支援早期的32-bit ARM指令集。

所有Cortex-M的核心都有一個共通的指令子集,包括大部份Thumb-1指令、一些Thumb-2指令,以及結果為32位元的乘法。Cortex-M0 / Cortex-M0+ / Cortex-M1 / Cortex-M23設計目的就是希望讓矽晶面積最小,因此其指令集也是Cortex-M家族中最少的。

Cortex-M0 / M0+ / M1中有Thumb-1指令,不過沒有ARMv7-M架構才加入的指令(CBZ, CBNZ, IT)。Cortex-M0 / M0+ / M1包括一小部份的Thumb-2指令(BL, DMB, DSB, ISB, MRS, MSR)。Cortex-M3 / M4 / M7 / M33 / M35P 有所有基本的Thumb-1和Thumb-2指令。Cortex-M3加上了三個Thumb-1指令、所有的Thumb-2指令、硬件的整體除法、以及飽和運算指令。Cortex-M4加上了數碼訊號處理(DSP)指令,以及可選的單精度浮點運算器(VFPv4-SP)。Cortex-M7加上了可選的雙精度浮點運算器(VFPv5)[2][3]。Cortex-M23 / M33加上了TrustZone指令。

| Arm Core | Cortex M0[5] |

Cortex M0+[6] |

Cortex M1[7] |

Cortex M3[8] |

Cortex M4[9] |

Cortex M7[10] |

Cortex M23[11] |

Cortex M33[12] |

Cortex M35P |

Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|---|

| ARM架構 | ARMv6-M[2] | ARMv6-M[2] | ARMv6-M[2] | ARMv7-M[3] | ARMv7E-M[3] | ARMv7E-M[3] | ARMv8-M Baseline[15] |

ARMv8-M Mainline[15] |

ARMv8-M Mainline[15] |

Armv8.1-M |

| 電腦系統結構 | Von Neumann | Von Neumann | Von Neumann | Harvard | Harvard | Harvard | Von Neumann | Harvard | Harvard | Harvard |

| 指令管線化 | 3層 | 2層 | 3層 | 3層 | 3層 | 6層 | 2層 | 3層 | 3層 | 4到5層 |

| Thumb-1指令 | 大部份 | 大部份 | 大部份 | 全部 | 全部 | 全部 | 大部份 | 全部 | 全部 | 全部 |

| Thumb-2指令 | 部份 | 部份 | 部份 | 全部 | 全部 | 全部 | 部份 | 全部 | 全部 | 全部 |

| 乘法指令 32x32, 輸出32-bit |

是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| 乘法指令 32x32, 輸出64-bit |

否 | 否 | 否 | 是 | 是 | 是 | 否 | 是 | 是 | 是 |

| 除法指令 32/32,商32-bit |

否 | 否 | 否 | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| 飽和指令 | 否 | 否 | 否 | 部份 | 是 | 是 | 否 | 是 | 是 | 是 |

| DSP指令 instructions | 否 | 否 | 否 | 否 | 是 | 是 | 否 | 可選 | 可選 | 可選 |

| 單精度浮點數(SP) 浮點運算指令 |

否 | 否 | 否 | 否 | 可選 | 可選 | 否 | 可選 | 可選 | 可選 |

| 雙精度浮點數(DP) 浮點指令 |

否 | 否 | 否 | 否 | 否 | 可選 | 否 | 否 | 否 | 可選 |

| 半精度(HP) | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可選 |

| TrustZone指令 | 否 | 否 | 否 | 否 | 否 | 否 | 可選 | 可選 | 可選 | 可選 |

| 輔助處理器指令 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可選 | 可選 | 可選 |

| Helium技術 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可選 |

| 中斷延遲 (若用零等待狀態的RAM) |

16 cycles | 15 cycles | 23 for NMI 26 for IRQ |

12 cycles | 12 cycles | 12 cycles | 15 no security ext 27 security ext |

TBD | TBD | TBD |

- 註:Cortex-M0/M0+/M1不包括以下16位元的Thumb-1指令:CBZ, CBNZ, IT[2][3]。

- 註:Cortex-M0/M0+/M1隻包括以下32位元的Thumb-2指令:BL, DMB, DSB, ISB, MRS, MSR.[2][3]

- 註:Cortex-M0/M0+/M1/M23隻有乘積結果為32位元的乘法指令(32bit × 32bit = lower 32bit),而Cortex-M3/M4/M7/M33/M35P有32位元相乘,結果為32位元的乘法指令(32bit × 32bit = 64bit)。Cortex-M4/M7(M33/M35P可選)包括DSP乘法指令 (16bit × 16bit = 32bit)、(32bit × 16bit = upper 32bi)、(32bit × 32bit = upper 32bit)ref name="ARMv6-M-Manual"/>[3]

- 註:要計算完乘法及除法的週期數依ARM Cortex-M的核心設計而不同。有些核心有較快速度或是較小尺寸的矽智財選項,因此核心可能用較少的矽面積,但需要的週期數較長。在執行除法指令或慢速迭代乘法指令時發生的中斷會讓處理器放棄其指令,在中斷結束後再繼續。

- Cortex-M0/M0+/M23中,結果為32位元的乘法可以選擇是1個週期或是32個週期。Cortex-M1可以選擇是3個週期或是33個週期。Cortex-M3/M4/M7/M33/M35P都是一個週期。.

- Cortex-M3中,結果為32位元的乘法指令,可能是3–5個週期(視數值而定)。Cortex-M4/M7/M33/M35P是一個週期。

- Cortex-M3/M4的除法指令是2–12個週期(視數值而定)。Cortex-M7是3–20個週期(視數值而定)。Cortex-M23有17個週期或34個週期的選項。Cortex-M33是2–11個週期(視數值而定)。Cortex-M35P的資料還不確定。

- 註:Cortex-M4 / M7 / M33 / M35P有不含FPU的矽智財選項,或是單精度(SP)的FPU,Cortex-M7加上第三個矽智財選項,可以支援單精度以及雙精度(DP)的FPU。若Cortex-M4 / M7 / M33 / M35P有FPU,其型號會是Cortex-M4F / Cortex-M7F / Cortex-M33F / Cortex-M35PF.[2][3]。

- 註:Cortex-M系列包括三個新的16位元睡眠模式Thumb-1指令:SEV, WFE, WFI。

- 註:中斷延遲週期計數假設

- 1.堆疊放在零等待狀態RAM

- 2.沒有在執行其他的中斷

- 3.沒有安全延伸機能選項(因為會增加週期)

- 註:哈佛架構的Cortex-M,其中斷延遲週期計數會比較短。

| Group | Instr bits |

Instructions | Cortex M0,M0+,M1 |

Cortex M3 |

Cortex M4 |

Cortex M7 |

Cortex M23 |

Cortex M33,M35P |

Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|

| Thumb-1 | 16 | ADC, ADD, ADR, AND, ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSB, LDRSH, LSL, LSR, MOV, MUL, MVN, NOP, ORR, POP, PUSH, REV, REV16, REVSH, ROR, RSB, SBC, SEV, STM, STR, STRB, STRH, SUB, SVC, SXTB, SXTH, TST, UXTB, UXTH, WFE, WFI, YIELD | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-1 | 16 | CBNZ, CBZ | 否 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-1 | 16 | IT | 否 | 是 | 是 | 是 | 否 | 是 | 是 |

| Thumb-2 | 32 | BL, DMB, DSB, ISB, MRS, MSR | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-2 | 32 | SDIV, UDIV | 否 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-2 | 32 | ADC, ADD, ADR, AND, ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ, CMN, CMP, DBG, EOR, LDC, LDM, LDR, LDRB, LDRBT, LDRD, LDREX, LDREXB, LDREXH, LDRH, LDRHT, LDRSB, LDRSBT, LDRSH, LDRSHT, LDRT, LSL, LSR, MCR, MCRR, MLA, MLS, MOV, MOVT, MRC, MRRC, MUL, MVN, NOP, ORN, ORR, PLD, PLDW, PLI, POP, PUSH, RBIT, REV, REV16, REVSH, ROR, RRX, RSB, SBC, SBFX, SEV, SMLAL, SMULL, SSAT, STC, STM, STR, STRB, STRBT, STRD, STREX, STREXB, STREXH, STRH, STRHT, STRT, SUB, SXTB, SXTH, TBB, TBH, TEQ, TST, UBFX, UMLAL, UMULL, USAT, UXTB, UXTH, WFE, WFI, YIELD | 否 | 是 | 是 | 是 | 否 | 是 | 是 |

| DSP | 32 | PKH, QADD, QADD16, QADD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB16, QSUB8, SADD16, SADD8, SASX, SEL, SHADD16, SHADD8, SHASX, SHSAX, SHSUB16, SHSUB8, SMLABB, SMLABT, SMLATB, SMLATT, SMLAD, SMLALBB, SMLALBT, SMLALTB, SMLALTT, SMLALD, SMLAWB, SMLAWT, SMLSD, SMLSLD, SMMLA, SMMLS, SMMUL, SMUAD, SMULBB, SMULBT, SMULTT, SMULTB, SMULWT, SMULWB, SMUSD, SSAT16, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHADD8, UHASX, UHSAX, UHSUB16, UHSUB8, UMAAL, UQADD16, UQADD8, UQASX, UQSAX, UQSUB16, UQSUB8, USAD8, USADA8, USAT16, USAX, USUB16, USUB8, UXTAB, UXTAB16, UXTAH, UXTB16 | 否 | 否 | 是 | 是 | 否 | 可選 | 是 |

| 單精度浮點數 | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMSR, VMUL, VNEG, VNMLA, VNMLS, VNMUL, VPOP, VPUSH, VSQRT, VSTM, VSTR, VSUB | 否 | 否 | 可選 | 可選 | 否 | 可選 | 可選 |

| 雙精度浮點數 | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | 否 | 否 | 否 | 可選 | 否 | 否 | 可選 |

| TrustZone | 16 | BLXNS, BXNS | 否 | 否 | 否 | 否 | 可選 | 可選 | 可選 |

| TrustZone | 32 | SG, TT, TTT, TTA, TTAT | 否 | 否 | 否 | 否 | 可選 | 可選 | 可選 |

| 輔助處理器 | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRRC, MRRC2 | 否 | 否 | 否 | 否 | 否 | 可選 | 可選 |

- 註:針對Cortex-M4 / M7 / M33 / M35P,單精度(SP)浮點運算器指令只有在矽智財中有SP FPU選項時才有效。

- 註:針對Cortex-M7,雙精度(DP)浮點運算器指令只有在矽智財中有DP FPU選項時才有效。

ARM Cortex-M系列的ARM架構,已停用一些早期核心的穖能[2][3]:

- Cortex-M核心中沒有32位元的ARM指令集。

- 位元組序在矽智財實現時就需要決定。早期的核心允許依MCU資料位元組序模式設置而調整。

- Cortex-M核心不支援輔助處理器,一直到ARM Cortex-M33/M35P核心的ARMv8-M Mainline才重新支援此一選項。

32位元ARM指令的能力和Thumb-1和Thumb-2指令集有很多地方重疊了,不過有些ARM的特徵找不到類似的特性。

- SWP和SWPB(swap)ARM架構在Cortex-M中沒有類似的架構。

16位元Thumb-1指令集最早是出現在早期ARMv4T架構的ARM7T核心,隨着時代而演進。在ARMv5 / ARMv6 / ARMv6T2 架構問世時,Thumb-1指令集也有擴充。不過也有移除一些Thumb-1指令。

- 不存在BLX <immediate>指令,此指令是用來從Thumb-1切換到ARM的指令集。BLX <register>指令在Cortex-M系列仍然支援。

- 不存在SETEND指令,因為不允許在執行時切換位元組序。

- 不支援輔助處理器指令,一直到ARM Cortex-M33/M35P核心的ARMv8-M Mainline才重新支援此些指令。

- SWI指令更名為SVC,雖二進位碼相同。不過SVC的處理程式和SWI的處理程式在例外模式的處理上差很多。

Cortex-M0

Cortex-M0核心是依小矽晶片面積以及最低價晶片進行最佳化的核心。

Cortex-M0核心的主要特點有[5]:

- ARMv6-M架構[2]

- 三層管線化

- 指令集:

- Thumb-1(大部份),但沒有CBZ, CBNZ, IT

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR

- 32-bit硬件整數乘法,結果也是32-bit

- 1到32個中斷,以及不可遮罩中斷

矽智財選項:

- 硬件整數乘法速度:1週期或32週期。

Cortex-M0+

| 微架構 | ARMv6-M |

|---|---|

| 指令集架構 | Thumb-1 (most), Thumb-2 (some) |

Cortex-M0+是以Cortex-M0再進行優化的版本。Cortex-M0+支援所有Cortex-M0的指令,因此可以用相同的編譯器以及除錯工具。Cortex-M0+的管線化由三層變成二層,因此耗能較少。除了Cortex-M0已有的除錯功能外,Cortex-M0+增加了稱為微追蹤緩衝區(Micro Trace Buffer、MTB)的選項,有簡易的指令追蹤緩衝區。Cortex-M0+也有加入Cortex-M3和Cortex-M4的一些特點,是以矽智財選項的方式加入,例如記憶體保護單元(MPU),以及中斷向量表重新定位[6]。

Cortex-M0+核心的主要特點有[6]:

- ARMv6-M架構[2]

- 二層管線化(比Cortex-M0少一層)

- 指令集(和Cortex-M0)相同

- Thumb-1(大部份),但沒有CBZ, CBNZ, IT

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR

- 32-bit硬件整數乘法,結果也是32-bit

- 1到32個中斷,以及不可遮罩中斷

矽智財選項:

- 硬件整數乘法速度:1週期或32週期。

- 八個區塊的記憶體保護單元(MPU)(和M3、M4相同)

- 中斷向量表重新定位(和M3、M4相同)

- 單一週期的I/O埠(在M0+/M23上有此機能)

- 微追蹤緩衝區(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此機能)

Cortex-M1

| 微架構 | ARMv6-M |

|---|---|

| 指令集架構 | Thumb-1 (most), Thumb-2 (some) |

The Cortex-M1是特別設計可以放入FPGA晶片的內核。

Cortex-M1內核的主要特點有[7]:

- ARMv6-M架構[2]

- 二層管線化

- 指令集

- Thumb-1(大部份),但沒有CBZ, CBNZ, IT.

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit硬件整數乘法,結果也是32-bit

- 1到32個中斷,以及不可遮罩中斷

矽智財選項:

- 硬件整數乘法速度:3或33週期。

- 選配的緊密耦合記憶體(TCM)0 to 1 MB 指令TCM,0 to 1 MB 資料TCM,都可以選擇要不要ECC.

- 外部中斷:0, 1, 8, 16, 32.

- 除錯模式:無,簡易功能,完整

- 位元組序:little-endian或BE-8 big-endian.

- 作業系統延伸:可以選擇

Cortex-M3

- ARMv7-M架構[3]:

- 三層管線化以及分支預測

- 指令集:

- Thumb-1(完整)

- Thumb-2(完整)

- 32-bit硬件整數乘法,結果可以是32-bit或64-bit,有號或無號,在乘法後允許加法或減法。32-bit乘法是一個週期,64-bit乘法和乘積累加(MAC)需要的週期較多

- 32-bit硬件整數除法(2–12週期)

- 支援飽和運算

- 12個週期的中斷延遲

- 整合休眠模式

矽智財選項:

- 可選的記憶體保護單元(MPU):0個區或8個區

Cortex-M4

在概念上,Cortex-M4是Cortex-M3加上數碼訊號處理(DSP)指令、可選的浮點運算器。若有浮點運算器,會稱為Cortex-M4F。

Cortex-M4內核的主要特點有[9]:

- ARMv7E-M架構[3]

- 三層管線化以及分支預測

- 指令集:

- 12個週期的中斷延遲

- 整合休眠模式

矽智財選項:

- 可選的浮點運算器(FPU):只有單精度IEEE-754的,稱為FPv4-SP延伸

- 可選的記憶體保護單元(MPU):0個區或8個區

Cortex-M7

Cortex-M7是高效能的內核,其運算效能是Cortex-M4的二倍。其中包括六層的超純量管線化有分支預測,有可選的單精度浮點運算器或雙精度浮點運算器[18][19]。指令集以及資料匯流排已由32-bit寬度增加到64-bit寬度。若內核中有FPU,會稱為Cortex-M7F,不然會稱為Cortex-M7。

Cortex-M7內核的主要特點有[10]:

- ARMv7E-M架構

- 6階管線化以及分支預測。在ARM Cortex-M內核中是最多的。

- 指令集:

- 1至240個中斷,以及不可遮罩中斷

- 12個週期的中斷延遲

- 整合休眠模式

矽智財選項:

Cortex-M23

| 微架構 | ARMv8-M Baseline |

|---|---|

| 指令集架構 | Thumb-1 (most), Thumb-2 (some), 除法、TrustZone |

Cortex-M23內核在2016年10月上市[20],以2015年11月發佈的ARMv8-M架構為基礎[21]。在概念上Cortex-M23類似Cortex-M0+,加上整數除法指令、TrustZone安全特性、也是二層管線化。

- ARMv8-M基線架構[15]

- 二層管線化(類似Cortex-M0+)

- TrustZone安全指令(只有在M23/M33/M35P)

- 32-bit硬件整數除法(17 或 34 週期)(M0/M0+/M1沒有)

- 堆疊邊界限制(只有在SAU選項開啟時才有)(M23/M33/M35P才有)

矽智財選項:

- 硬件整數乘法速度:1週期或32週期。

- 硬件整數除法速度:最長17週期或34週期,依除數而定,指令有可能會提早完成。

- 可選的記憶體保護單元(MPU):0, 4, 8, 12, 16個區塊

- 可選的安全屬性單元(SAU):0, 4, 8個區塊

- 單一週期的I/O埠(在M0+/M23上有此機能)

- 微追蹤緩衝區(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此機能)

Cortex-M33

Cortex-M33內核是在2016年10月發佈[20],是以2015年11月發佈的ARMv8-M架構為基礎[21]。概念上類似Cortex-M4和Cortex-M23的交集,也有三階的指令管道。

- ARMv8-M架構[15]:

- 三階管道

- TrustZone安全指令(只有在M23/M33/M35P才有)

- 32-bit硬件整數除法(最長11個週期)(M0/M0+/M1無此選項)

- 堆疊邊界限制(只有在SAU選項開啟時才有)(M23/M33/M35P才有)

矽智財選項:

- 可選的浮點運算器(FPU):只有單精度IEEE-754的,稱為FPv5延伸

- 可選的記憶體保護單元(MPU):0, 4, 8, 12, 16個區塊

- 可選的安全屬性單元(SAU):0, 4, 8個區塊

- 微追蹤緩衝區(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此機能)

Cortex-M35P

Cortex-M35P內核是在2018年5月發佈的,在概念上是Cortex-M33內核加上新的指令集,以及來自ARM SecurCore系列,新的防篡改硬件、可選的同位元以及ECC功能[22]。

目前此晶片的公開資料不多,只有技術參考手冊。到2020年2月為止,尚未看到各廠商推出此系列的微處理器。

Cortex-M55

Cortex-M55是在2020年2月發佈,是以2019年2月發佈的Armv8.1-M架構為基礎,有四階指令管道。

Cortex-M55核心的主要特點有:

- ARMv8.1-M Mainline/Helium內核[15]

- 四階管道

- 堆疊邊界限制(只有在SAU選項開啟時才有)

矽智財選項:

- Helium (M-Profile Vector Extension, MVE)

- 單精度和雙精度的浮點運算器

- 可選的DSP延伸

- 可選的TrustZone安全延伸

- 支援RAS(Safety and reliability)功能

- 支援協處理器

- 區分安全區和非安全區的MPU,可以分為0, 4, 8, 12或16個區

- 安全屬性單元可以分為0, 4或8個區

- 指令快取,大小可以設置為4KB, 8KB, 16KB, 32KB, 64KB

- 資料快取,大小可以設置為4KB, 8KB, 16KB, 32KB, 64KB

- 快取及TCM支援ECC

- 1–480個中斷

- 3–8個例外優先位元

- 內部和外部的喚醒中斷控制器(WIC)選項,可選的CTI, ITM及DWT

- ARM客製指令(未來發佈的版本中會支援)

檔案

ARM晶片的檔案很多。 過去八位元的微處理器只有一份檔案,不過隨着微處理器的進步,許多功能都需要支援。ARM晶片的檔案包一般會包括IC製造商以及CPU內核供應商(Arm)的檔案。

典型的檔案結構如下:

- 檔案樹(從上到下)

- IC製造商網頁

- IC製造商宣傳投影片

- IC製造商實際晶片的數據表

- IC製造商該晶片家族的參考手冊,其中有常用週邊以及特點

- ARM內核網站

- ARM內核通用使用手冊

- ARM內核技術參考手冊

- ARM架構參考手冊

IC製造商可能會有其他資料,例如開發板使用手冊、應用指南、快速手冊、軟件函式庫檔案、已知問題等。

參考資料

延伸閱讀

外部連結

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.