邏輯門

来自维基百科,自由的百科全书

邏輯閘或邏輯門是集成電路的基本概念組件。簡單邏輯門可由電晶體組成。這些電晶體的組合可以使代表兩種訊號的高低電平在通過它們之後產生高電平或者低電平的訊號。高、低電平可以分別代表邏輯上的「真」(T;true)與「假」(F;false)或二進制的1和0,從而實現邏輯運算。常見的邏輯門包括與閘,或門,非閘,異或閘(也稱異或)。

| 基本邏輯閘 | |

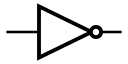

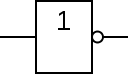

| 緩衝 | 非 |

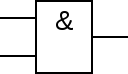

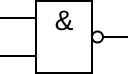

| 與 | 與非 |

| 或 | 或非 |

| 異或 | 同或 |

| 蘊含 | 蘊含非 |

邏輯門是組成數字系統的基本結構,通常組合使用運算更複雜的邏輯。一些廠商通過組合邏輯門生產實用、小型、集成的產品,如可程式邏輯裝置。

符號表

常用的邏輯門有兩種常用表示法,皆由ANSI(美國國家標準協會)/IEEE(電機電子工程師學會)Std 91-1984跟作為其補充的ANSI/IEEE Std 91a-1991。 「特殊形狀符號」是用過去電路簡圖為基礎以及50年代、60年代MIL-STD-806作衍生;有時也描述成「軍事」,而這個也反映了它的起源。「IEC矩形國標符號」是以ANSI Y32.14跟一些早期工業用的符號為基礎,再重新由IEEE跟IEC(國際電工委員會)做微調而成;在每個符號中皆可以發現有矩形的外框圍着所代表的字,且相較於舊的表示法,他可以涵蓋更多的邏輯門[1]。ICE的標準也被轉換成其他表示法,像是歐洲的EN(歐洲標準委員會)60617-12:1999、英國的BS(由英國標準學會制定) EN 60617-12:1999跟德國的DIN EN 60617-12:1998。

IEEE Std 91-1984跟IEC 60617-12的共同目標是提供一套有系統符號來描述複雜的邏輯功能跟數碼電路。這些邏輯的功能相較於AND閘和OR閘更加的複雜,例如中等大小的4位元計數器或大型的微處理器。

IEC 617-12以及接替他的IEC 60617-12沒有很明確的標示出「特殊形狀符號」,但是不可能不使用他們[1]。然而在ANSI/IEEE 91和ANSI/IEEE 91a有提到:「根據IEC刊物第617期的第12部分指出特殊形狀符號不會優先使用,但也沒有和特殊形狀符號有衝突」。IEC 60617-12則包含了相應說明(在第2.1節):「即使非優先使用,使用其他由國家標準認可的符號-特殊形狀符號,不應被認為和這個標準有衝突。在使用其他特殊形狀符號,以形成複數符號(例如使用如嵌入的符號)不應鼓勵」。這項妥協方案使IEEE跟IEC協會遵守各自的標準。

第三種表示法較廣泛用在歐洲,尤其是歐洲的學術界;可參見"DIN 40700"的德文版條目。

在1980年代,示意圖成為主要的方式用來設計印刷電路板以及客製化IC(例如邏輯陣列)。而現在,客製化IC和現場可程式邏輯門陣列(field-programmable gate array)通常用Verilog或VHDL等硬件描述語言(Hardware Description Language;HDL)來設計。

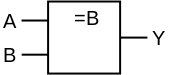

| 類型 | ANSI及IEEE標準 | IEC標準 | 漢名 | 短釋 | 邏輯函數表示 | 真值表 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| AND |

|

|

「與」閘/「及」閘/「且」閘 | 全入皆高才出高。

一低出低。 |

或

|

AND有0則0 | ||||||||||||||||||

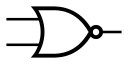

| OR |

|

|

「或」閘 | 全入皆低才出低。

一高出高。 |

或

|

OR有1則1 | ||||||||||||||||||

| NOT |

|

|

「非」閘/反相器/「反」閘/變流器 | 輸入的高低狀態逆轉。 |

| |||||||||||||||||||

| 在電子領域,NOT閘也常稱反相器(Inverter)。符號後圓圈常稱泡泡,泡泡常用來表示外部邏輯狀態及內部邏輯狀態(氣泡右側及氣泡左側)的否定關係(1變0、0變1)。電路圖一定要定義0和1的狀態,通常高電位=1 (=5V) , 低電位=0(=GND);當然有些時候如果要將高電位設為0時,可以直接在電路圖中說明,這稱為直接極性指示,可參見IEEE Std 91/91A跟IEC 60617-12,兩者表示法中泡泡跟電路圖中的說明可以在使用特殊形狀符號及矩形國標符號的電路圖中使用,但純邏輯電路圖只有泡泡可用。 | ||||||||||||||||||||||||

| NAND |

|

|

「與非」閘/「反及」閘/「非與」閘/「反且」閘 | 全入皆高才出低。

一低出高。 |

| |||||||||||||||||||

| NOR |

|

|

「或非」閘/「反或」閘/「非或」閘 | 全入皆低才出高。

一高出低。 |

| |||||||||||||||||||

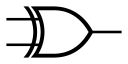

| XOR |

|

|

「異或」閘/「異或」閘 | 只有其中一項輸入為高,輸出為高;否則出低。 |

| |||||||||||||||||||

| XOR閘(exclusive-OR)的輸出為1只有當兩項輸入是不同的狀態;反之當兩者輸入相同,輸出為0,不論輸入為0或1。如果有超過兩項輸入,當輸入端為1的數目是奇數。實際使用上,這些閘由更基本的邏輯門組合而成。 | ||||||||||||||||||||||||

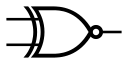

| XNOR |

|

|

「同或」閘/「反異或」閘/「互斥反或」閘/「異或非」閘 | 只有其中一項輸入為高,輸出為低;否則出高。 |

或

|

| ||||||||||||||||||

| BUF |

|

|

「是」閘/同相器/「同」閘/中繼器 | 輸出的高低狀態與輸入相同。 |

| |||||||||||||||||||

| IMPLY |

|

|

「蘊含」閘/「蘊含」閘 | 如果第一輸入為低,輸出高,否則輸出與第二輸入相同的高低狀態。 |

| |||||||||||||||||||

| NIMPLY |

|

|

「蘊含非」閘/「蘊含非」閘 | 如果第一輸入為低,輸出低,否則輸出與第二輸入相反的高低狀態。 |

或

|

| ||||||||||||||||||

通用邏輯門

查爾斯·桑德斯·皮爾士(1880–81冬)指出NOR閘可單獨使用(或者NAND閘也可以)來產生其他邏輯門的所有功能,不過他這個研究一直到1933年才發表。[2]1913年,Henry M. Sheffer第一個發表NAND閘可以做出全部功能的證明,也因此NAND閘的邏輯運算有時候也稱為謝費爾豎線(Sheffer stroke);NOR閘有時叫Peirce's arrow。[3]所以這些閘有時候叫做通用邏輯門

參考文獻

外部連結

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

,

,  ...

...