上拉電阻

来自维基百科,自由的百科全书

在數碼電路中,上拉電阻(英語:Pull-up resistors)是當某輸入端口未連接設備或處於高阻抗的情況下,一種用於保證輸入訊號為預期邏輯電平的電阻元件。他們通常在不同的邏輯裝置之間工作,提供一定的電壓訊號。[1][2]

原理

在上拉電阻所連接的導線上,如果外部組件未啟用,上拉電阻則「微弱地」將輸入電壓訊號「拉高」。當外部組件未連接時,對輸入端來說,外部「看上去」就是高阻抗的。這時,通過上拉電阻可以將輸入端口處的電壓拉高到高電平。如果外部組件啟用,它將取消上拉電阻所設置的高電平。通過這樣,上拉電阻可以使引腳即使在未連接外部組件的時候也能保持確定的邏輯電平。[3]

同樣的,一個下拉電阻(Pull-down resistor)以類似的方式工作,不過是與地(GND)連接。它可以使邏輯訊號保持在接近0伏特的狀態,即使沒有活動的設備連接在其所在的引腳上。

應用

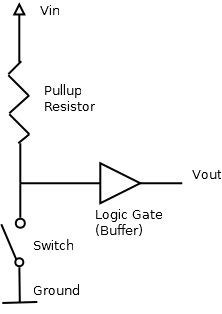

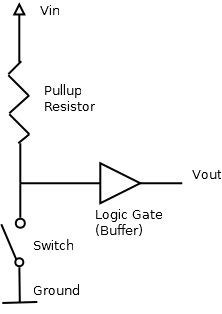

一個上拉電阻可以設置在連接邏輯門和其輸入端之間。例如,一個輸入訊號可以被一個電阻拉高,而一個開關或者帶跳線可以將輸入端和地相連。這可以被用作信息配置、選擇,或者對外部設備訊號進行檢錯糾錯。

上拉電阻可以在邏輯設備不提供電流的時候工作。集極開路就具有上拉電阻[3],這樣的電路輸出訊號常常在驅動外部設備、組合邏輯電路、多個設備連接到一個總線的情況里應用。例如,右圖所示的電路使用5伏特來激勵一個繼電器。如果左邊的輸入未連入,下拉電阻R1保證輸入訊號被拉低至低電平。7407TTL系列是一個集極緩衝器,僅僅輸出它所得到的輸入訊號。但是對於右邊的元件來說,由於是TTL型元件,當它輸出高電平的時候,它本身對右邊的元件來說等效為未連接。這時,上拉電阻R2將輸出訊號上拉到12伏特,為下一級場效電晶體提供足夠的電壓使之導通,從而激活繼電器。

上拉電阻可以和其他邏輯設備一起焊接在同一個電路板上。許多微控制器希望嵌入式控制應用程式使用內部的、可程式化的上拉電阻,減少對外部組件的需求。[2]

缺點

上拉電阻的缺點是當電流流經時其將消耗額外的能量,並且可能會引起輸出電平的延遲。某些邏輯晶片對於經過上拉電阻引入的電源供應瞬間狀態較為敏感,這樣就迫使為上拉電阻配置獨立的、帶有濾波的電壓源。[2]

參考文獻

相關條目

Wikiwand - on

Seamless Wikipedia browsing. On steroids.