ARM Cortex-M是ARM架构处理器核心中,低阶系列的统称,由安谋控股所授权。这组核心的特点为低成本以及高能源效率的微处理器而最佳化设计,已有上千万个消费性设备中有此系列的微处理器[1]。此系列核心包括Cortex-M0、Cortex-M0+、Cortex-M1、Cortex-M3、Cortex-M4、Cortex-M7、Cortex-M23、Cortex-M33、Cortex-M35P和Cortex-M55。其中Cortex-M4 / M7 / M33 / M35P / M55 核心有浮点运算器的选项,若有浮点运算器的选项,会在型号后面说明,例如Cortex-Mx with FPU或Cortex-MxF,其中x是核心编号。

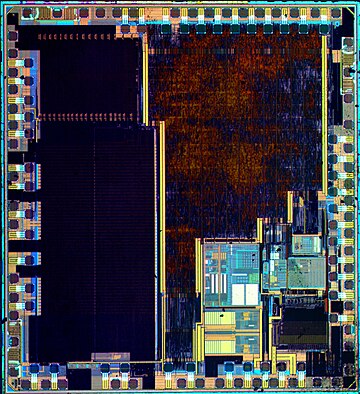

24 MHz ARM Cortex-M3 单片机,有16千字节闪存,4 KB RAM。由意法半导体生产

简介

| 32-bit | |

|---|---|

| 年份 | 核心 |

| 2004年 | Cortex-M3 |

| 2007年 | Cortex-M1 |

| 2009年 | Cortex-M0 |

| 2010年 | Cortex-M4 |

| 2012年 | Cortex-M0+ |

| 2014年 | Cortex-M7 |

| 2016年 | Cortex-M23 |

| 2016年 | Cortex-M33 |

| 2018年 | Cortex-M35P |

| 2020年 | Cortex-M55 |

ARM Cortex-M系列是为了单片机、特殊应用积体电路(ASIC)、应用专门标准产品(ASSP)、现场可编程逻辑门阵列(FPGA)及单片系统(SoC)设计的ARM微处理器核心。Cortex-M核心常用在 专用微控制器晶片中,但也会藏在SoC晶片中,例如电源管理制器、输入/输出控制器、系统控制器、触碰萤幕控制器、智慧电池控制器以及感测器控制器。

以往8位元的微控制器相当流行,但低阶的Cortex-M晶片已经降价,占据了一些8位元微控制器的市场。在取代8位元微控制器时,Cortex-M是常出现的选项,因为有32位元数学运算上的优势,也会用来替换一些较旧的ARM核心 ,例如ARM7及ARM9。

安谋控股不会以其自身的技术生产CPU或贩售CPU,而是其将处理器的架构授权给其他有意愿开发的公司。安谋有许多不同的授权条款,差异在成本以及可交付成果。对于所有的授权,安谋都会提出一份可整合的ARM核心硬体描述,也包括完整的软体开发工具组,以及贩售包括ARM CPU在内的积体电路的权利。

整合元件制造厂(IDM)收到的ARM处理器知识产权,是可逻辑综合的寄存器传输级(用Verilog所写)。以此型式,整合元件制造商可以进行架构层级的最佳化以及延伸,可以让制造商达成其客户的设计目的,例如高时脉速度、非常低的能耗、指令集延伸(包括浮点数)、针对大小的最佳化、除错器的支援等。若要确认特定的ARM CPU晶片中已有那些功能,则需确认制造商的资料表以及相关文件。

Cortex-M核心的部份选配机能如下:

- SysTick计时器:24位元的系统计时器,延伸了处理器以及巢状向量中断控制器(Nested Vectored Interrupt Controller、NVIC)的机能。若有此计时器,也可以提供额外的SysTick中断,可以配置其优先权[2][3][4]。虽然SysTick计时器不是必备的,不过几乎没有不支援SysTick的Cortex-M微处理器。若Cortex-M33控制器有安全扩展(Security Extension)选项,会有二个SysTicks,一个是安全的,另一个是一般的。

- 位元带(Bit-Band):位元带区域内记忆体中的每一个位元,可以个别映射到一个字元组。例如,写入特定的假名字元组,就代表设定或是清除位元带区域内特定的位元。因此位元带区域内的每一个位元都可以透过字元组对齐的位址来直接读写。而且,每一个位元都可以用C/C++进行设定、清除、反相等功能,不需要透过一连串畗读取-修改-写入的指令顺序[2][3][4]。位元带也不是Cortex-M一定会有的功能,不过不支援位元带的Cortex-M3或Cortex-M4微处理器较不常见。有些Cortex-M0及Cortex-M0+微处理器也会有位元带。

- 记忆体保护单元(MPU):透过强制的权限以及存取规则,可以保护特定区域的记忆体。最多可以支援八个不同的记忆体区域,每个还可以分成八个等大小的子区域[2][3][4]。

- 紧密耦合记忆体(Tightly-Coupled Memory、TCM):是低延迟的RAM,可以保存关键性的程序、资料及堆叠。紧密耦合记忆体一般会是微处理器中最快的RAM,仅次于缓存记忆体。

| ARM Core | Cortex M0[5] |

Cortex M0+[6] |

Cortex M1[7] |

Cortex M3[8] |

Cortex M4[9] |

Cortex M7[10] |

Cortex M23[11] |

Cortex M33[12] |

Cortex M35P |

|---|---|---|---|---|---|---|---|---|---|

| SysTick 24位元计时器 | 选配 (0,1) |

选配 (0,1) |

选配 (0,1) |

是 (1) |

是 (1) |

是 (1) |

选配 (0,1,2) |

是 (1,2) |

是 (1,2) |

| 单周期I/O埠 | 否 | 选配 | 否 | 否 | 否 | 否 | 选配 | 否 | 否 |

| 位元带记忆体 | 否[13] | 否[13] | 否* | 选配 | 选配 | 选配 | 否 | 否 | 否 |

| 记忆体保护单元 (MPU) |

否 | 选配 (0,8) |

否 | 选配 (0,8) |

选配 (0,8) |

选配 (0,8,16) |

选配 (0,4,8,12,16) |

选配 (0,4,8,12,16) |

选配 * |

| 安全属性单元(SAU) 及堆叠限制 |

否 | 否 | 否 | 否 | 否 | 否 | 选配 (0,4,8) |

选配 (0,4,8) |

选配 * |

| 指令TCM | 否 | 否 | 选配 | 否 | 否 | 选配 | 否 | 否 | 否 |

| 资料TCM | 否 | 否 | 选配 | 否 | 否 | 选配 | 否 | 否 | 否 |

| 指令缓存 | 否[14] | 否[14] | 否[14] | 否[14] | 否[14] | 选配 | 否 | 否 | 选配 |

| 资料缓存 | 否[14] | 否[14] | 否[14] | 否[14] | 否[14] | 选配 | 否 | 否 | 否 |

| 向量表位移暂存器 (VTOR) |

否 | 选配 (0,1) |

选配 (0,1) |

选配 (0,1) |

选配 (0,1) |

选配 (0,1) |

选配 (0,1,2) |

是 (1,2) |

是 (1,2) |

- 注:大部份Cortex-M3及M4的微处理器有位元带及记忆体保护单元。M0/M0+可以用Cortex-M系统开发工具加入位元带选项[13]

- 注:软体在试图使用特定机能时,需要先确认该机能是否有效[4]

- 注:Cortex-M35P的公开资料不多,一直到其技术参考手册发行后才有改善。

- 字节序:小端序(Little-endian)或大端序(big-endian)。Cortex-M和其他早期的ARM核心不同,在制作晶片时就要选用小端序或大端序。

- 中断:1至32个(M0/M0+/M1)、1至240个(M3/M4/M7/M23)、1至480个(M33/M35P)

- 唤醒中断控制器:选配

- 向量表位移暂存器:选配(M0没有此选项)

- 指令存取宽度:只有16位元,或几乎是32位元

- 支援使用者/特取模式:选配

- 重置所有的暂存器:选配

- 单一周期的I/O埠:选配(M0+/M23)

- 除错存取埠(DAP):无、SWD、JTAG及SWD(所有Cortex-M核心都有此选项)

- 支援Halting除错:选配

- 监视点比较器数量:0至2个(M0/M0+/M1),0至4个(M3/M4/M7/M23/M33/M35P)

- 中断点比较器数量:0至4个 (M0/M0+/M1/M23),0至8个(M3/M4/M7/M33/M35P)

Cortex-M0 / M0+ / M1实现的是ARMv6-M架构[2],Cortex-M3实现的是ARMv7-M架构[3],Cortex-M4 / Cortex-M7实现的是ARMv7E-M架构[3]。Cortex-M23 / M33 / M35P实现的是ARMv8-M架构[15],Cortex-M55实现的是ARMv8.1-M架构[16]。这些架构是二进制的指令码,可以和ARMv6-M、 ARMv7-M、ARMv7E-M向上相容。Cortex-M0 / Cortex-M0+ / Cortex-M1的指令码不用修改就可以在Cortex-M3 / Cortex-M4 / Cortex-M7上执行。Cortex-M3上可以执行的二进制程式码不需修改就可以在Cortex-M4 / Cortex-M7 / Cortex-M33 / Cortex-M35P上执行[2][3]。Cortex-M架构中支援Thumb-1和Thumb-2的指令集,不支援早期的32-bit ARM指令集。

所有Cortex-M的核心都有一个共通的指令子集,包括大部份Thumb-1指令、一些Thumb-2指令,以及结果为32位元的乘法。Cortex-M0 / Cortex-M0+ / Cortex-M1 / Cortex-M23设计目的就是希望让矽晶面积最小,因此其指令集也是Cortex-M家族中最少的。

Cortex-M0 / M0+ / M1中有Thumb-1指令,不过没有ARMv7-M架构才加入的指令(CBZ, CBNZ, IT)。Cortex-M0 / M0+ / M1包括一小部份的Thumb-2指令(BL, DMB, DSB, ISB, MRS, MSR)。Cortex-M3 / M4 / M7 / M33 / M35P 有所有基本的Thumb-1和Thumb-2指令。Cortex-M3加上了三个Thumb-1指令、所有的Thumb-2指令、硬体的整体除法、以及饱和运算指令。Cortex-M4加上了数位讯号处理(DSP)指令,以及可选的单精度浮点运算器(VFPv4-SP)。Cortex-M7加上了可选的双精度浮点运算器(VFPv5)[2][3]。Cortex-M23 / M33加上了TrustZone指令。

| Arm Core | Cortex M0[5] |

Cortex M0+[6] |

Cortex M1[7] |

Cortex M3[8] |

Cortex M4[9] |

Cortex M7[10] |

Cortex M23[11] |

Cortex M33[12] |

Cortex M35P |

Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|---|

| ARM架构 | ARMv6-M[2] | ARMv6-M[2] | ARMv6-M[2] | ARMv7-M[3] | ARMv7E-M[3] | ARMv7E-M[3] | ARMv8-M Baseline[15] |

ARMv8-M Mainline[15] |

ARMv8-M Mainline[15] |

Armv8.1-M |

| 计算机系统结构 | Von Neumann | Von Neumann | Von Neumann | Harvard | Harvard | Harvard | Von Neumann | Harvard | Harvard | Harvard |

| 指令管线化 | 3层 | 2层 | 3层 | 3层 | 3层 | 6层 | 2层 | 3层 | 3层 | 4到5层 |

| Thumb-1指令 | 大部份 | 大部份 | 大部份 | 全部 | 全部 | 全部 | 大部份 | 全部 | 全部 | 全部 |

| Thumb-2指令 | 部份 | 部份 | 部份 | 全部 | 全部 | 全部 | 部份 | 全部 | 全部 | 全部 |

| 乘法指令 32x32, 输出32-bit |

是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| 乘法指令 32x32, 输出64-bit |

否 | 否 | 否 | 是 | 是 | 是 | 否 | 是 | 是 | 是 |

| 除法指令 32/32,商32-bit |

否 | 否 | 否 | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| 饱和指令 | 否 | 否 | 否 | 部份 | 是 | 是 | 否 | 是 | 是 | 是 |

| DSP指令 instructions | 否 | 否 | 否 | 否 | 是 | 是 | 否 | 可选 | 可选 | 可选 |

| 单精度浮点数(SP) 浮点运算指令 |

否 | 否 | 否 | 否 | 可选 | 可选 | 否 | 可选 | 可选 | 可选 |

| 双精度浮点数(DP) 浮点指令 |

否 | 否 | 否 | 否 | 否 | 可选 | 否 | 否 | 否 | 可选 |

| 半精度(HP) | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可选 |

| TrustZone指令 | 否 | 否 | 否 | 否 | 否 | 否 | 可选 | 可选 | 可选 | 可选 |

| 辅助处理器指令 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可选 | 可选 | 可选 |

| Helium技术 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 否 | 可选 |

| 中断延迟 (若用零等待状态的RAM) |

16 cycles | 15 cycles | 23 for NMI 26 for IRQ |

12 cycles | 12 cycles | 12 cycles | 15 no security ext 27 security ext |

TBD | TBD | TBD |

- 注:Cortex-M0/M0+/M1不包括以下16位元的Thumb-1指令:CBZ, CBNZ, IT[2][3]。

- 注:Cortex-M0/M0+/M1只包括以下32位元的Thumb-2指令:BL, DMB, DSB, ISB, MRS, MSR.[2][3]

- 注:Cortex-M0/M0+/M1/M23只有乘积结果为32位元的乘法指令(32bit × 32bit = lower 32bit),而Cortex-M3/M4/M7/M33/M35P有32位元相乘,结果为32位元的乘法指令(32bit × 32bit = 64bit)。Cortex-M4/M7(M33/M35P可选)包括DSP乘法指令 (16bit × 16bit = 32bit)、(32bit × 16bit = upper 32bi)、(32bit × 32bit = upper 32bit)ref name="ARMv6-M-Manual"/>[3]

- 注:要计算完乘法及除法的周期数依ARM Cortex-M的核心设计而不同。有些核心有较快速度或是较小尺寸的矽智财选项,因此核心可能用较少的矽面积,但需要的周期数较长。在执行除法指令或慢速迭代乘法指令时发生的中断会让处理器放弃其指令,在中断结束后再继续。

- Cortex-M0/M0+/M23中,结果为32位元的乘法可以选择是1个周期或是32个周期。Cortex-M1可以选择是3个周期或是33个周期。Cortex-M3/M4/M7/M33/M35P都是一个周期。.

- Cortex-M3中,结果为32位元的乘法指令,可能是3–5个周期(视数值而定)。Cortex-M4/M7/M33/M35P是一个周期。

- Cortex-M3/M4的除法指令是2–12个周期(视数值而定)。Cortex-M7是3–20个周期(视数值而定)。Cortex-M23有17个周期或34个周期的选项。Cortex-M33是2–11个周期(视数值而定)。Cortex-M35P的资料还不确定。

- 注:Cortex-M4 / M7 / M33 / M35P有不含FPU的矽智财选项,或是单精度(SP)的FPU,Cortex-M7加上第三个矽智财选项,可以支援单精度以及双精度(DP)的FPU。若Cortex-M4 / M7 / M33 / M35P有FPU,其型号会是Cortex-M4F / Cortex-M7F / Cortex-M33F / Cortex-M35PF.[2][3]。

- 注:Cortex-M系列包括三个新的16位元睡眠模式Thumb-1指令:SEV, WFE, WFI。

- 注:中断延迟周期计数假设

- 1.堆叠放在零等待状态RAM

- 2.没有在执行其他的中断

- 3.没有安全延伸机能选项(因为会增加周期)

- 注:哈佛架构的Cortex-M,其中断延迟周期计数会比较短。

| Group | Instr bits |

Instructions | Cortex M0,M0+,M1 |

Cortex M3 |

Cortex M4 |

Cortex M7 |

Cortex M23 |

Cortex M33,M35P |

Cortex M55 |

|---|---|---|---|---|---|---|---|---|---|

| Thumb-1 | 16 | ADC, ADD, ADR, AND, ASR, B, BIC, BKPT, BLX, BX, CMN, CMP, CPS, EOR, LDM, LDR, LDRB, LDRH, LDRSB, LDRSH, LSL, LSR, MOV, MUL, MVN, NOP, ORR, POP, PUSH, REV, REV16, REVSH, ROR, RSB, SBC, SEV, STM, STR, STRB, STRH, SUB, SVC, SXTB, SXTH, TST, UXTB, UXTH, WFE, WFI, YIELD | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-1 | 16 | CBNZ, CBZ | 否 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-1 | 16 | IT | 否 | 是 | 是 | 是 | 否 | 是 | 是 |

| Thumb-2 | 32 | BL, DMB, DSB, ISB, MRS, MSR | 是 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-2 | 32 | SDIV, UDIV | 否 | 是 | 是 | 是 | 是 | 是 | 是 |

| Thumb-2 | 32 | ADC, ADD, ADR, AND, ASR, B, BFC, BFI, BIC, CDP, CLREX, CLZ, CMN, CMP, DBG, EOR, LDC, LDM, LDR, LDRB, LDRBT, LDRD, LDREX, LDREXB, LDREXH, LDRH, LDRHT, LDRSB, LDRSBT, LDRSH, LDRSHT, LDRT, LSL, LSR, MCR, MCRR, MLA, MLS, MOV, MOVT, MRC, MRRC, MUL, MVN, NOP, ORN, ORR, PLD, PLDW, PLI, POP, PUSH, RBIT, REV, REV16, REVSH, ROR, RRX, RSB, SBC, SBFX, SEV, SMLAL, SMULL, SSAT, STC, STM, STR, STRB, STRBT, STRD, STREX, STREXB, STREXH, STRH, STRHT, STRT, SUB, SXTB, SXTH, TBB, TBH, TEQ, TST, UBFX, UMLAL, UMULL, USAT, UXTB, UXTH, WFE, WFI, YIELD | 否 | 是 | 是 | 是 | 否 | 是 | 是 |

| DSP | 32 | PKH, QADD, QADD16, QADD8, QASX, QDADD, QDSUB, QSAX, QSUB, QSUB16, QSUB8, SADD16, SADD8, SASX, SEL, SHADD16, SHADD8, SHASX, SHSAX, SHSUB16, SHSUB8, SMLABB, SMLABT, SMLATB, SMLATT, SMLAD, SMLALBB, SMLALBT, SMLALTB, SMLALTT, SMLALD, SMLAWB, SMLAWT, SMLSD, SMLSLD, SMMLA, SMMLS, SMMUL, SMUAD, SMULBB, SMULBT, SMULTT, SMULTB, SMULWT, SMULWB, SMUSD, SSAT16, SSAX, SSUB16, SSUB8, SXTAB, SXTAB16, SXTAH, SXTB16, UADD16, UADD8, UASX, UHADD16, UHADD8, UHASX, UHSAX, UHSUB16, UHSUB8, UMAAL, UQADD16, UQADD8, UQASX, UQSAX, UQSUB16, UQSUB8, USAD8, USADA8, USAT16, USAX, USUB16, USUB8, UXTAB, UXTAB16, UXTAH, UXTB16 | 否 | 否 | 是 | 是 | 否 | 可选 | 是 |

| 单精度浮点数 | 32 | VABS, VADD, VCMP, VCMPE, VCVT, VCVTR, VDIV, VLDM, VLDR, VMLA, VMLS, VMOV, VMRS, VMSR, VMUL, VNEG, VNMLA, VNMLS, VNMUL, VPOP, VPUSH, VSQRT, VSTM, VSTR, VSUB | 否 | 否 | 可选 | 可选 | 否 | 可选 | 可选 |

| 双精度浮点数 | 32 | VCVTA, VCVTM, VCVTN, VCVTP, VMAXNM, VMINNM, VRINTA, VRINTM, VRINTN, VRINTP, VRINTR, VRINTX, VRINTZ, VSEL | 否 | 否 | 否 | 可选 | 否 | 否 | 可选 |

| TrustZone | 16 | BLXNS, BXNS | 否 | 否 | 否 | 否 | 可选 | 可选 | 可选 |

| TrustZone | 32 | SG, TT, TTT, TTA, TTAT | 否 | 否 | 否 | 否 | 可选 | 可选 | 可选 |

| 辅助处理器 | 16 | CDP, CDP2, MCR, MCR2, MCRR, MCRR2, MRC, MRC2, MRRC, MRRC2 | 否 | 否 | 否 | 否 | 否 | 可选 | 可选 |

- 注:针对Cortex-M4 / M7 / M33 / M35P,单精度(SP)浮点运算器指令只有在矽智财中有SP FPU选项时才有效。

- 注:针对Cortex-M7,双精度(DP)浮点运算器指令只有在矽智财中有DP FPU选项时才有效。

ARM Cortex-M系列的ARM架构,已停用一些早期核心的穖能[2][3]:

- Cortex-M核心中没有32位的ARM指令集。

- 字节序在矽智财实现时就需要决定。早期的核心允许依MCU资料字节序模式设定而调整。

- Cortex-M核心不支援辅助处理器,一直到ARM Cortex-M33/M35P核心的ARMv8-M Mainline才重新支援此一选项。

32位元ARM指令的能力和Thumb-1和Thumb-2指令集有很多地方重叠了,不过有些ARM的特征找不到类似的特性。

- SWP和SWPB(swap)ARM架构在Cortex-M中没有类似的架构。

16位元Thumb-1指令集最早是出现在早期ARMv4T架构的ARM7T核心,随著时代而演进。在ARMv5 / ARMv6 / ARMv6T2 架构问世时,Thumb-1指令集也有扩充。不过也有移除一些Thumb-1指令。

- 不存在BLX <immediate>指令,此指令是用来从Thumb-1切换到ARM的指令集。BLX <register>指令在Cortex-M系列仍然支援。

- 不存在SETEND指令,因为不允许在执行时切换字节序。

- 不支援辅助处理器指令,一直到ARM Cortex-M33/M35P核心的ARMv8-M Mainline才重新支援此些指令。

- SWI指令更名为SVC,虽二进位码相同。不过SVC的处理程式和SWI的处理程式在例外模式的处理上差很多。

Cortex-M0

Cortex-M0核心是依小矽晶元面积以及最低价晶片进行最佳化的核心。

Cortex-M0核心的主要特点有[5]:

- ARMv6-M架构[2]

- 三层管线

- 指令集:

- Thumb-1(大部份),但没有CBZ, CBNZ, IT

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR

- 32-bit硬体整数乘法,结果也是32-bit

- 1到32个中断,以及不可遮罩中断

矽智财选项:

- 硬体整数乘法速度:1周期或32周期。

Cortex-M0+

| 微架构 | ARMv6-M |

|---|---|

| 指令集架构 | Thumb-1 (most), Thumb-2 (some) |

Cortex-M0+是以Cortex-M0再进行优化的版本。Cortex-M0+支援所有Cortex-M0的指令,因此可以用相同的编译器以及除错工具。Cortex-M0+的管线由三层变成二层,因此耗能较少。除了Cortex-M0已有的除错功能外,Cortex-M0+增加了称为微追踪缓冲区(Micro Trace Buffer、MTB)的选项,有简易的指令追踪缓冲区。Cortex-M0+也有加入Cortex-M3和Cortex-M4的一些特点,是以矽智财选项的方式加入,例如记忆体保护单元(MPU),以及中断向量表重新定位[6]。

Cortex-M0+核心的主要特点有[6]:

- ARMv6-M架构[2]

- 二层管线(比Cortex-M0少一层)

- 指令集(和Cortex-M0)相同

- Thumb-1(大部份),但没有CBZ, CBNZ, IT

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR

- 32-bit硬体整数乘法,结果也是32-bit

- 1到32个中断,以及不可遮罩中断

矽智财选项:

- 硬体整数乘法速度:1周期或32周期。

- 八个区块的记忆体保护单元(MPU)(和M3、M4相同)

- 中断向量表重新定位(和M3、M4相同)

- 单一周期的I/O埠(在M0+/M23上有此机能)

- 微追踪缓冲区(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此机能)

Cortex-M1

| 微架构 | ARMv6-M |

|---|---|

| 指令集架构 | Thumb-1 (most), Thumb-2 (some) |

The Cortex-M1是特别设计可以放入FPGA晶片的内核。

Cortex-M1内核的主要特点有[7]:

- ARMv6-M架构[2]

- 二层管线

- 指令集

- Thumb-1(大部份),但没有CBZ, CBNZ, IT.

- Thumb-2(少部份),只有BL, DMB, DSB, ISB, MRS, MSR.

- 32-bit硬体整数乘法,结果也是32-bit

- 1到32个中断,以及不可遮罩中断

矽智财选项:

- 硬体整数乘法速度:3或33周期。

- 选配的紧密耦合记忆体(TCM)0 to 1 MB 指令TCM,0 to 1 MB 资料TCM,都可以选择要不要ECC.

- 外部中断:0, 1, 8, 16, 32.

- 除错模式:无,简易功能,完整

- 字节序:little-endian或BE-8 big-endian.

- 作业系统延伸:可以选择

Cortex-M3

- ARMv7-M架构[3]:

- 三层管线以及分支预测

- 指令集:

- Thumb-1(完整)

- Thumb-2(完整)

- 32-bit硬体整数乘法,结果可以是32-bit或64-bit,有号或无号,在乘法后允许加法或减法。32-bit乘法是一个周期,64-bit乘法和乘积累加(MAC)需要的周期较多

- 32-bit硬体整数除法(2–12周期)

- 支援饱和运算

- 12个周期的中断延迟

- 整合休眠模式

矽智财选项:

- 可选的记忆体保护单元(MPU):0个区或8个区

Cortex-M4

在概念上,Cortex-M4是Cortex-M3加上数位信号处理(DSP)指令、可选的浮点运算器。若有浮点运算器,会称为Cortex-M4F。

Cortex-M4内核的主要特点有[9]:

- ARMv7E-M架构[3]

- 三层管线以及分支预测

- 指令集:

- 12个周期的中断延迟

- 整合休眠模式

矽智财选项:

- 可选的浮点运算器(FPU):只有单精度IEEE-754的,称为FPv4-SP延伸

- 可选的记忆体保护单元(MPU):0个区或8个区

Cortex-M7

Cortex-M7是高性能的内核,其运算效能是Cortex-M4的二倍。其中包括六层的超纯量管线有分支预测,有可选的单精度浮点运算器或双精度浮点运算器[18][19]。指令集以及资料汇流排已由32-bit宽度增加到64-bit宽度。若内核中有FPU,会称为Cortex-M7F,不然会称为Cortex-M7。

Cortex-M7内核的主要特点有[10]:

- ARMv7E-M架构

- 6阶管线以及分支预测。在ARM Cortex-M内核中是最多的。

- 指令集:

- 1至240个中断,以及不可遮罩中断

- 12个周期的中断延迟

- 整合休眠模式

矽智财选项:

Cortex-M23

| 微架构 | ARMv8-M Baseline |

|---|---|

| 指令集架构 | Thumb-1 (most), Thumb-2 (some), 除法、TrustZone |

Cortex-M23内核在2016年10月上市[20],以2015年11月发布的ARMv8-M架构为基础[21]。在概念上Cortex-M23类似Cortex-M0+,加上整数除法指令、TrustZone安全特性、也是二层管线。

- ARMv8-M基线架构[15]

- 二层管线(类似Cortex-M0+)

- TrustZone安全指令(只有在M23/M33/M35P)

- 32-bit硬体整数除法(17 或 34 周期)(M0/M0+/M1没有)

- 堆叠边界限制(只有在SAU选项开启时才有)(M23/M33/M35P才有)

矽智财选项:

- 硬体整数乘法速度:1周期或32周期。

- 硬体整数除法速度:最长17周期或34周期,依除数而定,指令有可能会提早完成。

- 可选的记忆体保护单元(MPU):0, 4, 8, 12, 16个区块

- 可选的安全属性单元(SAU):0, 4, 8个区块

- 单一周期的I/O埠(在M0+/M23上有此机能)

- 微追踪缓冲区(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此机能)

Cortex-M33

Cortex-M33内核是在2016年10月发布[20],是以2015年11月发布的ARMv8-M架构为基础[21]。概念上类似Cortex-M4和Cortex-M23的交集,也有三阶的指令管道。

- ARMv8-M架构[15]:

- 三阶管道

- TrustZone安全指令(只有在M23/M33/M35P才有)

- 32-bit硬体整数除法(最长11个周期)(M0/M0+/M1无此选项)

- 堆叠边界限制(只有在SAU选项开启时才有)(M23/M33/M35P才有)

矽智财选项:

- 可选的浮点运算器(FPU):只有单精度IEEE-754的,称为FPv5延伸

- 可选的记忆体保护单元(MPU):0, 4, 8, 12, 16个区块

- 可选的安全属性单元(SAU):0, 4, 8个区块

- 微追踪缓冲区(Micro Trace Buffer、MTB)(在M0+/M23/M33/M35P上有此机能)

Cortex-M35P

Cortex-M35P内核是在2018年5月发布的,在概念上是Cortex-M33内核加上新的指令集,以及来自ARM SecurCore系列,新的防篡改硬体、可选的同位元以及ECC功能[22]。

目前此晶片的公开资料不多,只有技术参考手册。到2020年2月为止,尚未看到各厂商推出此系列的微处理器。

Cortex-M55

Cortex-M55是在2020年2月发布,是以2019年2月发布的Armv8.1-M架构为基础,有四阶指令管道。

Cortex-M55核心的主要特点有:

- ARMv8.1-M Mainline/Helium内核[15]

- 四阶管道

- 堆叠边界限制(只有在SAU选项开启时才有)

矽智财选项:

- Helium (M-Profile Vector Extension, MVE)

- 单精度和双精度的浮点运算器

- 可选的DSP延伸

- 可选的TrustZone安全延伸

- 支援RAS(Safety and reliability)功能

- 支援协处理器

- 区分安全区和非安全区的MPU,可以分为0, 4, 8, 12或16个区

- 安全属性单元可以分为0, 4或8个区

- 指令缓存,大小可以设定为4KB, 8KB, 16KB, 32KB, 64KB

- 资料缓存,大小可以设定为4KB, 8KB, 16KB, 32KB, 64KB

- 缓存及TCM支援ECC

- 1–480个中断

- 3–8个例外优先位元

- 内部和外部的唤醒中断控制器(WIC)选项,可选的CTI, ITM及DWT

- ARM客制指令(未来发布的版本中会支援)

文件

ARM晶片的文件很多。 过去八位元的微处理器只有一份文件,不过随著微处理器的进步,许多功能都需要支援。ARM晶片的文件包一般会包括IC制造商以及CPU内核供应商(Arm)的文件。

典型的文件结构如下:

- 文件树(从上到下)

- IC制造商网页

- IC制造商宣传投影片

- IC制造商实际晶片的数据表

- IC制造商该晶片家族的参考手册,其中有常用周边以及特点

- ARM内核网站

- ARM内核通用使用手册

- ARM内核技术参考手册

- ARM架构参考手册

IC制造商可能会有其他资料,例如开发板使用手册、应用指南、快速手册、软体函式库文件、已知问题等。

参考资料

延伸阅读

外部链接

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.