RISC-V

开源指令集架构 来自维基百科,自由的百科全书

RISC-V(英语发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),简易解释为与开源软体运动相对应的一种“开源硬体”。该项目于2010年在加州大学柏克莱分校启动,但许多贡献者是该大学以外的志愿者和行业工作者。

与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件而不必支付给任何公司专利费。虽然这不是第一个开源指令集[1],但它具有重要意义,因为其设计使其适用于现代计算设备(如仓库规模云计算机、高端移动电话和微小嵌入式系统)。设计者考虑到了这些用途中的性能与功率效率。该指令集还具有众多支持的软件,这解决了新指令集通常的弱点。[2]

RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。[3][4]

截至2021年12月,RISC-V工作小组已经批准了版本 20191213 的非特权指令集(Unprivileged ISA,曾经称为用户级指令集 User-Level ISA),以及版本 20211203 的特权指令集(Privileged ISA)。

意义

RISC-V的作者们旨在提供数种可以在BSD许可证之下自由使用的CPU设计。该许可证允许像是RISC-V芯片设计等衍生作品可以像RISC-V本身一样是公开且自由发行,也可以是闭源或者是专有财产。

相比而言,ARM控股和MIPS科技等商业芯片供应商会对使用其专利者收取高额的许可费用。[5]他们也要求在接收其描述设计优点的文件和指令集前,还需要签署保密协议。许多设计优点为完全专有,从来不会披露给客户。这种保密制度阻碍了公共教育用途和安全审核,以及开发公共、低成本的自由及开放源代码软件编译器和操作系统。[来源请求]

处理器设计需要多种专业的设计知识,包括电子逻辑、编译器和操作系统,这种资源很难在专业工程团队之外见到。所以现代且高质量的通用计算机指令集近年来除了学术环境以外并没有在任何地方被广泛使用,甚至没有被阐述。正因如此,许多RISC-V贡献者将此视为整个社群付出的成果,而这也是RISC-V有很多工程上的应用的一项原因。

RISC-V的作者们还有大量研究和使用者经验来验证他们在硅片和仿真中的设计。RISC-V指令集是从一系列的学术计算机设计项目直接发展而来的。它一开始的目的有一部分是为了帮助这些项目。

历史

RISC的历史可追溯到1980年左右。[6]在此之前,人们觉得简单的计算机可能会有用,但是没有很多人去阐述其设计原则。这种简单而有效的计算机一直都是学术界的兴趣。

学术界的学者们为了出版第一版的《计算机体系结构:量化研究方法》(Computer Architecture: A Quantitative Approach)ISBN 978-1558600690 ,所以于1990年订立了RISC指令集DLX。大卫·帕特森(David Patterson)是其中一位作者,后来协助RISC-V的开发。但是DLX只用于教育用途,学术界和业馀爱好者使用FPGA来实做它,但并没有取得商业运用。

版本2及更早版本的ARM CPU具有公共域指令集,并且仍有GCC的支持。该指令集有三个开源内核,但从未被制造。

OpenRISC是一款基于DLX的开源指令集,并且具有相关的RISC设计。OpenRISC 完全支持GCC并且有实做在Linux上,但是它很少有商业上的实做。

加州柏克莱分校的Krste Asanović教授发现开放原始码的电脑系统有很多用途。在2010年他决定用三个月的时间来开发并发表一个开放原始码的电脑系统。这个计画是用来帮助包括学术以及工业的使用者。柏克莱分校的大卫·帕特森教授也参加了这个计画。帕特森也是原来伯克利分校RISC的设计者,RISC-V只是他众多RISC CPU研究计画的一个.RISC-V计画早期一些经费来自DARPA。

有参与支援RISC-V基金会的公司以及机构包括了超微半导体、晶心科技、英国航太系统、加州大学伯克利分校、Bluespec、Cortus、Google、GreenWaves Technology、慧与科技、华为、IBM、Imperas Software、中国科学院、北京清华大学、印度理工学院、莱迪思半导体、迈伦科技、美高森美、美光科技、辉达、恩智浦半导体、甲骨文公司、高通、Rambus、威腾电子、SiFive、阿里巴巴集团、红帽公司、成为资本[7]。

2019年6月,图灵奖得主、RISC-V基金会创始人之一大卫·帕特森(David Patterson)在瑞士宣布,将依托清华-伯克利深圳学院(TBSI),在内部建设RISC-V国际开源实验室(RISC-V International Open Source Laboratory),又称大卫帕特森RIOS图灵实验室。清华大学称实验室将瞄准世界CPU产业战略发展新方向和粤港澳大湾区产业创新需求,[2]聚焦于开源指令集CPU研究,建设以深圳为根节点的RISC-V全球创新网络和以技术成果转移为主要使命的非营利组织,全面提升RISC-V生态系至最先进可商用水平。预判届时将面对国际大厂法律层面发起挑战问题上,伯克利加州大学和清华大学的法学院将与之建立联系。[2]

2020年3月,RISC-V基金会为规避美国对中国的贸易限制而将总部搬迁至瑞士[8],并更名为RISC-V国际(英语:RISC-V International),以非盈利商业协会的身份在瑞士注册[9]。

激励要求

RISC设计者们认为指令集因为位于硬体和软体之间,所以是电脑主要的沟通桥梁,因此如果有一个设计良好的指令集是开源而且可以被任何人使用的,就可以让更多的资源能够重复利用,而大大的减少软体的成本。而这样的指令集也会增加硬体供应商市场的竞争力,因为硬体供应商们可以挪用更多资源来进行设计,减少处理软体支援的事务。[10]

设计者声称在指令集设计领域里,新的设计准则渐渐变得罕见,而近四十年中,大多数成功的设计变得越来越相似。至于那些失败的指令集,大多数是因为他们的赞助商赚不了钱,而不是因为其指令集在技术上有多差。所以,一个在成熟的设计准则之下开发且设计良好的开源指令集想必能吸引许多供应商长期的支援。[10]

许多先前的开源指令集架构使用GNU通用公共授权条款来鼓励使用者们允许他们的实作方法被其他人复制或是使用。

设计者们表示,RISC-V指令集是给实际上的电脑使用的,它不像其他学术上的指令集设计,只有为了比较好阐述理念而做最佳化。而RISC-V指令集有一些功能是可以增加电脑速度又可以减少成本和电源使用。这些特色包含,Load/store架构,在CPU里面的位元表示方法来简化数据多工器(MUX),以标准为基础来简化的浮点数,架构中立的设计和把最高有效位(Most significant bit,MSB)放到固定位置来加速符号扩充(Sign extension)。而sign extension常常就是静态时序分析里面的关键路径(Critical timing path)[11]。

RISC-V 指令集是设计来给各式各样的用途使用的,而它支援三个不同的字组大小,分别是32位元、64位元、128位元以及与这三种字组大小有关的各式各样的指令子集。而这些指令子集的定义会按照那三个字组大小来做些微的改动。透过这些指令子集的向量处理器与资料中心等级的机柜式平行电脑/平行运算来帮助嵌入式系统、个人电脑和超级电脑。

该指令集采取不固定的编码长度而且还可以再扩充,因此在未来,还可以一直加入更多位元的编码方式。该指令集有特别留空间给128位元的延伸版本,因为60年的产业界经验显示在指令集设计领域里,最无法复原的错误就是缺少记忆体定址空间。截至2016年,128位元的指令集仍然刻意地维持在“未冻结”的状态,这是因为到现在为止,人们很少有实际上操作这么大记忆体的系统的经验。[11]

然而,RISC-V也可以拿来做学术上的使用。它拥有简化的整数指令子集允许学生拿来做基本的练习,而整数指令子集就是一个简单的指令集架构(ISA)让软体可以控制研究上的机器。而不定长度的指令集架构也允许扩充功能来满足研究或是学生练习上的需求。[11]分割出来的特权指令集可以支援在不重新设计编译器的情况下,进行作业系统方面的研究。[12]RISC-V的开放的智慧财产权允许相关的设计被发布、使用和修改。[11]

软件

一个新的CPU指令集通常的问题是缺少CPU的硬体设计跟软体的支援。在RISC-V的网站有一个user mode指令集的规格,还有一个用来支援作业系统模式的优先指令集的初步规格。

市面上已经有好几个使用RISC-V开源架构的CPU设计可以供参考,包括64-bit Berkeley Out of Order Machine(BOOM)[13]、64-bit Rocket[14]、柏克莱设计的五个32-bit Sodor CPU[3]、Clifford Wolf 的 picorv32、Syntacore 的 scr1、苏黎世联邦理工学院/波隆纳大学的 PULPino (Riscy and Zero-Riscy)[15],以及很多其他的设计。使用三层指令分段的 Sodor CPU 是一个适合嵌入式设计的小型CPU。Rocket可能适用在小型低功耗的个人电脑或其他个人装置。BOOM 使用了大部分Rocket的架构,但是功能更加强大,适合个人电脑、伺服器或超级电脑。picorv 跟 scr1 都是使用Verilog 设计的 32位元 MCU 等级的 RV32IMC。PULPino的核心使用了一个适合微控制器的简单的 RV32IMC ISA架构(Zero-Riscy),以及另外一个更强大的DSP版本 RV32IMFC ISA 可以支援一些嵌入式信号处理的特别 DSP 指令集。

设计软体包括了一个设计编译器 Chisel,它可把设计编译成Verilog代码。网站上还有测试用的参考资料可以用来验证设计的正确性。

RISC-V目前提供的软体有 GNU Compiler Collection (GCC) toolchain(具有侦错器 GDB)、一套 LLVM toolchain、OVPsim模拟器(以及RISC-V快速处理器模式的软体参考库)、Spike 模拟器,以及一套在QEMU上运行的模拟器。

作业系统的支援包括 Linux 核心、FreeBSD,以及 NetBSD,但是监督模式的指令直到版本 1.11 的特权指令集才被标准化[12],所以这方面的支援还不是正式的。有一个早期的 RISC-V 的FreeBSD 作业系统已经在2016年2月上传到开放原始码社群,而且包含在 FreeBSD 11.0[16][17] 。Debian[18]跟Fedora[19]的版本也有人在移植,并且在逐渐稳定中。已经有人做了一个 Das U-Boot 的移植版本。[20]UEFI Spec v2.7 定义了RISC-V UFEI 的规格,而且慧与科技公司的工程师已经做好一个 TianoCore 的移植版本,并且将会上传到开放原始码社群。已经有人做好了一个 L4 microkernel family 的移植[21]。还有一个在网页上用JavaScript写的 RISC-V Linux 系统模拟器[22]。

设计

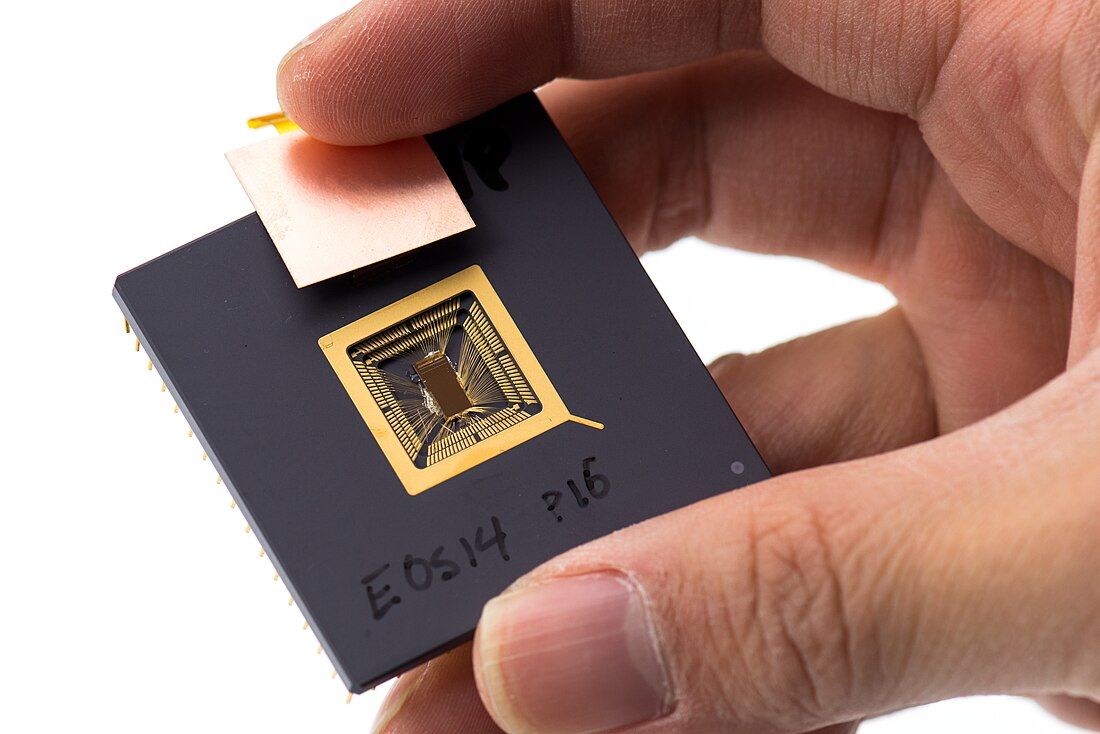

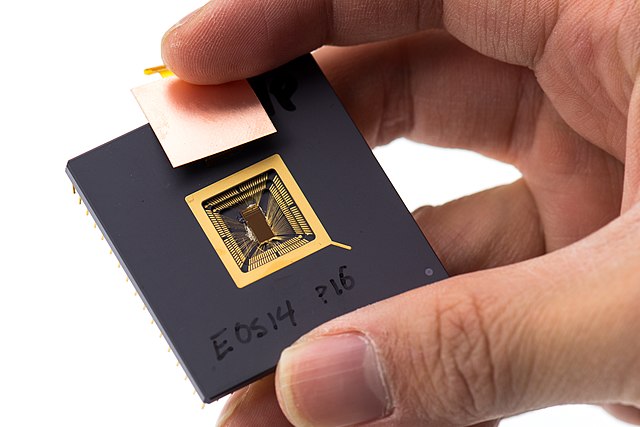

RISC-V处理器

参见

参考资料

拓展阅读

外部链接

Wikiwand - on

Seamless Wikipedia browsing. On steroids.