Atmel AVR

来自维基百科,自由的百科全书

Atmel AVR系列是一种基于改进的哈佛结构、8位~32位精简指令集(Reduced Instruction Set Computing,RISC)的微控制器,由Atmel公司于1996年研发。AVR系列是首次采用闪存(Flash Memory)作为数据存储介质的单芯片微控制器之一,同时代的其它微控制器多采用一次写入可编程ROM、EPROM或是EEPROM。

目前AVR处理器发展了六个系列,分别是:tinyAVR,ATtiny系列;megaAVR,ATmega系列;XMEGA,ATxmega系列;Application-specific AVR,面向特殊应用的AVR系列,增加LCD控制器、USB控制器、PWM等特性;FPSLIC,FPGA上的AVR核;AVR32,32位AVR系列,包含SIMD和DSP以及音视频处理特性,与ARM架构形成竞争。

发展简史

AVR架构最早由两名挪威理工学院(Norwegian Institute of Technology,NTH)的学生Alf-Egil Bogen和Vegard Wollan共同构思出来。[1][2]

原始的AVR微控制单元由当地Trondheim的一所特殊应用集成电路(ASIC)工作室Nordic VLSI(现为北欧半导体)负责开发。当时它被称作μRISC(Micro RISC),还可使用Nordic VLSI的硅晶圆等基础材料来制作其芯片。当这些技术被Nordic VLSI卖给Atmel后,其内部架构被当时任职于Atmel挪威子公司的Bogen以及Wollan进一步发展。架构设计者们和来自IAR系统公司的编译器编写者们紧密合作,来确保指令集提供更高效率的高级编程语言编译。[3]

而在命名上,Atmel解释‘AVR’这个名称不是某几个单词的缩写,也不代表任何特别的事物。AVR的创造者们也没有给出明确的关于‘AVR’之表意的答案。[2]然而,一般认为,‘AVR’表示Alf (Egil Bogen) and Vegard (Wollan)'s RISC processor。[4]而本文里用的‘AVR’一般指8位RISC的Atmel AVR微控制器的产品线。

首个AVR微控制器的产品线是AT90S8515,拥有和英特尔8051微控制器相同的40针双列直插封装(DIP),包括外部多路地址和资料总线。但RESET线和英特尔8051相反,8051的是高电平有效RESET,而AVR是低电平有效RESET,但除此以外,其它针脚是完全一致的。

设备概览

AVR是一个修改过的哈佛架构计算机,程序和资料分别存储在各自的拥有不同寻址空间的物理内存系统上,但有能力使用特殊的指令可从程序存储器内读取资料项。

AVR分为六大家族系列:

- tinyAVR — ATtiny系列

- 0.5~16kB的程序存储器

- 6~32管脚封装

- 有限的外围设备集合

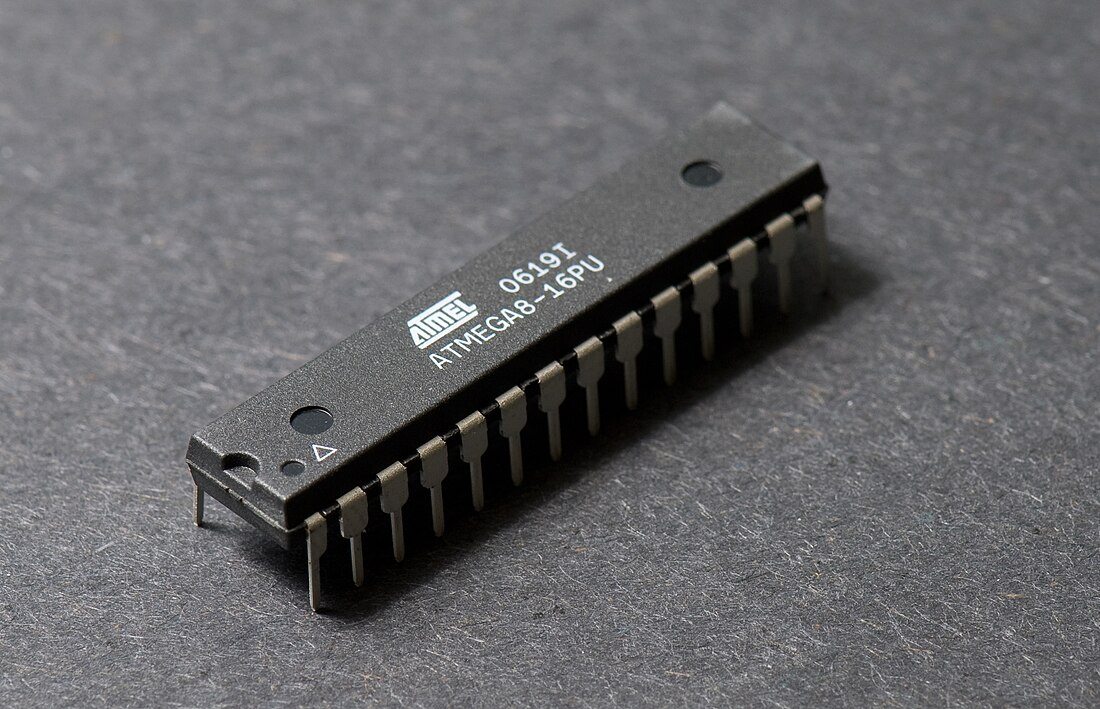

- megaAVR — ATmega系列

- 4~512kB的程序存储器

- 28~100管脚封装

- 扩展指令集(乘法指令和管理更大容量的程序存储器管理指令)

- 更多的外围设备集合

- XMEGA — ATxmega系列

- 16~384kB程序存储器

- 44~64~100管脚封装(A4、A3、A1)

- 扩展性能特性,像是DMA、‘事件系统’、以及加密支持

- 更多外围设备集,包含模拟数字转换器(ADC)

- FPSLIC (AVR with FPGA) — 载于FPGA上的AVR核心

- 32-bit AVRs — 32位AVR

闪存、电子抹除式可复写只读存储器(EEPROM)、以及静态随机存储器(SRAM)都内置于一颗芯片上,在大部分应用中尽可能无需外部存储器。一些设备拥有并行的外部总线选择以允许加入额外的资料存储器或存储器映射设备。几乎所有的设备(除最小规模TinyAVR芯片以外)拥有串列总线,可以用来连接更大的串列EEPROM或闪存。

程序指令被存储于非易失性的闪存上。尽管微控制器只有8位,但每指令可以访问1至2个16位的字节。

程序存储器的容量大小常用于设备命名(如ATmega64x产品线拥有64KB的闪存,ATmega32x产品线拥有32KB的闪存)

不支持扩展程序存储器,所有由AVR核心执行的代码皆需要存储于内部的存储器。然而AT94 FPSLIC AVR/FPGA芯片没有这种限制。

资料寻址空间由寄存器文件、输出/输入寄存器、和SRAM组成。

AVR拥有32个的寄存器,分别为( R0 到 R31 )并被归类为8位RISC设备。

在大部分AVR架构上,工作寄存器被映射为首位的32个存储器地址(000016–001F16)接着是64个输出/输入(I/O)寄存器(002016–005F16)。

实际上SRAM是在这些寄存器分段(寻址为006016)后开启。(注意输出/输入寄存器空间在一些扩展设备上或许更大,使得加载存储器映射I/O寄存器将占用一部分SRAM的寻址空间)

虽然有这些分开的寻址解决方案和优化的寄存器文件和I/O寄存器访问操作码,但它们全部都可以被加以处理和操作,就像它们都在SRAM上。

在XMEGA系列上,工作寄存器文件并没有映射到资料寻址空间上;正因为如此,不能将XMEGA的工作寄存器像是在SRAM上那样对待。作为替代,I/O寄存器被映射到资料寻址空间内非常靠前的位置上。另外,资料寻址空间中用作I/O寄存器的总数上大幅增加,容量达到4096字节(000016–0FFF16)。然而,正如前代产品一样,快速I/O操作指令只可到达首先的64个I/O寄存器位置(首位的32个位置是给位操作指令使用的)。往后的I/O寄存器,XMEGA系列预留了一个4096比特宽度地址空间范围,可被选作将内置EEPROM映射至资料寻址空间上(100016–1FFF16)。实际可用的SRAM位于这些被占用的寻址空间以后,从200016开始。

几乎所有的AVR微控制器都拥有内置的EEPROM,用来提供半永久的资料存储。和闪存一样,EEPROM可在断电以后维持其内存储的资料。

在大部分的AVR架构中,内部EEPROM存储器并没有映射到微控制单元的可寻址存储器空间上。它只可和外挂的外围设备一样使用特别的指针寄存器和读/写指令来访问,这使得EEPROM的访问速度要比其它内置的随机存储器(RAM)要慢不少。

然而,某些SecureAVR(AT90SC)家族系列的设备[6]使用了一种特殊的EEPROM根据相关配置设置映射至资料或程序存储器。XMEGA家族系列也允许EEPROM映射至西辽寻址空间上。

因EEPROM的擦写次数不是无限的——Atmel的技术细明规格表上标明是100,000次擦写周期——一个设计精良的EEPROM擦写常程序应比较EEPROM地址上的内容和请求写入的内容并在需要进行改变的位置处才真正执行写入操作。

注意,在很多情况下擦除和写入是分开执行的,以字节为单位进行,这有助于延长其使用寿命,因比特仅需全被设置为‘1’(擦除)或选择性地置‘0’(写入)。

Atmel的AVR核心拥有二阶单级流水线设计。这意味着处理器可以在执行现在的指令同时将下一个指令读取。绝大部分的指令执行仅需一到两个时钟周期,使AVR核心在众多8位微控制器中是最快的。

AVR核心被设计为能够高效运行经编译的C语言程序,还内置了数个指针指令与之相适配。

AVR指令集系统相比其它大多数的比特微控制器的,正交指令集要多出不少,尤其是AVR当下的竞争对手英特尔8051以及其仿制品和PIC微控制器。然而,这不完全是固定的:

- 指针寄存器 R26 至R31 是X、Y和Z拥有的寻址能力,彼此是不同的

- 寄存器位置R0至R15和寄存器R16至R31拥有不同的寻址能力

- 输出/输入端口0~31和端口32至63拥有不同的寻址能力

- 当SER不影响标志时CLR会影响标志,即使它们是互补指令。CLR设置所有比特为“零”而SER指令则设置所有比特为“一”。(注意,CLR指令是EOR R, R的虚假操作;SER指令是LDI R,$FF的短指令。数学运算时当遇到搬移/加载/存储/分支,像是EOR会变更标志而像是LDI的则不会)

- 读取存储在程序存储器(快闪型)的唯独资料时要用到特殊的LPM指令;闪存总线会为指令存储器保留。

此外,一些芯片差异会影响代码的生成。代码指针(包括在堆栈上的返回地址)在芯片上是两个字节长度以及有高达128KB的闪存,但在一些更大的芯片上变成3个字节长度;并不是所有的芯片都有硬件乘法器;拥有超过8KB闪存的芯片拥有分支和附带更大范围的传唤指令;或者四者都有。

通常的规则指令集使得可直接使用C(或者甚至Ada)编译器来对AVR进行编程。GCC也在离目前相当长的时间以前就支持包括AVR在内的多种微控制器,而且还被广泛使用。事实上,Atmel也从为小型微控制器用的编译器的主要开发者当中征集并导入他们的作品。以确定高级编程语言编译器中最常用的指令集特性。

AVR系列可以很好地支持0~20MHz的主频,某些设备更达到32MHz。更低功耗的作业一般需要一个较低的主频。所有最近的AVR设备(Tiny、Mega、以及Xmega,但90年代的产品除外)有内置石英振荡器、可以不需要外接时钟或震荡器电路。一些AVR设备还有一个系统时钟预定标器,提升系统时钟至1024。这个预定标器可以被软件执行时重新配置,允许对主频进行优化作业。

因所有在寄存器R0至R31位址的运算作业仅需一个主频,AVR可以拥有每兆赫(MHz)最高每秒一百万指令(MIPS),换言之一颗8MHz的AVR处理器拥有8MIPS的性能。从存储器加载和存储资料需要两个主频,分支也需要两个主频。在一些较新的‘3字节PC’上,像是ATmega2560的设备,分支操作会比之前的设备慢上一个主频。

AVR由于开发工具可轻易免费或低价获得,包括一些合适价格的开发板设备和免费的开发软件,而拥有庞大的开发群体。AVR也以众多不同的名义贩售,但它们都使用相同的基本核心,只是周边设备和存储器的搭配不一样。每个系列的不同芯片之间的兼容性相当好,尽管输出输入控制器的搭配会有所不同。

更多可参见#外部链接一节中与AVR开发的相关站点。

编程界面

有多种方法可将程序加载至AVR芯片上。不同AVR家族系列的程序写入方法都各有不同。

高电压平行编程(High voltage parallel programming,HVPP)是作为‘最后手段’来使用,亦可能是以坏熔丝设置修复AVR芯片的唯一方法。

大部分的AVR型号可以保留一个开机加载程序区域,有256字节至4KB的大小,可存储多次编程的代码。在复位后,首先执行bootloader,然后终止一些用户运行的程序,当需要重新变成或跳转至主程序时。在任何界面可用时,代码便可以进行重新编程,像PXE(预启动执行环境)一样,透过以太网适配器能读取加密处理的二进制资料。Atmel有关于许多总线接口的应用程序注释及源码。[7][8][9][10]

AT90SC系列的AVR芯片可以使用原厂掩模ROM而不使用闪存来作为程序存储器。[11] 因为在大批量生产基于AVR的特定功能控制器时,比起在开发阶段使用价格较高的闪存,在生产阶段使用掩模ROM可以有效提高成本效益。

aWire是一种新的单线调试界面,可用于新版UC3L AVR32设备上。

参见

- Arduino

- AVR32

参考资料

扩展阅读

外部链接

Wikiwand - on

Seamless Wikipedia browsing. On steroids.