热门问题

时间线

聊天

视角

组合逻辑电路

来自维基百科,自由的百科全书

Remove ads

在数字电路理论中,组合逻辑电路(英语:Combinatorial logic, combinational logic)是一种逻辑电路,它的任一时刻的稳态输出,仅仅与该时刻的输入变量的取值有关,而与该时刻以前的输入变量取值无关。相对于组合逻辑电路,时序逻辑电路的输出结果除了依照目前的输入外也和先前的输入有关系。从电路结构分析,组合电路由各种逻辑门组成,网络中无记忆器件,也无反馈线。

组合逻辑是在电脑被用来做输入的信号跟储存的资料作逻辑代数运算之用。实际上电脑电路都会混用包含组合逻辑和时序逻辑的电路。举例来说,算术运算逻辑单元(ALU)中,尽管ALU是由循序逻辑的程序装置所控制,而数学的运算就是从组合逻辑制产生的。计算机中用到的其他电路,如半加器、全加器、半减器、全减器、数据选择器、数据分配器、编码器和译码器也用来构成组合逻辑电路。

Remove ads

组合电路的分析

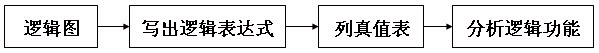

由已知的逻辑电路图,找出输入变量和输出函数之间的逻辑关系,达到分析电路功能,评价设计好坏,维护系统硬件,改善电路设计的目的,这个过程称为数字电路的逻辑分析。

组合电路分析的步骤:

组合电路的设计

逻辑设计又称为逻辑综合,根据给定的逻辑条件或者提出的逻辑功能,整理出满足该逻辑的电路,这个过程称为数字电路的逻辑设计。

组合逻辑系统的实际设计可能要考虑实际逻辑器件对输入变化作出反应的时间。输出是由多个不同路径、不同时亮的开关器件组合而成时,由于变化沿不同路径传播,输出在稳定到稳态之前可能会发生瞬间改变。[1]

组合逻辑的构建通常是两种方法之一:积之和,或和之积。考虑以下真值表:

用乘积相加法,将所有输出真的语句相加:

运用布尔代数,输出可简化为真值表的等价:

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads

,

,  ...

...