Loading AI tools

De PowerPC 600-familie (ook PPC600) verwijst naar de eerste serie van PowerPC-processoren die voortkwamen uit de alliantie tussen Apple Computer, IBM en Motorola. De eerste microprocessor in deze familie was de PowerPC 601 uit 1993. De tweede generatie volgde in 1994 met de PowerPC 603 en 604. Hoewel beide nog steeds een 32-bits RISC-ontwerp hadden, was de PowerPC-instructiesetarchitectuur vanaf het begin ontworpen als een 64-bits architectuur. De PowerPC 620 uit 1995 was de eerste 64-bit PowerPC-processor.

| POWER-, PowerPC- en Power ISA-architectuur |

|---|

| Historisch |

|

POWER · POWER2 · POWER3 · POWER4 · POWER5 · PPC6xx · PPC7xx · PPC74xx · PPC970 · PowerPC-AS · Broadway |

| Huidig |

|

e200 · e300 · e500 · e600 · e5500 · e6500 · PA6T · POWER6 · POWER7 · POWER8 · POWER9 · Power10 · PPC4xx · Cell PPE · Xenon |

| Geannuleerd |

| Gerelateerde links |

|

OpenPOWER Foundation · RISC · AIM-alliantie · System p · Power.org · PAPR · PReP · CHRP · AltiVec |

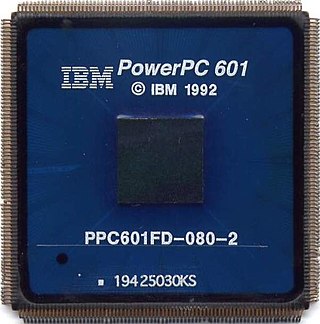

De PowerPC 601 was de eerste generatie microprocessors die de standaard 32-bits PowerPC-instructieset ondersteunde. Het ontwerp ervan startte halverwege 1991 en de eerste prototypechips waren beschikbaar in oktober 1992. De 601 was de eerste geavanceerde single-chip implementatie van de Power-architectuur. Om de processor in een recordtempo op de markt te kunnen brengen maakte de ingenieurs gebruik van een groot deel van de basisstructuur en delen van de IBM RISC Single Chip (RSC)-processor,[1] maar voegden ook ondersteuning toe voor de overgrote meerderheid van de nieuwe PowerPC-instructies die niet in de POWER-instructieset voorkomen.

De 601 is ontworpen voor een breed scala aan toepassingen en ondersteunt externe L2-cache en symmetric multiprocessing. De chip had vier functionele eenheden, waaronder een floating-point unit, een arithmetic logic unit, branch unit and a sequencer unit. De processor bevatte ook een memory management unit. De integer-pipeline was vier stappen lang, de branch-pipeline twee stappen, de geheugen-pipeline vijf stappen en de floating-point-pipeline zes stappen.[2]

De processor werd door IBM aangeboden als de PPC601 en door Motorola als de MP601, met kloksnelheden variërend van 50 tot 80 MHz. De chip bevat 2,8 miljoen transistoren en heeft een uniforme L1-cache van 32 KB, wat in die tijd behoorlijk veel was. Mede dankzij deze grote cache werd de 601 beschouwd als een krachtige processor in zijn segment, die beter presteerde dan de concurrerende Intel Pentium. De PowerPC 601 werd gebruikt in de eerste Power Macintosh-computers van Apple en in diverse RS/6000-werkstations en SMP-servers van IBM en Bull.

PowerPC 601v

In 1994 introduceerde IBM de PowerPC 601v of PowerPC 601+, een bijgewerkte versie van de 601 met een kloksnelheid van 90 tot 120 MHz. Deze processor werd uitsluitend door IBM geproduceerd op basis van een nieuwer CMOS-proces.

De PowerPC 603 was de eerste processor die de volledige 32-bit PowerPC-architectuur implementeerde zoals gespecificeerd. De 603 is ontworpen als een goedkope processor met laag vermogen voor gebruik in draagbare apparaten. Een van de belangrijkste kenmerken waren de energiebesparende functies die het stroomverbruik drastisch konden verminderen, waarbij in de slaapmodus slechts 2 mW werd verbruikt. De 603 bevat 1,6 miljoen transistoren en heeft aparte 8 KB L1-caches voor instructies en gegevens en een 32/64 bit 60x geheugenbus. De 603-kern had geen hardwareondersteuning voor SMP.[2]

De 603-architectuur is de directe voorloper van de PowerPC 750-architectuur, door Apple op de markt gebracht als de PowerPC G3. De 603 was bedoeld voor gebruik in de Apple PowerBook laptopfamilie, maar was wegens zijn kleinere processorcaches niet performant genoeg om 68K-emulatiesoftware te draaien. Als gevolg hiervan gebruikte Apple de 603 alleen in zijn goedkope desktopmodellen van de Performa-lijn.[3] Omdat Apple ervoor koos om te wachten op een processorrevisie liep de introductie van de PowerBook 5300 en de PowerBook Duo 2300 vertraging op.[4] Het gebruik van de 603 in de Performa 5200-lijn leidde ertoe dat de processor een slechte reputatie kreeg. Afgezien van de povere prestaties bij het uitvoeren van 68K-emulatiesoftware kregen de Performa-machines af te rekenen met een verscheidenheid aan ontwerpfouten, waaronder slechte netwerkprestaties en -stabiliteit, busproblemen, ROM-bugs en trage harde schijven.[5][6] Geen van de problemen van de 5200-lijn, afgezien van de 68K-emulatieprestaties, was inherent te wijten aan de 603. Het fundamentele probleem was dat de processor gebruikt werd in combinatie met 68K-moederborden en andere verouderde onderdelen.[7]

PowerPC 603e en 603ev

De prestatieproblemen van de 603 werden aangepakt in de PowerPC 603e. De L1-cache werd vergroot en uitgebreid tot 16 KB vierweg set-associatieve caches voor instructies en gegevens. Ook de kloksnelheid van de processors werd verdubbeld tot 200 MHz. Door het fabricageproces te verkleinen haalde de PowerPC 603ev zelfs snelheden tot 300 MHz. De 603e en 603ev hebben elk 2,6 miljoen transistoren.

De PowerPC 603e die gebruikt werd in de Power Macintosh 6500 was de eerste reguliere desktopprocessor die 300 MHz bereikte. Ook de BeBox van Be Inc. was opgebouwd rond de 603e, wat opmerkelijk was omdat de BeBox een multiprocessing-systeem is en daar was de 603 niet voor ontworpen. IBM gebruikte Power PC 603e-processoren in de IBM ThinkPad 800-serie. Verder dook de 603e onder andere ook op in digitale oscilloscopen en satellieten.

G2

De PowerPC 603e-kern, door Freescale omgedoopt tot G2, vormt de basis voor veel ingebedde PowerQUICC II-processoren en wordt als zodanig voortdurend verder ontwikkeld. De PowerQUICC II SoC-processoren van Freescale worden aangeduid als MPC82xx[8] en zijn verkrijgbaar in verschillende configuraties tot 450 MHz. De naam G2 wordt ook gebruikt als retroniem voor de 603e- en 604-processoren om aan te sluiten bij de G3, G4 en de G5.

e300

Freescale heeft de 603e-kern verder verbeterd in de PowerQUICC II Pro embedded processors en omgedoopt tot e300. Er zijn grotere L1-caches van 32/32 KB en andere prestatieverbeterende maatregelen toegevoegd. De PowerQUICC II Pro SoC-processors van Freescale zijn verkrijgbaar in een verscheidenheid aan configuraties met snelheden tot 667 MHz.

De PowerPC 604 kwam samen met de PowerPC 603 in december 1994 op de markt. De 604 was ontworpen als een krachtige processor voor werkstations en instapservers en bood als zodanig ondersteuning voor symmetric multiprocessing in hardware. De 604 werd op grote schaal gebruikt in de topmodellen van de Apple Power Macintosh-reeks, alsook in Macintosh-klonen, in de low-end RS/6000-servers en werkstations van IBM, in Amiga-acceleratorkaarten en als een ingebedde CPU voor telecomtoepassingen.

De 604 is een superscalaire processor die vier instructies tegelijkertijd kan lanceren. De 604 heeft een pipeline met zes stappen en zes uitvoeringseenheden: twee eenvoudige en één complexe arithmetic logic unit, één floating-point unit, één branch unit die de out-of-order execution beheert en één load/store unit. Deze uitvoeringseenheden kunnen parallel werken, waarbij in elke cyclus maximaal zes instructies kunnen voltooid worden. De chip heeft afzonderlijke L1-caches van 16 KB voor gegevens en instructies. De externe interface is een 32- of 64-bits 60x-bus die werkt met kloksnelheden tot 50 MHz.[2] De PowerPC 604 bevat 3,6 miljoen transistoren en haalde snelheden tussen 100 en 180 MHz.[9] De chips werden zowel door IBM als door Motorola vervaardigd.

PowerPC 604e

De PowerPC 604e werd geïntroduceerd in 1996 en voegde een condition register unit en aparte L1-caches van 32 KB voor instructies en gegevens toe. In combinatie met diverse verbeteringen in het geheugensubsysteem en de branch prediction unit resulteerde dit in een prestatieverbetering van 25% vergeleken met zijn voorganger. De 604e bevat 5,1 miljoen transistoren, met kloksnelheden variërend van 166 tot 233 MHz.

PowerPC 604ev "Mach5"

De PowerPC 604ev, 604r of "Mach 5" werd geïntroduceerd in augustus 1997 en was in wezen een 604e die door IBM en Motorola vervaardigd werd op basis van een nieuwer proces, dat hogere snelheden toeliet met een lager energieverbruik. De chip werkte met snelheden tussen 250 en 400 MHz en ondersteunde een geheugenbus tot 100 MHz.

IBM gebruikte de 604ev gedurende een aantal jaren in de instapmodellen van de RS/6000-reeks. Apple liet de 604ev in 1998 vallen en schakelde over op de PowerPC 750.

De PowerPC 620 was de eerste implementatie van de volledige 64-bit PowerPC-architectuur. Het was net als de 603 en 604 een PowerPC van de tweede generatie, maar dan specifiek bedoeld voor de high-end werkstation- en servermarkt. De 620 zou aanvankelijk samen met de 603 en 604 gelanceerd worden, maar zijn introductie werd uitgesteld tot 1997. Toen de 620 eindelijk op de markt kwam bleken zijn prestaties ondermaats en was hij minder performant dan de aanzienlijk goedkopere 604e.[10][11] De 620 werd daarom weinig gebruikt en is nooit in grote aantallen geproduceerd.

De chip bevat 6,9 miljoen transistoren en werkte met kloksnelheden tussen 120 en 150 MHz. Het ontwerp van de 620 leek sterk op dat van de 604, met een pipeline met vijf stappen, dezelfde ondersteuning voor symmetric multiprocessing en hetzelfde aantal uitvoeringseenheden. De 620 had bovendien grotere instructie- en datacaches van 32 KB, ondersteuning voor een L2-cache met een capaciteit van 128 MB en krachtigere branch- en load/store units met meer buffers. De tabel in de branch prediction unit was groter en kon meer instructies lanceren waardoor de 620 de out-of-order execution efficiënter kon afhandelen dan de 604. De floating-point unit werd ook verbeterd ten opzichte van de 604 met ondersteuning in hardware voor verschillende belangrijke instructies zoals het berekenen van vierkantswortels.[2]

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.