La mémoire vive dynamique (en anglais DRAM pour Dynamic Random Access Memory) est un type de mémoire vive compacte et peu dispendieuse.

La simplicité structurelle de la DRAM — un pico-condensateur et un transistor pour un bit — permet d'obtenir une densité élevée. Son inconvénient réside dans les courants de fuite des pico-condensateurs : l'information disparaît à moins que la charge des condensateurs ne soit rafraîchie avec une période de quelques millisecondes. D'où le terme de dynamique. A contrario, les mémoires vives statiques (SRAM) n'ont pas besoin de rafraîchissement mais utilisent plus d'espace.

Sans alimentation, la DRAM perd ses données, ce qui la range dans la famille des mémoires volatiles.

La mémoire DRAM utilise la capacité parasite drain/substrat d'un transistor à effet de champ.

Les puces mémoires sont regroupées sur des supports SIMM (contacts électriques identiques sur les 2 faces du connecteur de la carte de barrette) ou DIMM (contacts électriques séparés sur les 2 faces du connecteur).

Types de mémoire vive dynamique

Les mémoires vives dynamiques ont connu différentes versions :

- EDO : (de l'anglais Extended Data Out). Mémoire vive utilisée dans les ordinateurs au début des années 1990 avec la génération des Pentium première génération[1]. Elle est devenue obsolète dès 1997.

- SDRAM : de l'anglais Synchronous Dynamic RAM. Elle est utilisée comme mémoire principale et vidéo. La transition s'est faite lors du passage du Pentium II au Pentium III. Les différents types de SDRAM se distinguent par leur fréquence de fonctionnement, typiquement 66,100 et 133 MHz. Les barrettes comportent 168 broches. Elle est obsolète aujourd'hui.

- VRAM : de l'anglais Video RAM. Présente dans les cartes graphiques. Elle sert à construire l'image vidéo qui sera envoyée à l'écran d'ordinateur via le convertisseur RAMDAC.

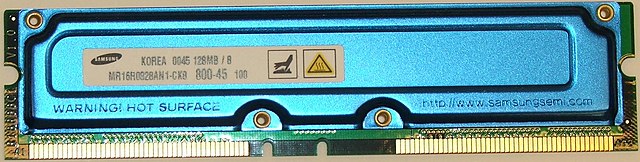

- RDRAM : de l'anglais Rambus Dynamic RAM. Développée par la société Rambus, elle souffre notamment d'un prix beaucoup plus élevé que les autres types de mémoires et de brevets trop restrictifs de la part de la société créatrice. Elle est utilisée pour les machines de génération Pentium III et Pentium 4.

- DDR SDRAM : de l'anglais Double Data Rate Synchronous Dynamic RAM. Utilisée comme mémoire principale et comme mémoire vidéo, elle est synchrone avec l'horloge système mais elle double également la largeur de bande passante en transférant des données deux fois par cycle d'horloge au lieu d'une seule pour la SDRAM. On distingue les DDR PC1600, PC2100, PC2700, PC3200, etc. Le nombre représente la quantité théorique maximale de transfert d'information en Mégaoctets par seconde. Elle s'est généralisée dans les ordinateurs grand public avec les générations Pentium III et Pentium 4. Elle comporte 184 broches. Cette mémoire est en voie de disparition avec le retrait des ordinateurs[Lesquels ?] du début des années 2000[réf. nécessaire].

- DDR2 SDRAM : de l'anglais Double Data Rate two SDRAM. Il s'agit de la 2e génération de la technologie DDR. Selon la fréquence d'utilisation recommandée on distingue les DDR2-400, 533, 667, 800 et 1066. Le nombre (400, 533, etc.) étant la fréquence de fonctionnement. Certains constructeurs privilégient la technique d'appellation basée sur la quantité de données théoriquement transportables (PC2-4200, PC2-5300, etc.), mais certains semblent retourner à la vitesse réelle de fonctionnement afin de distinguer plus clairement la DDR2 de la génération précédente. Elle comporte normalement 240 broches.

- DDR3 SDRAM : de l'anglais Double Data Rate three SDRAM. Il s'agit de la 3e génération de la technologie DDR. Les spécifications de cette nouvelle version sont réalisées par JEDEC. Les premiers micro-ordinateurs pouvant utiliser la DDR3 sont arrivés sur le marché pour la fin de 2007. La DDR3 fournit un débit deux fois plus important que la DDR2. Début 2014 c'est la technologie la plus communément utilisée dans les ordinateurs grand public pour la mémoire principale.

- DDR4 SDRAM : de l'anglais Double Data Rate fourth SDRAM. Il s'agit de la 4e génération de la technologie DDR. Les spécifications de cette nouvelle version sont réalisées par JEDEC. Les premiers micro-ordinateurs pouvant utiliser la DDR4 sont arrivés sur le marché pour la fin de 2014. La DDR4 fournit un débit deux fois plus important que la DDR3.

- DDR5 SDRAM : c'est la cinquième génération.

- XDR DRAM : de l'anglais XDimm Rambus RAM. Technologie basée sur la technologie Flexio développée par Rambus. Elle permet d'envisager des débits théoriques de 6,4 à 12,8 Gio/s en rafale.

Principes de fonctionnement

La DRAM est généralement disposée selon un réseau rectangulaire (matrice) de cellules de stockage de charge composé d’un condensateur et d’un transistor par bit de données. La figure de droite montre un exemple simple avec une matrice de cellules quatre par quatre. Certaines matrices DRAM comptent plusieurs milliers de cellules en hauteur et en largeur[2],[3].

Les longues lignes horizontales reliant chaque rangée sont appelées lignes de mots. Chaque colonne de cellules est composée de deux lignes de bits, chacune connectée à toutes les autres cellules de stockage de la colonne (l’illustration de droite n’inclut pas ce détail important). Elles sont généralement appelées lignes de bits « + » et « - ».

Un amplificateur de détection est essentiellement une paire d’inverseurs croisés entre les lignes de bits. L'entrée du premier inverseur est connectée à la ligne de bits + et sa sortie à la ligne de bits −. L’entrée du deuxième inverseur est connectée à la ligne de bits et sa sortie à la ligne de bits +. Il en résulte une rétroaction positive qui se stabilise une fois qu’une ligne de bits est à la tension la plus élevée possible et que l’autre ligne de bits est à la tension la plus basse possible.

Lecture d’un bit de données à partir d’une cellule de stockage

- Les amplificateurs de détection sont déconnectés[4].

- Les lignes de bits sont préchargées à des tensions exactement égales qui se situent entre les niveaux logiques haut et bas (par exemple, 0,5 V si les deux niveaux sont 0 et 1 V). Les lignes de bits sont physiquement symétriques pour maintenir la capacité égale, et donc à ce moment-là, leurs tensions sont égales[4].

- Le circuit de précharge est désactivé. Parce que les lignes de bits sont relativement longues, elles ont une capacité suffisante pour maintenir la tension préchargée pendant une courte période. Il s’agit d’un exemple de logique dynamique[4].

- La ligne de mots de la rangée souhaitée est ensuite pilotée vers le haut pour connecter le condensateur de stockage d’une cellule à sa ligne de bits. Cela provoque la conduction du transistor, transférant la charge de la cellule de stockage à la ligne de bits connectée (si la valeur stockée est de 1) ou de la ligne de bits connectée à la cellule de stockage (si la valeur stockée est de 0). Étant donné que la capacité de la ligne de bits est généralement beaucoup plus élevée que la capacité de la cellule de stockage, la tension sur la ligne de bits augmente très légèrement si le condensateur de la cellule de stockage est déchargé et diminue très légèrement s'il est chargé (par exemple, 0,54 et 0,45 V dans les deux cas). Comme l’autre ligne de bits reste à 0,50 V, il y a une petite différence de tension entre les deux lignes de bits torsadées[4].

- Les amplificateurs de détection sont maintenant connectés aux paires de lignes de bits. Une rétroaction positive se produit alors à partir des inverseurs croisés, amplifiant ainsi la petite différence de tension entre les lignes de bits paires et impaires d’une colonne particulière jusqu’à ce qu’une ligne de bits soit complètement à la tension la plus basse et l’autre à la tension la plus haute. Une fois que cela s’est produit, la rangée est « ouverte » (les données de cellule souhaitées sont disponibles)[4].

- Toutes les cellules de stockage de la rangée ouverte sont détectées simultanément et les sorties de l’amplificateur de détection sont verrouillées. Une adresse de colonne sélectionne ensuite le bit verrouillé à connecter au bus de données externe. Les lectures de différentes colonnes dans la même rangée peuvent être effectuées sans délai d’ouverture de rangée car, pour la rangée ouverte, toutes les données ont déjà été détectées et verrouillées[4].

- Pendant que la lecture des colonnes d'une rangée ouverte se produit, le courant remonte les lignes de bits à partir de la sortie des amplificateurs de détection et recharge les cellules de stockage. Cela renforce (c’est-à-dire « rafraîchit ») la charge dans la cellule de stockage en augmentant la tension dans le condensateur de stockage s’il était chargé au départ, ou en le maintenant déchargé s’il était vide. En raison de la longueur des lignes de bits, il y a un délai de propagation assez long pour que la charge soit retransférée au condensateur de la cellule. Cela prend beaucoup de temps après la fin de l’amplification de détection et se chevauche donc avec une ou plusieurs lectures de colonne[4].

- Une fois la lecture de toutes les colonnes de la rangée ouverte en cours effectuée, la ligne de mot est désactivée pour déconnecter les condensateurs de la cellule de stockage des lignes de bits (la rangée est « fermée »). L’amplificateur de détection est désactivé et les lignes de bits sont à nouveau préchargées[4].

Écriture dans une cellule de stockage

Pour stocker des données, une rangée est ouverte et l’amplificateur de détection d’une colonne donnée est temporairement forcé à l’état haute ou basse tension souhaité, provoquant ainsi la charge ou la décharge du condensateur de la cellule de stockage par la ligne de bits à la valeur souhaitée. En raison de la configuration à rétroaction positive de l’amplificateur de détection, il maintiendra une ligne de bits à une tension stable même après la suppression de la tension de forçage. Lors d’une écriture dans une cellule particulière, toutes les colonnes d’une rangée sont détectées simultanément, tout comme lors de la lecture, de sorte que bien que la charge du condensateur de la cellule de stockage d’une seule colonne soit modifiée, la rangée entière est rafraîchie (réécrite), comme illustré dans la figure de droite[4].

Sécurité

Attaque par démarrage à froid

Bien que les spécifications de la mémoire dynamique indiquent que la conservation des données de la mémoire n'est garantie que si la mémoire est rafraîchie régulièrement (typiquement toutes les 64 ms), les condensateurs de cellules de mémoire conservent souvent leurs charges durant des périodes significativement plus longues, en particulier à basses températures[5]. Sous certaines conditions, la plupart des données de la mémoire DRAM peuvent être récupérées même si la mémoire n'a pas été rafraîchie depuis plusieurs minutes[6].

Cette propriété peut être utilisée pour contourner certaines mesures de sécurité et récupérer des données stockées dans la mémoire et supposées avoir été détruites à la mise hors tension de l'ordinateur. Pour ce faire, il suffit de redémarrer l'ordinateur rapidement et copier le contenu de la mémoire vive[réf. nécessaire]. Alternativement, on peut refroidir les puces de mémoire et les transférer sur un autre ordinateur[réf. nécessaire]. Une telle attaque a réussi à contourner des systèmes populaires de chiffrement de disque, tels que TrueCrypt, BitLocker Drive Encryption de Microsoft, et FileVault d'Apple[5]. Ce type d'attaque contre un ordinateur est appelé une attaque par démarrage à froid.

Attaque par martèlement de mémoire

Le martèlement de mémoire est un effet secondaire imprévu dans les mémoires dynamiques à accès directe (DRAM) qui provoque une fuite de charge électrique dans des cellules de mémoire, et en conséquence provoque une interaction électrique entre ces cellules et d'autres cellules voisines.

Notes et références

Annexes

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.