Intel Quark is a line of 32-bit x86 SoCs and microcontrollers by Intel, designed for small size and low power consumption, and targeted at new markets including wearable devices. The line was introduced at Intel Developer Forum in 2013, and discontinued in January 2019.[1]

Quark processors, while slower than Atom processors, are much smaller and consume less power. They lack support for SIMD instruction sets (such as MMX and SSE)[2] and only support embedded operating systems.

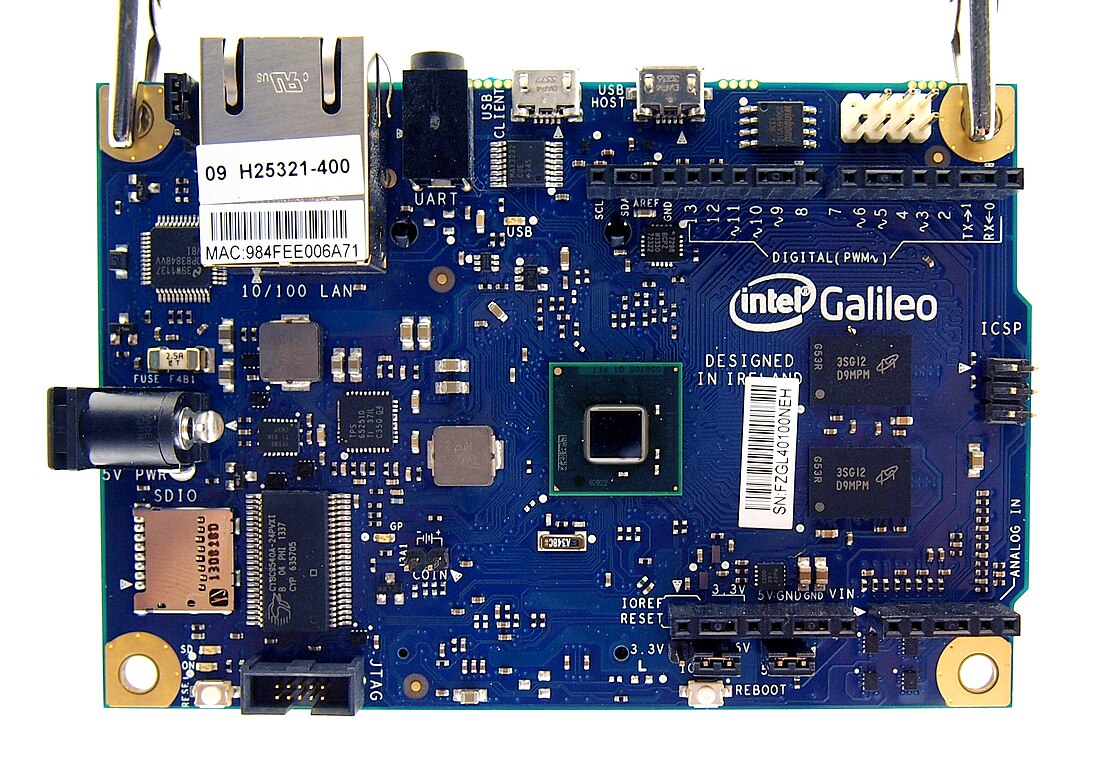

Quark powers the (now discontinued) Intel Galileo developer microcontroller board.[3] In 2016 Arduino released the Arduino 101 board that includes an Intel Quark SoC.[4][5] The CPU instruction set is, for most models, the same as a Pentium (P54C/i586) CPU.[6]

History

The first product in the Quark line is the single-core 32 nm X1000 SoC with a clock rate of up to 400 MHz. The system includes several interfaces, including PCI Express, serial UART, I²C, Fast Ethernet, USB 2.0, SDIO, power management controller, and GPIO. There are 16 kB of on-chip embedded SRAM and an integrated DDR3 memory controller.[7][8]

A second Intel product that includes Quark core, the Intel Edison microcomputer, was presented in January 2014. It has a form factor close to the size of an SD card, and is capable of wireless networking using Wi-Fi or Bluetooth.[9]

In January 2015, Intel announced the sub-miniature Intel Curie module for wearable applications, based on a Quark SE core with 80 kB SRAM and 384 kB flash.[10] At the size of a button, it also features a 6-axis accelerometer, a DSP sensor hub, a Bluetooth LE unit and a battery charge controller.

Intel announced the end-of-life of its Quark products in January 2019, with orders accepted until July 2019 and final shipments set for July 2022.[1][11]

List of processors

This section is written like a manual or guide. (September 2021) |

"Lakemont" (32 nm)

The name Lakemont has been used in reference to the processor core in multiple Quark-series processors.[12]: 4 [13]: 42

"Clanton"

Source:[14]

- All models support i586 instruction set, with x87 FPU and NX bit

- Temperature range: -40 °C to +85 °C for X10x1 models, 0 °C to +70 °C, for X10x0 models

- Secure boot supported on X102x models

- DDR3 controller with one 16-bit channel

- Two PCI-Express 2.0 controllers, with 1 lane each.

- USB Controller with two USB 2.0 Host ports and one USB 2.0 device port

- Two 10/100 MBit Ethernet controllers

- Integrated memory card reader supporting SDIO 3.0, eMMC 4.41 and SD 3.0

- Serial I/O supporting SPI, UART (serial port) and I2C

(The L2 cache column shows the size of the L1 cache.)

| Model | sSpec number |

Cores | Clock rate | GPU frequency |

L2 cache |

I/O bus | Memory | Voltage | TDP | Socket | Release date | Part number(s) |

Release price (USD) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Quark X1000 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 | 0.95–1.1 V | 2.2 W

|

|

Q4'13 |

|

$9.63 |

| Quark X1001 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 | 0.95–1.1 V | 2.2 W

|

|

Q2'14 |

|

$11.77 |

| Quark X1010 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q1'14 |

|

$10.16 |

| Quark X1011 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q2'14 |

|

$12.31 |

| Quark X1020 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q2'14 |

|

$11.45 |

| Quark X1020D |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q1'14 |

|

$10.70 |

| Quark X1021 |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q2'14 |

|

$13.39 |

| Quark X1021D |

|

1 | 400 MHz | — | 16 KB | PCIe | DDR3-800 (ECC) | 0.95–1.1 V | 2.2 W

|

|

Q2'14 |

|

$12.85 |

"Silver Butte"

- Implements only a limited subset of the 32-bit x86 instruction set (e.g. segmentation, BCD/string instructions, AF/PF flags,

XCHGare not supported)[15]

"Mint Valley"

- Supports i586 instruction set, without x87.

| Model | sSpec number |

Cores | Clock rate | GPU frequency |

L2 cache |

I/O bus | Memory | Voltage | TDP | Socket | Release date | Part number(s) |

Release price (USD) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Quark D2000 |

|

1 | 32 MHz | — | AHB-Lite,[13]: 72 APB[13]: 96 | eSRAM | 1.62–3.63 V | 0.025 W

|

|

Q3'15 | FND2000

|

$2.54 |

"Atlas Peak"

- Supports i586 instruction set, without x87.

| Model | sSpec number |

Cores | Clock rate | GPU frequency |

L2 cache |

I/O bus | Memory | Voltage | TDP | Socket | Release date | Part number(s) |

Release price (USD) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Quark SE C1000 |

|

1 | 32 MHz | — | 8 KB | AHB-Lite, APB | eSRAM | 1.8–3.3 V | 0.025 W

|

|

Q4'15 | LMCQ1000

|

$10.32 |

Segfault bug

Intel Quark SoC X1000 contains a bug (#71538)[17] that "under specific circumstances" results in a type of crash known as a segfault. The workaround implemented by Intel is to omit LOCK prefixes (not required on single-threaded processors) in the compiled code.[18] While source-based embedded systems like those built using the Yocto Project can incorporate this workaround at compile time, general purpose Linux distributions such as Debian are deeply affected by the bug. Such a workaround is not easy to implement in binaries meant to support multithreading too as they require LOCK prefixes to function properly.[19]

See also

References

External links

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.