Adder (electronics)

Digital circuit that produces sums from inputs From Wikipedia, the free encyclopedia

An adder, or summer,[1] is a digital circuit that performs addition of numbers. In many computers and other kinds of processors, adders are used in the arithmetic logic units (ALUs). They are also used in other parts of the processor, where they are used to calculate addresses, table indices, increment and decrement operators and similar operations.

Although adders can be constructed for many number representations, such as binary-coded decimal or excess-3, the most common adders operate on binary numbers. In cases where two's complement or ones' complement is being used to represent negative numbers, it is trivial to modify an adder into an adder–subtractor. Other signed number representations require more logic around the basic adder.

History

George Stibitz invented the 2-bit binary adder (the Model K) in 1937.

Binary adders

Summarize

Perspective

Half adder

The half adder adds two single binary digits and . It has two outputs, sum () and carry (). The carry signal represents an overflow into the next digit of a multi-digit addition. The value of the sum is . The simplest half-adder design, pictured on the right, incorporates an XOR gate for and an AND gate for . The Boolean logic for the sum (in this case ) will be whereas for the carry () will be . With the addition of an OR gate to combine their carry outputs, two half adders can be combined to make a full adder.[2]

The truth table for the half adder is:

| Inputs | Outputs | ||

|---|---|---|---|

| A | B | Cout | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Various half adder digital logic circuits:

- Half adder in action.

- Schematic of half adder implemented with five NAND gates.

- Schematic symbol for a 1-bit half adder.

Full adder

A full adder adds binary numbers and accounts for values carried in as well as out. A one-bit full-adder adds three one-bit numbers, often written as , , and ; and are the operands, and is a bit carried in from the previous less-significant stage.[3] The circuit produces a two-bit output. Output carry and sum are typically represented by the signals and , where the sum equals . The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. bit binary numbers.

A full adder can be implemented in many different ways such as with a custom transistor-level circuit or composed of other gates. The most common implementation is with:

The above expressions for and can be derived from using a Karnaugh map to simplify the truth table.

In this implementation, the final OR gate before the carry-out output may be replaced by an XOR gate without altering the resulting logic. This is because when A and B are both 1, the term is always 0, and hence can only be 0. Thus, the inputs to the final OR gate can never be both 1's (this is the only combination for which the OR and XOR outputs differ).

Due to the functional completeness property of the NAND and NOR gates, a full adder can also be implemented using nine NAND gates,[4] or nine NOR gates.

Using only two types of gates is convenient if the circuit is being implemented using simple integrated circuit chips which contain only one gate type per chip.

A full adder can also be constructed from two half adders by connecting and to the input of one half adder, then taking its sum-output as one of the inputs to the second half adder and as its other input, and finally the carry outputs from the two half-adders are connected to an OR gate. The sum-output from the second half adder is the final sum output () of the full adder and the output from the OR gate is the final carry output (). The critical path of a full adder runs through both XOR gates and ends at the sum bit . Assumed that an XOR gate takes 1 delays to complete, the delay imposed by the critical path of a full adder is equal to:

The critical path of a carry runs through one XOR gate in adder and through 2 gates (AND and OR) in carry-block and therefore, if AND or OR gates take 1 delay to complete, has a delay of:

The truth table for the full adder is:

| Inputs | Outputs | |||

|---|---|---|---|---|

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Inverting all inputs of a full adder also inverts all of its outputs, which can be used in the design of fast ripple-carry adders, because there is no need to invert the carry.[5]

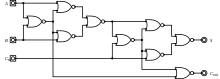

Various full adder digital logic circuits:

- Full adder in action.

- Schematic of full adder implemented with nine NAND gates.

- Schematic of full adder implemented with nine NOR gates.

- Schematic symbol for a 1-bit full adder with Cin and Cout drawn on sides of block to emphasize their use in a multi-bit adder

Adders supporting multiple bits

Ripple-carry adder

It is possible to create a logical circuit using multiple full adders to add N-bit numbers. Each full adder inputs a , which is the of the previous adder. This kind of adder is called a ripple-carry adder (RCA), since each carry bit "ripples" to the next full adder. The first (and only the first) full adder may be replaced by a half adder (under the assumption that ).

The layout of a ripple-carry adder is simple, which allows fast design time; however, the ripple-carry adder is relatively slow, since each full adder must wait for the carry bit to be calculated from the previous full adder. The gate delay can easily be calculated by inspection of the full adder circuit. Each full adder requires three levels of logic. In a 32-bit ripple-carry adder, there are 32 full adders, so the critical path (worst case) delay is 3 (from input to of first adder) + 31 × 2 (for carry propagation in latter adders) = 65 gate delays.[6] The general equation for the worst-case delay for a n-bit carry-ripple adder, accounting for both the sum and carry bits, is:

A design with alternating carry polarities and optimized AND-OR-Invert gates can be about twice as fast.[7][5]

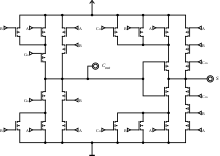

Carry-lookahead adder (Weinberger and Smith, 1958)

To reduce the computation time, Weinberger and Smith invented a faster way to add two binary numbers by using carry-lookahead adders (CLA).[8] They introduced two signals ( and ) for each bit position, based on whether a carry is propagated through from a less significant bit position (at least one input is a 1), generated in that bit position (both inputs are 1), or killed in that bit position (both inputs are 0). In most cases, is simply the sum output of a half adder and is the carry output of the same adder. After and are generated, the carries for every bit position are created.

Mere derivation of Weinberger-Smith CLA recurrence, are: Brent–Kung adder (BKA),[9] and the Kogge–Stone adder (KSA).[10][11] This was shown in Oklobdzija and Zeydel paper in IEEE Journal of Solid-State Circutis.[12]

Some other multi-bit adder architectures break the adder into blocks. It is possible to vary the length of these blocks based on the propagation delay of the circuits to optimize computation time. These block based adders include the carry-skip (or carry-bypass) adder which will determine and values for each block rather than each bit, and the carry-select adder which pre-generates the sum and carry values for either possible carry input (0 or 1) to the block, using multiplexers to select the appropriate result when the carry bit is known.

By combining multiple carry-lookahead adders, even larger adders can be created. This can be used at multiple levels to make even larger adders. For example, the following adder is a 64-bit adder that uses four 16-bit CLAs with two levels of lookahead carry units.

Other adder designs include the carry-select adder, conditional sum adder, carry-skip adder, and carry-complete adder.

Carry-save adders

If an adding circuit is to compute the sum of three or more numbers, it can be advantageous to not propagate the carry result. Instead, three-input adders are used, generating two results: a sum and a carry. The sum and the carry may be fed into two inputs of the subsequent 3-number adder without having to wait for propagation of a carry signal. After all stages of addition, however, a conventional adder (such as the ripple-carry or the lookahead) must be used to combine the final sum and carry results.

3:2 compressors

A full adder can be viewed as a 3:2 lossy compressor: it sums three one-bit inputs and returns the result as a single two-bit number; that is, it maps 8 input values to 4 output values. (the term "compressor" instead of "counter" was introduced in[13])Thus, for example, a binary input of 101 results in an output of 1 + 0 + 1 = 10 (decimal number 2). The carry-out represents bit one of the result, while the sum represents bit zero. Likewise, a half adder can be used as a 2:2 lossy compressor, compressing four possible inputs into three possible outputs.

Such compressors can be used to speed up the summation of three or more addends. If the number of addends is exactly three, the layout is known as the carry-save adder. If the number of addends is four or more, more than one layer of compressors is necessary, and there are various possible designs for the circuit: the most common are Dadda and Wallace trees. This kind of circuit is most notably used in multiplier circuits, which is why these circuits are also known as Dadda and Wallace multipliers.

Quantum adders

Using only the Toffoli and CNOT quantum logic gates, it is possible to produce quantum full- and half-adders.[14][15][16] The same circuits can also be implemented in classical reversible computation, as both CNOT and Toffoli are also classical logic gates.

Since the quantum Fourier transform has a low circuit complexity, it can efficiently be used for adding numbers as well.[17][18][19]

Analog adders

Just as in Binary adders, combining two input currents effectively adds those currents together. Within the constraints of the hardware, non-binary signals (i.e. with a base higher than 2) can be added together to calculate a sum. Also known as a "summing amplifier",[20] this technique can be used to reduce the number of transistors in an addition circuit.

See also

- Binary multiplier

- Subtractor

- Electronic mixer — for adding analog signals

References

Further reading

External links

Wikiwand - on

Seamless Wikipedia browsing. On steroids.