8bitový mikroprocesor From Wikipedia, the free encyclopedia

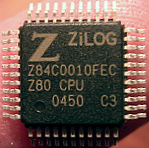

Zilog Z80 je osmibitový mikroprocesor, navržený firmou Zilog a prodávaný od července 1976. Byl široce používán jak ve stolních počítačích, tak pro armádní účely. Z80 a jeho klony tvoří jednu z nejvíce používaných CPU sérií všech dob a společně se sérií MOS Technology 6502 dominoval trhu s osmibitovými počítači od začátku 70. až do poloviny 80. let 20. století.

| Zilog Z80 | |

|---|---|

Z80 (z června 1976) | |

| Specifikace | |

| Návrh | Federico Faggin, Masatoshi Shima |

| Uvedení | březen 1976 |

| Výrobci | Zilog, Mostek, Synertek, SGS-Thomson, NEC, Sharp, Toshiba, Rohm, GoldStar (LG Group), Hitachi, National Semiconductor a další |

| Výrobní proces | 4μm |

| Frekvence | 2,5; 4; 6; 8; 10 MHz; CMOS až 20 MHz, binárně kompatibilní (od Zilogu) až 33 nebo 50 MHz |

| Šířka datové sběrnice | 8 bitů[1] |

| Šířka adresní sběrnice | 16 bitů[1] |

| Patice | 40-pin DIP |

Zilog licencoval design Z80 několika dodavatelům a mnoho východoevropských a ruských výrobců vyrábělo nelicencované kopie (U880D v počítačích Robotron). To umožnilo výrobkům menších společností prosadit se na trhu vedle větších společností, jako třeba Toshiba. V důsledku toho Zilog, od uvedení procesoru na trh, vyrobil méně než polovinu procesorů Z80. V posledních desetiletích se Zilog soustředí na stále rostoucí trh s vestavěnými systémy (pro který jsou učeny původní Z80 a Z180) a na nejnovější z rodiny mikrokontrolérů, Z80-kompatibilní.

Ačkoli už dříve Zilog uskutečnil pokusy s pokročilými mikropočítači, než byly architektury Z80 (Z800 a Z280), tyto čipy se nikdy neuchytily. Společnost se také snažila proniknout na trh s pracovními stanicemi se svým procesorem Z8000 a 32bitovým Z80000 (ani jeden nesouvisí s 8bitovým procesorem Z80).

Společnost Sharp vyrobila funkční skleněnou variantu procesoru Z80.[2]

Z80 se objevil, když Federico Faggin po práci na procesoru Intel 8080 opustil společnost Intel a na konci roku 1974 vstoupil do firmy Zilog. Společně s Ralphem Ungermanem (1942–2015) uvedli v červenci 1976 procesor Z80 na trh. Byl navržen, aby byl zpětně kompatibilní s procesorem Intel 8080, takže operační systém CP/M mohl fungovat bez jakýchkoli dalších úprav. K vývoji procesoru Z80 přispěl také další z návrhářů procesorů Intel 4004 a 8080, Masatoshi Shima.

Patrně nejslavnější použití a boom přinesla procesoru řada domácích počítačů Sinclair ZX81 a Sinclair ZX Spectrum. Později ho firma SEGA nasadila v herních konzolích Master System a Game Gear. Firma Nintendo použila v konzolích Game Boy a Game Boy Color klon procesoru Z80 od firmy Sharp. Procesor Z80 byl také použit v japonském domácím počítači Sord M5. Mezi další počítače, ve kterých byl použit, patří TRS-80 (modely 1–4), Commodore 128D, Franklin Ace 1200, Osborne 1, KayPro I a KayPro II.[3][p 1] V herních automatech a konzolích Neo Geo je využitý jako koprocesor řídící zvukový systém.[4] V Československu byly na základě Z80 vyráběny počítače Ondra a Didaktik, nebo také slušovické TNS-SC, TNS-GC a TNS-HC.

V současnosti je Z80 stále používán např. ve vestavěných systémech, mikrokontrolérech nebo v elektronice (například programovatelné kalkulátory, tiskárny, syntezátory či MP3 přehrávače atd.). Je také využíván pro různé domácí a školní projekty a výukové pomůcky.[5][6][7]

Z80 nabízí mnoho skutečných vylepšení oproti 8080:

Z80 vystřídal procesor 8080 a jeho nástupce 8085, na trhu s procesory a stal se jedním z nejpopulárnějších 8bitových CPU. Možná, že klíčem, který zapříčinil úspěch procesoru Z80, byl zabudovaný DRAM refresh a ostatní funkce, které dovolovaly systému aby byl postaven s menším počtem podpůrných čipů (později, většinu Z80 systémů představovaly vestavěné systémy, které typicky používaly statickou RAM, a proto nepotřebovaly tento refresh).

Podle originálního designu NMOS se určená horní hranice frekvence postupně zvyšuje z původních 2,5 MHz, přes dobře známé 4 MHz (Z80A), až na 6 MHz (Z80B) a 8 MHz (Z80H). CMOS verze byla také vyvinuta se stanovenými limity frekvencí v rozsahu od 4 MHz až do 20 MHz pro verzi, která se prodává dnes. CMOS verze také umožňovala spánek s nízkou spotřebou se zachováním vnitřních stavů (nemá žádnou dolní hraniční frekvenci). Plně kompatibilní s deriváty HD64180/Z180 a eZ80, ty jsou v současné době určené až pro 33 MHz a 50 MHz.

Procesor umožňuje adresovat 64 KiB paměti, která může být libovolného typu, RAM i ROM. Pokud je vyžadováno více dostupné paměti, než 64 KiB, je nutné použít techniku stránkování paměti, která je použita mimo jiné u počítačů Sinclair ZX Spectrum 128, Didaktik Gama, či v herních automatech a konzolích Neo Geo.[8][9] K dispozici je oficiálně 256 vstupně/výstupních portů (8bitové adresování), chování procesoru umožňuje adresovat až 65536 portů (16bitové adresování), při adresování 65536 portů ale nelze použít instrukce blokových vstupně/výstupních operací, protože registr B umožňující 16bitové adresování je u těchto instrukcí využit jako čítač přenesených bajtů.[10]

Toshiba, jakožto licencovaný výrobce, integrovala některé periferní obvody z rodiny procesoru Z80 do společného pouzdra s vlastním procesorem, tyto kombinované procesory později převzal Zilog do svého výrobního programu také.[11]

Programovací model a sada registrů jsou konvenční a díky odvození ze stejného předchůdce (Intel 8080) se podobají rodině x86. Procesor Z80 má zdvojenou sadu hlavních registrů, což spolu s rychlými instrukcemi pro přepínání obou sad umožňuje rychle reagovat na jednoúrovňové přerušení s vysokou prioritou. Tato vlastnost byla představena v Datapoint 2200, ale v procesoru 8008 nebyla Intelem implementována. Tato vlastnost usnadňuje použití Z80 ve vestavěných systémech, pro které byla většina prvních mikroprocesorů určena spíše než pro použití v osobních počítačích. Podle jednoho z designérů, Masatoshi Shima, se trh zaměřil na vysoce výkonné tiskárny, pokladny a inteligentní terminály. Zdvojená sada registrů však byla také využívána pro vysoce optimalizované, ručně kódované programy. Některý software, hlavně hry pro MSX, Sinclair ZX Spectrum a další počítače založené na Z80, které používaly kód optimalizovaný na extrémní úroveň, využívaly mimo jiné i zdvojenou sadu registrů.

Registry

| Registry mikroprocesoru Z80 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Stejně jako v procesoru 8080, 8bitové registry jsou většinou spojeny, aby poskytovaly 16bitovou verzi. Kompatibilní registry procesoru 8080 jsou:

Nové registry zavedené v Z80 jsou:

Alternativní registry nejsou přímo přístupné, místo toho jsou použity dvě speciální instrukce, EX AF, AF' a EXX, které pouze přepínají klopný obvod vybírající registr A a příznaky nebo zbytek (registry BC, DE a HL) sady registrů. To umožňuje rychlé prohození kontextu pro obsluhu přerušení: instrukce EX AF, AF´ může být použita samostatně (pro opravdu jednoduché a rychlé přerušení) nebo spolu s EXX aby se vyměnila celá sada AF, BC, DE, HL. Tento postup je mnohonásobně rychlejší, než uložení registrů na zásobník (které lze používat pro pomalejší obsluhu víceúrovňových přerušení s nižší prioritou).

Refresh registr, R, se zvyšuje pokaždé, když CPU vykoná opcode (operační kód) nebo opcode prefix a proto nemá žádný přímý vztah s vykonáváním programu. Proto se někdy používá pro generování pseudonáhodných čísel ve hrách a také ve schématech ochrany softwaru. V některých návrzích je také použit jako „hardwarový“ čítač, slavný příklad toho je ZX81, který umožňuje sledovat pozici písmene na televizní obrazovce tím, že generuje přerušení při přetočení čítače (propojením A6 na vstup INT).

Registr I je určený pro vyšší byte adresy tabulky obsluh přerušení ve speciálním režimu přerušení číslo 2 (do něhož se přepíná instrukcí IM 2). Nižší byte adresy dodá zařízení v cyklu potvrzení přerušení. Tento režim umožňuje používat až 128 obslužných rutin přerušení, přičemž priorita může být určena pořadím zapojení zařízení v řetězci. I tento registr se někdy používá velmi kreativně; v režimech přerušení 0 a 1 může být použit jednoduše jako další 8bitový datový registr.

První jazyk symbolických adres (dále jen assembler) pro Intel 8008 byl založen na velmi jednoduché (ale systematické) syntaxi, zděděné od Datapointu 2200. Pro původní čip Intel 8008 byla později tato originální syntaxe změněna na novou, poněkud tradičnější formu assembleru. V tu samou dobu byl assembler rozšířen, aby se přizpůsobil přidání nových adresních možností ve více pokročilém čipu Intel 8080 (Intel 8008 a 8080 sdílely jazykovou podskupinu bez toho aby byly binárně kompatibilní, nicméně, Intel 8008 byl binárně kompatibilní s Datapointem 2200).

V tomto procesu, symbolický název (neboli mnemonická zkratka) L, pro LOAD, byla nahrazena různými zkratkami slov LOAD, STORE a MOVE, a ty byly smíchány s ostatními symbolickými písmeny. Symbolický název písmene M, pro paměť, byl odstraněn ze symbolických instrukcí, aby se stal syntakticky samostatným operandem, zatímco registry a kombinace registrů byly velmi rozporuplně označeny. Buď zkrácením operandu (MVI D, LXI H a podobně) nebo v rámci vlastních symbolických instrukcí (LDA, LHLD a podobně) nebo obojím najednou (LDAX B, STAX D a podobně).

| Datapoint 2200 a i8008 | i8080 | Z80 | i8086/i8088 |

|---|---|---|---|

| před rokem 1973 | ~1974 | 1976 | 1978 |

LBC |

MOV B,C |

LD B,C |

MOV BL,CL |

-- |

LDAX B |

LD A,(BC) |

MOV AL,[BX] |

LAM |

MOV A,M |

LD A,(HL) |

MOV AL,[BP] |

LBM |

MOV B,M |

LD B,(HL) |

MOV BL,[BP] |

-- |

STAX D |

LD (DE),A |

-- |

LMA |

MOV M,A |

LD (HL),A |

MOV [BP],AL |

LMC |

MOV M,C |

LD (HL),C |

MOV [BP],CL |

LDI 56 |

MVI D,56 |

LD D,56 |

MOV DL,56 |

LMI 56 |

MVI M,56 |

LD (HL),56 |

MOV byte ptr [BP],56 |

-- |

LDA 1234 |

LD A,(1234) |

MOV AL,[1234] |

-- |

STA 1234 |

LD (1234),A |

MOV [1234],AL |

-- |

-- |

LD B,(IX+56) |

MOV BL,[SI+56] |

-- |

-- |

LD (IX+56),C |

MOV [SI+56],CL |

-- |

-- |

LD (IY+56),78 |

MOV byte ptr [DI+56],78 |

-- |

LXI B,1234 |

LD BC,1234 |

MOV BX,1234 |

-- |

LXI H,1234 |

LD HL,1234 |

MOV BP,1234 |

-- |

SHLD 1234 |

LD (1234),HL |

MOV [1234],BP |

-- |

LHLD 1234 |

LD HL,(1234) |

MOV BP,[1234] |

-- |

-- |

LD BC,(1234) |

MOV BX,[1234] |

-- |

-- |

LD IX,(1234) |

MOV SI,[1234] |

Ukázka čtyř syntaxí, používajících vzorky ekvivalentní nebo (pro 8086) velmi podobné LOAD a STORE instrukcím.

Protože Intel prohlašoval, že vlastní práva na symbolické názvy, musela být v assembleru vyvinuta nová syntaxe. Tentokrát byl použit mnohem systematičtější přístup:

Tyto zásady umožňovaly přímočaře zjistit jména a tvary všech instrukcí procesoru Z80. Naopak je ale nutné, aby si uživatel pamatoval omezení některých instrukcí, kdy například instrukce LD umožňuje osmibitový přenos mezi libovolnými dvěma registry,[p 2] zatímco šestnáctibitový přenos je možný pouze mezi některými dvojicemi a tak třeba instrukce LD BC,HL neexistuje.[12]

S výjimkou pojmenování rozdílů, a navzdory určitému rozporu v základní registrové struktuře, syntaxe Z80 a 8086 je v podstatě izomorfní pro velkou část instrukcí. V assembleru pro 8080 a 8086 existují pouze docela nedůležité podobnosti (jako například slovo MOV, nebo písmeno X pro rozšířené registry). Programy pro procesor 8080 mohou být přeloženy do strojového kódu pro procesor 8086 pomocí speciálního assembleru nebo přeloženy do jazyka symbolických adres pomocí překladatelského programu.

Procesor Z80 používá 252 z 256 možných kódů jednotlivých bajtů opcodu (operační kód – "kořenové instrukce"). Čtyři zbývající kódy jsou značně používané jako opcode prefix. CB a ED povolí speciální instrukce a DD nebo FD vyberou IX+d nebo IY+d příslušně (v některých případech bez posunutí "d") v místě HL. Toto schéma dává procesoru Z80 velké množství permutací instrukcí a registrů. Zilog je kategorizuje do 158 různých instrukčních typů, 78 z nich jsou ty samé jako u procesoru Intel 8080 (umožňují provoz programů z procesoru 8080 na procesoru Z80). Dokumentace k Z80 dělí skupiny instrukcí do následujících kategorií:

V originálním procesoru Z80 nejsou dostupné několikanásobné instrukce. Rozdílné velikosti a varianty sčítání, posunu a rotace mají někdy rozdílné účinky na příznaky, a to proto, že z procesoru 8080 byly zkopírovány příznaky ovlivňující vlastnosti. Instrukce LOAD neovlivňuje příznaky (s výjimkou LOAD registru I a R, které jsou pro zvláštní účely). Instrukce index registru jsou užitečné pro snížení délky kódu a zatímco některé nejsou o mnoho rychlejší než ekvivalentní sekvence jednodušších operací, nepřímo šetří čas pro vykonání instrukce tím, že snižuje potřebu uložit a obnovit registry. O deset let mladší design Z180 si mohl ze začátku dovolit více "čipového prostoru", který umožňuje o něco účinnější implementaci (mimo jiné používá širší ALU). Podobné věci mohou být řečeny o Z800, Z280 a Z380. Nicméně až roku 2001, když byl vydán procesor eZ80 umožňující plné zřetězení instrukcí (neboli Pipelining), se jim tyto instrukce konečně přiblížily svou efektivitou v cyklech jak jen to bylo technicky možné, to jest vzhledem ke kódování v Z80 kombinovaném se schopností realizovat 8bitové čtení nebo zápis v každém hodinovém cyklu. Stejně tak instrukce pro 16bitové sčítání nejsou v originálním procesoru Z80 příliš rychlé (11 hodinových cyklů). Nicméně, jsou asi dvakrát rychlejší, než když se vykonávají ty samé výpočty pomocí 8bitových operací. A stejně tak důležité je, že snižují množství operací s registry.

Některé instrukce vyžadují, aby byly následovány číselnými operandy. Typ vyžadovaného operandu je označen následujícím způsobem:

Některé instrukce se z konstrukčních důvodů nacházejí v instrukční sadě několikrát, např. instrukce ld hl,(NN) a ld (NN),hl, a jejich jednotlivé varianty se liší způsobem interní realizace a dobou jejich vykonání.[13] Ze stejných důvodů se v instrukční sadě nacházejí také instrukce, které nedělají žádnou smysluplnou akci, např. instrukce ld a,a.[14] Počítač Sprinter využívá ve svém hardwaru těchto "nic nedělajících" instrukcí k ovládání hardwarového akcelerátoru.[15]

| desítkově | šestnáctkově | základní instrukce | instrukce po prefixu CB | instrukce po prefixu ED |

|---|---|---|---|---|

| 0 | 00 | nop | rlc b | |

| 1 | 01 | ld bc,NN | rlc c | |

| 2 | 02 | ld (bc),a | rlc d | |

| 3 | 03 | inc bc | rlc e | |

| 4 | 04 | inc b | rlc h | |

| 5 | 05 | dec b | rlc l | |

| 6 | 06 | ld b,N | rlc (hl) | |

| 7 | 07 | rlca | rlc a | |

| 8 | 08 | ex af,af' | rrc b | |

| 9 | 09 | add hl,bc | rrc c | |

| 10 | 0A | ld a,(bc) | rrc d | |

| 11 | 0B | dec bc | rrc e | |

| 12 | 0C | inc c | rrc h | |

| 13 | 0D | dec c | rrc l | |

| 14 | 0E | ld c,N | rrc (hl) | |

| 15 | 0F | rrca | rrc a | |

| 16 | 10 | djnz ±N | rl b | |

| 17 | 11 | ld de,NN | rl c | |

| 18 | 12 | ld (de),a | rl d | |

| 19 | 13 | inc de | rl e | |

| 20 | 14 | inc d | rl h | |

| 21 | 15 | dec d | rl l | |

| 22 | 16 | ld d,N | rl (hl) | |

| 23 | 17 | rla | rl a | |

| 24 | 18 | jr ±N | rr b | |

| 25 | 19 | add hl,de | rr c | |

| 26 | 1A | ld a,(de) | rr d | |

| 27 | 1B | dec de | rr e | |

| 28 | 1C | inc e | rr h | |

| 29 | 1D | dec e | rr l | |

| 30 | 1E | ld e,N | rr (hl) | |

| 31 | 1F | rra | rr a | |

| 32 | 20 | jr nz,±N | sla b | |

| 33 | 21 | ld hl,NN | sla c | |

| 34 | 22 | ld (NN),hl | sla d | |

| 35 | 23 | inc hl | sla e | |

| 36 | 24 | inc h | sla h | |

| 37 | 25 | dec h | sla l | |

| 38 | 26 | ld h,N | sla (hl) | |

| 39 | 27 | daa[p 3] | sla a | |

| 40 | 28 | jr z,±N | sra b | |

| 41 | 29 | add hl,hl | sra c | |

| 42 | 2A | ld hl,(NN) | sra d | |

| 43 | 2B | dec hl | sra e | |

| 44 | 2C | inc l | sra h | |

| 45 | 2D | dec l | sra l | |

| 46 | 2E | ld l,N | sra (hl) | |

| 47 | 2F | cpl | sra a | |

| 48 | 30 | jr nc,±N | slia b[p 4] | |

| 49 | 31 | ld sp,NN | slia c[p 4] | |

| 50 | 32 | ld (NN),a | slia d[p 4] | |

| 51 | 33 | inc sp | slia e[p 4] | |

| 52 | 34 | inc (hl) | slia h[p 4] | |

| 53 | 35 | dec (hl) | slia l[p 4] | |

| 54 | 36 | ld (hl),N | slia (hl)[p 4] | |

| 55 | 37 | scf | slia a[p 4] | |

| 56 | 38 | jr c,±N | srl b | |

| 57 | 39 | add hl,sp | srl c | |

| 58 | 3A | ld a,(NN) | srl d | |

| 59 | 3B | dec sp | srl e | |

| 60 | 3C | inc a | srl h | |

| 61 | 3D | dec a | srl l | |

| 62 | 3E | ld a,N | srl (hl) | |

| 63 | 3F | ccf | srl a | |

| 64 | 40 | ld b,b | bit 0,b | in b,(c) |

| 65 | 41 | ld b,c | bit 0,c | out (c),b |

| 66 | 42 | ld b,d | bit 0,d | sbc hl,bc |

| 67 | 43 | ld b,e | bit 0,e | ld (NN),bc |

| 68 | 44 | ld b,h | bit 0,h | neg |

| 69 | 45 | ld b,l | bit 0,l | retn |

| 70 | 46 | ld b,(hl) | bit 0,(hl) | im 0 |

| 71 | 47 | ld b,a | bit 0,a | ld i,a |

| 72 | 48 | ld c,b | bit 1,b | in c,(c) |

| 73 | 49 | ld c,c | bit 1,c | out (c),c |

| 74 | 4A | ld c,d | bit 1,d | adc hl,bc |

| 75 | 4B | ld c,e | bit 1,e | ld bc,(NN) |

| 76 | 4C | ld c,h | bit 1,h | neg[p 5] |

| 77 | 4D | ld c,l | bit 1,l | reti |

| 78 | 4E | ld c,(hl) | bit 1,(hl) | im 0/1[p 5] |

| 79 | 4F | ld c,a | bit 1,a | ld r,a |

| 80 | 50 | ld d,b | bit 2,b | in d,(c) |

| 81 | 51 | ld d,c | bit 2,c | out (c),d |

| 82 | 52 | ld d,d | bit 2,d | sbc hl,de |

| 83 | 53 | ld d,e | bit 2,e | ld (NN),de |

| 84 | 54 | ld d,h | bit 2,h | neg[p 5] |

| 85 | 55 | ld d,l | bit 2,l | retn[p 5] |

| 86 | 56 | ld d,(hl) | bit 2,(hl) | im 1 |

| 87 | 57 | ld d,a | bit 2,a | ld a,i |

| 88 | 58 | ld e,b | bit 3,b | in e,(c) |

| 89 | 59 | ld e,c | bit 3,c | out (c),e |

| 90 | 5A | ld e,d | bit 3,d | adc hl,de |

| 91 | 5B | ld e,e | bit 3,e | ld de,(NN) |

| 92 | 5C | ld e,h | bit 3,h | neg[p 5] |

| 93 | 5D | ld e,l | bit 3,l | retn[p 5] |

| 94 | 5E | ld e,(hl) | bit 3,(hl) | im 2 |

| 95 | 5F | ld e,a | bit 3,a | ld a,r |

| 96 | 60 | ld h,b | bit 4,b | in h,(c) |

| 97 | 61 | ld h,c | bit 4,c | out (c),h |

| 98 | 62 | ld h,d | bit 4,d | sbc hl,hl |

| 99 | 63 | ld h,e | bit 4,e | ld (NN),hl |

| 100 | 64 | ld h,h | bit 4,h | neg[p 5] |

| 101 | 65 | ld h,l | bit 4,l | retn[p 5] |

| 102 | 66 | ld h,(hl) | bit 4,(hl) | im 0[p 5] |

| 103 | 67 | ld h,a | bit 4,a | rrd |

| 104 | 68 | ld l,b | bit 5,b | in l,(c) |

| 105 | 69 | ld l,c | bit 5,c | out (c),l |

| 106 | 6A | ld l,d | bit 5,d | adc hl,hl |

| 107 | 6B | ld l,e | bit 5,e | ld hl,(NN) |

| 108 | 6C | ld l,h | bit 5,h | neg[p 5] |

| 109 | 6D | ld l,l | bit 5,l | retn[p 5] |

| 110 | 6E | ld l,(hl) | bit 5,(hl) | im 0/1[p 5] |

| 111 | 6F | ld l,a | bit 5,a | rld |

| 112 | 70 | ld (hl),b | bit 6,b | in (c)[p 6] |

| 113 | 71 | ld (hl),c | bit 6,c | out (c),0[p 5] |

| 114 | 72 | ld (hl),d | bit 6,d | sbc hl,sp |

| 115 | 73 | ld (hl),e | bit 6,e | ld (NN),sp |

| 116 | 74 | ld (hl),h | bit 6,h | neg[p 5] |

| 117 | 75 | ld (hl),l | bit 6,l | retn[p 5] |

| 118 | 76 | halt | bit 6,(hl) | im 1[p 5] |

| 119 | 77 | ld (hl),a | bit 6,a | nop[p 5] |

| 120 | 78 | ld a,b | bit 7,b | in a,(c) |

| 121 | 79 | ld a,c | bit 7,c | out (c),a |

| 122 | 7A | ld a,d | bit 7,d | adc hl,sp |

| 123 | 7B | ld a,e | bit 7,e | ld sp,(NN) |

| 124 | 7C | ld a,h | bit 7,h | neg[p 5] |

| 125 | 7D | ld a,l | bit 7,l | retn[p 5] |

| 126 | 7E | ld a,(hl) | bit 7,(hl) | im 2[p 5] |

| 127 | 7F | ld a,a | bit 7,a | nop[p 5] |

| 128 | 80 | add a,b | res 0,b | |

| 129 | 81 | add a,c | res 0,c | |

| 130 | 82 | add a,d | res 0,d | |

| 131 | 83 | add a,e | res 0,e | |

| 132 | 84 | add a,h | res 0,h | |

| 133 | 85 | add a,l | res 0,l | |

| 134 | 86 | add a,(hl) | res 0,(hl) | |

| 135 | 87 | add a,a | res 0,a | |

| 136 | 88 | adc a,b | res 1,b | |

| 137 | 89 | adc a,c | res 1,c | |

| 138 | 8A | adc a,d | res 1,d | |

| 139 | 8B | adc a,e | res 1,e | |

| 140 | 8C | adc a,h | res 1,h | |

| 141 | 8D | adc a,l | res 1,l | |

| 142 | 8E | adc a,(hl) | res 1,(hl) | |

| 143 | 8F | adc a,a | res 1,a | |

| 144 | 90 | sub b | res 2,b | |

| 145 | 91 | sub c | res 2,c | |

| 146 | 92 | sub d | res 2,d | |

| 147 | 93 | sub e | res 2,e | |

| 148 | 94 | sub h | res 2,h | |

| 149 | 95 | sub l | res 2,l | |

| 150 | 96 | sub (hl) | res 2,(hl) | |

| 151 | 97 | sub a | res 2,a | |

| 152 | 98 | sbc a,b | res 3,b | |

| 153 | 99 | sbc a,c | res 3,c | |

| 154 | 9A | sbc a,d | res 3,d | |

| 155 | 9B | sbc a,e | res 3,e | |

| 156 | 9C | sbc a,h | res 3,h | |

| 157 | 9D | sbc a,l | res 3,l | |

| 158 | 9E | sbc a,(hl) | res 3,(hl) | |

| 159 | 9F | sbc a,a | res 3,a | |

| 160 | A0 | and b | res 4,b | ldi |

| 161 | A1 | and c | res 4,c | cpi |

| 162 | A2 | and d | res 4,d | ini |

| 163 | A3 | and e | res 4,e | outi |

| 164 | A4 | and h | res 4,h | |

| 165 | A5 | and l | res 4,l | |

| 166 | A6 | and (hl) | res 4,(hl) | |

| 167 | A7 | and a | res 4,a | |

| 168 | A8 | xor b | res 5,b | ldd |

| 169 | A9 | xor c | res 5,c | cpd |

| 170 | AA | xor d | res 5,d | ind |

| 171 | AB | xor e | res 5,e | outd |

| 172 | AC | xor h | res 5,h | |

| 173 | AD | xor l | res 5,l | |

| 174 | AE | xor (hl) | res 5,(hl) | |

| 175 | AF | xor a | res 5,a | |

| 176 | B0 | or b | res 6,b | ldir |

| 177 | B1 | or c | res 6,c | cpir |

| 178 | B2 | or d | res 6,d | inir |

| 179 | B3 | or e | res 6,e | otir |

| 180 | B4 | or h | res 6,h | |

| 181 | B5 | or l | res 6,l | |

| 182 | B6 | or (hl) | res 6,(hl) | |

| 183 | B7 | or a | res 6,a | |

| 184 | B8 | cp b | res 7,b | lddr |

| 185 | B9 | cp c | res 7,c | cpdr |

| 186 | BA | cp d | res 7,d | indr |

| 187 | BB | cp e | res 7,e | otdr |

| 188 | BC | cp h | res 7,h | |

| 189 | BD | cp l | res 7,l | |

| 190 | BE | cp (hl) | res 7,(hl) | |

| 191 | BF | cp a | res 7,a | |

| 192 | C0 | ret nz | set 0,b | |

| 193 | C1 | pop bc | set 0,c | |

| 194 | C2 | jp nz,NN | set 0,d | |

| 195 | C3 | jp NN | set 0,e | |

| 196 | C4 | call nz,NN | set 0,h | |

| 197 | C5 | push bc | set 0,l | |

| 198 | C6 | add a,N | set 0,(hl) | |

| 199 | C7 | rst 0 | set 0,a | |

| 200 | C8 | ret z | set 1,b | |

| 201 | C9 | ret | set 1,c | |

| 202 | CA | jp z,NN | set 1,d | |

| 203 | CB | PREFIX CB | set 1,e | |

| 204 | CC | call z,NN | set 1,h | |

| 205 | CD | call NN | set 1,l | |

| 206 | CE | adc a,N | set 1,(hl) | |

| 207 | CF | rst 8 | set 1,a | |

| 208 | D0 | ret nc | set 2,b | |

| 209 | D1 | pop de | set 2,c | |

| 210 | D2 | jp nc,NN | set 2,d | |

| 211 | D3 | out (N),a | set 2,e | |

| 212 | D4 | call nc,NN | set 2,h | |

| 213 | D5 | push de | set 2,l | |

| 214 | D6 | sub N | set 2,(hl) | |

| 215 | D7 | rst 16 | set 2,a | |

| 216 | D8 | ret c | set 3,b | |

| 217 | D9 | exx | set 3,c | |

| 218 | DA | jp c,NN | set 3,d | |

| 219 | DB | in a,(N) | set 3,e | |

| 220 | DC | call c,NN | set 3,h | |

| 221 | DD | PREFIX IX | set 3,l | |

| 222 | DE | sbc a,N | set 3,(hl) | |

| 223 | DF | rst 24 | set 3,a | |

| 224 | E0 | ret po | set 4,b | |

| 225 | E1 | pop hl | set 4,c | |

| 226 | E2 | jp po,NN | set 4,d | |

| 227 | E3 | ex (sp),hl | set 4,e | |

| 228 | E4 | call po,NN | set 4,h | |

| 229 | E5 | push hl | set 4,l | |

| 230 | E6 | and N | set 4,(hl) | |

| 231 | E7 | rst 32 | set 4,a | |

| 232 | E8 | ret pe | set 5,b | |

| 233 | E9 | jp (hl) | set 5,c | |

| 234 | EA | jp pe,NN | set 5,d | |

| 235 | EB | ex de,hl | set 5,e | |

| 236 | EC | call pe,NN | set 5,h | |

| 237 | ED | PREFIX ED | set 5,l | |

| 238 | EE | xor N | set 5,(hl) | |

| 239 | EF | rst 40 | set 5,a | |

| 240 | F0 | ret p | set 6,b | |

| 241 | F1 | pop af | set 6,c | |

| 242 | F2 | jp p,NN | set 6,d | |

| 243 | F3 | di | set 6,e | |

| 244 | F4 | call p,NN | set 6,h | |

| 245 | F5 | push af | set 6,l | |

| 246 | F6 | or N | set 6,(hl) | |

| 247 | F7 | rst 48 | set 6,a | |

| 248 | F8 | ret m | set 7,b | |

| 249 | F9 | ld sp,hl | set 7,c | |

| 250 | FA | jp m,NN | set 7,d | |

| 251 | FB | ei | set 7,e | |

| 252 | FC | call m,NN | set 7,h | |

| 253 | FD | PREFIX IY | set 7,l | |

| 254 | FE | cp N | set 7,(hl) | |

| 255 | FF | rst 56 | set 7,a |

Instrukce s prefixem ED v rozsazích 00-3F A 80-FF šestnáctkově s výjimkou instrukcí pro blokové přenosy nedělají žádnou akci, pouze trvají 8 T-cyklů a zvyšují hodnotu registru R o 2.[17] V instrukčním souboru se nenacházejí instrukce pro násobení. Instrukce pro násobení mlt obsahuje až procesor Z180.[18]

Protože procesor Z80 je použit v mnoha typech počítačů, pro každý typ existuje kompilátor. Pro počítače Sinclair ZX Spectrum existují kompilátor Gens a Prometheus. Pro operační systém Linux a pro DOS existuje kompilátor Z80-ASM, který kromě podpory samotného procesoru s 64 KiB paměti podporuje i obvod Z80 CTC, rozšířené stránkování paměti a prioritní systém přerušení procesoru Z80.[19] Existuje také online vývojové prostředí a kompilátor ORG.[20]

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.